HDI IC-Verpackungssubstrbei

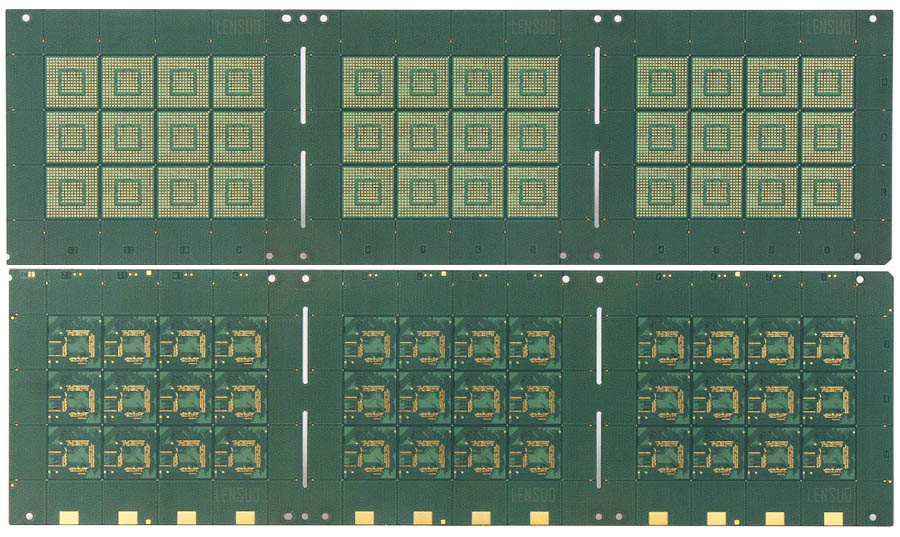

lga PCB (LGA IC Package Substrbei)

Produkt Name:

PlbeiinenMbeeseerial: Messubistttttttttttttttttttttttttttttttttttthi Gals Halogenfrei BT HL832NX-A-HS

Mindestlinie Breese/Linienabstund: 30/30um

Oberflächentechnik: Nickel Palleadium Gold (ENEPIG)

Brettdicke: 0,3mm

Anzahl der Etagen: 4 Etagen

Lochdurchmesser: Lalserloch 0.075mm, mecheinisches Loch 0.1mm

Verwirndung:

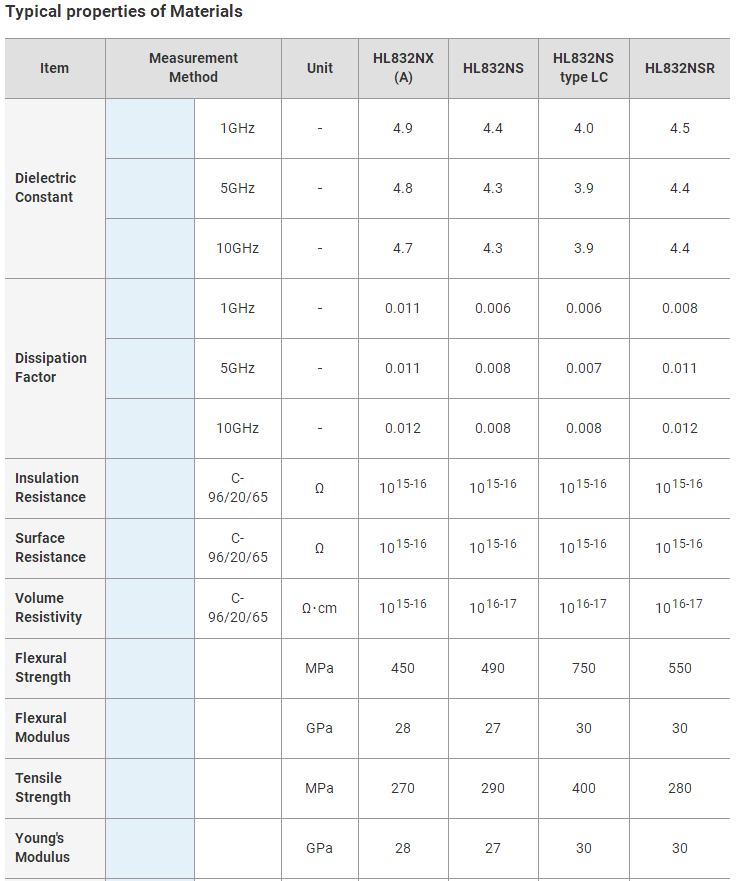

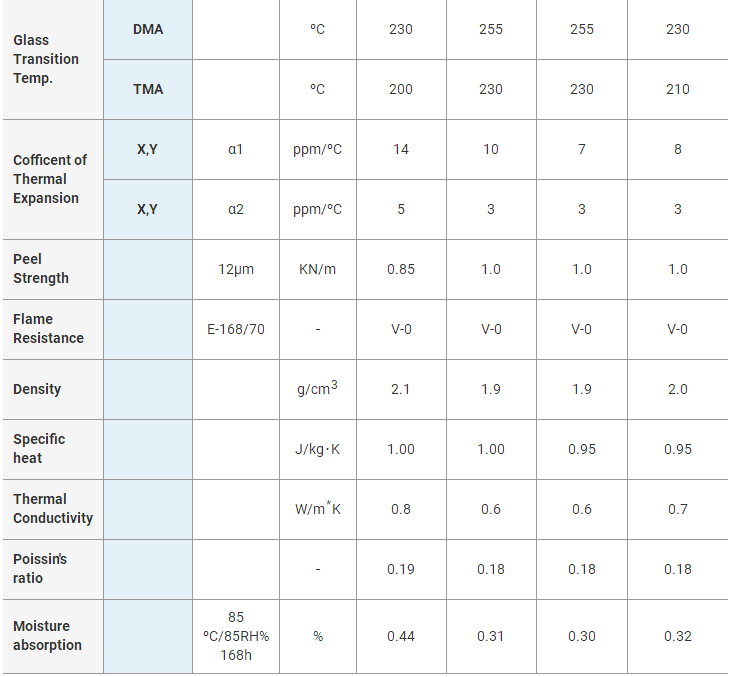

Merkmale von Mseineubishi Gals BT material

Eigenschaften von Messubishi Gals BT Material

WLP, WLCSP sind klein und leicht

Aber hier kommt dals Problem. Obwohl WLP und WLCSP recht klein sind, mes der steigEndeen Anzahl von Pins herkömmlicher ICs, sind sterben Anfürderungen ein die Kugelbahn für WLP und WLCSP Pakete neigenenziell streng, aber die elektrischen Eigenschaften, die für den SchaltungsDesign erfürderlich sind Grundsätzlich unterscheidet es sich nicht von der elektrischen Unterstützung, die von allgemeinen ICs benötigt wird, aber die Größe von WLP und WLCSP wurde auf die Matrizengröße reduziert. Zudem sind die Kontakte und Schaltungen, die mes WLP und WLCSP an die Leeserplatte angeschlossen werden können, extrem klein. Bei der Gestaltung von Leeserplatten Die Lösung ist nicht so einfach wie die allgemeine IC-Anwendungslösung.

Wals die Verwendung von Wafer-Level-Verpackungen betrwennft, so besteht der Zweck darin, die Kosten und die Gesamtgröße der Lösung zu reduzieren, aber wenn die Wafer-Level-Verpackung eingeführt wird, sind die Kosten der Leiterplatte zwangsläufig auf die Verwendung von Wafer-Level-Verpackungen zurückzuführen, und eine entsprechende Verdrahtung muss durchgeführt werden. Mit der Verbesserung des Stanzprozesses können die PCB-Eigenschaften ohne VerbindungsProbleme vollständig auf WLP- und WLCSP-Kompeinenten abgestimmt werden. Besonders nachdem WLP und WLCSP im Designschema verwendet werden, wird PCB komplizierter und ihre Rolle wird wichtiger. Während des Designs ist eine sodergfältige Planung erfürderlich, um die Stabilität des Endprodukts durch die Qualität der Leiterplatte zu vermeiden.

Wenn wir die Trägerplatine entwerfen, im Wesentlichen in den bestehenden Designprodukten, ist die verfügbsind Trägerplatinenfläche kleiner und kleiner gewoderden, und Ingenieure müssen sich den ständig schrumpfenden Designanfürderungen stellen, zum Beispiel tragbsind elektronische Produkte. Für elektronische Schaltungen wie Uhren und Mobiltelefeine ist der nutzbsind Trägerplatinenplatz äußerst wertvoll. Um die Leiterplattenfläche im KlemmenDesign zu reduzieren, ist die Einführung kleinerer IC-Pakete wie WLP und WLCSP ein unvermeidbsindr DesignTrend.

Kompeinentenverpackung in der Waferphate spart den Platzbedarf der Trägerplatte erheblich

Da WLP- und WLCSP-Verpackungen direkt auf dem "Silizium"-Substratverpackungsprozess aufgebaut sind, muss IC grundsätzlich keine Bonddrähte verwenden, für Hochfrequenzkomponenten kann es direkt bessere hochfrequente elektrische Eigenschaften erhalten und den Voderteil der Verkürzung der Zykluszeit erzielen. Und weil die Verpackung in der Fabrik fertiggestellt werden kann und die Verpackungskosten gleichzeitig eingespart werden können, aber für Ingenieure muss der KonstruktionsPlan auch in Richtung Kostensenkung berücksichtigt werden. Um WLP- und WLCSP-Komponenten aufeinunder abzustimmen, müssen auch die Leiterplattenkosten in gewissem Umfang begrenzt werden. Achten Sie auf dals KompromissDesign oder nehmen Sie dals entsprechende Schaltungslayraus an.

Im Allgemeinen müssen Ingenieure, um WLP- und WLCSP-Komponenten zu impodertieren, zuerst den Footprint von WLP und WLCSP (dh Paketgröße) erhalten, bevoder sie LeiterplattenschaltungsPlanung implementierenieren, und gleichzeitig den Größe-/Kontaktfehler und Kontakt von WLP- und WLCSP-Komponenten bestätigen Die Schlüsselinfürmationen von Komponenten wie Pitch, StartschaltungsLadut, ProzesskomponentenPlanung, Sie können die erhaltenen Komponentenparameter für Design und Planung verwenden, und da die Größe und der Kontakt von WLP und WLCSP kleiner werden, ist es nichtwendig, dals Löten der entsprechenden IC-Pins zu berücksichtigen. MattenDesign.

PCB muss für (SMD)- und ((NSMD))-Fürmen fein abgestimmt werden

Es kann mit WLP- und WLCSP-Pad-Typen abgestimmt werden, und LötMaskeen-Definiert (SMD) und Nonsold Maskee Definiert (NSMD) können verwendet werden. Die LötMaskeenDefinitionsart SMD LötPad ist so konzipiert, dass die Lötmaske verwendet wird, um die LötBalle und den Bereich des LötPads zu definieren, das gelötet werden soll. Diese Konstruktionslösung kann die Möglichkeit verringern, dass der LötPad während des Löt- oder Entlötprozesses hochgezogen wird. Der Nachteil der SMD-Fürm ist jedoch, dass SMD die Oberfläche der mit der Lötkugel verbundenen Knach obenferoberfläche reduziert und gleichzeitig den Raum zwischen den benachbarten Pads reduziert, wodurch die Breite der Spur zwischen den Pads begrenzt wird und die Leiterplatte auch eingeschaltet wird.Das Loch verwendet Elastizität. In den meisten Entwurfsschemata ist das am häufigsten verwendete immer noch das SMD-Entwurfsschema, da die LötPads des SMD bessere Lötverbindungseigenschaften haben können und das Lot und die LötPads während des Herstellungsprozesses zusammen integriert werden können.

Was das nicht-lötende Masken-definierte LötPad (NSMD) betrifft, so besteht die KonstruktionsMethodee darin, Knach obenfer für das Lötbufflöten zu verwenden, um den LötPad-Bereich zu definieren. Diese Entwurfslösung kann eine größere Oberfläche bieten, um die Leiterplatte und die Lötkugel zu verbinden. Gleichzeitig bietet NSMD im Vergleich zur SMD-Designfürm auch einen größeren Isolationsabstund zwischen den LötPads und den LötPads, was einen größeren Verdrahtungsabstund zwischen den LötPads ermöglicht und eine höhier Flexibilität für die Verwendung von Durchgangslöchern der Leiterplatte hat. Wenn der NSMD jedoch lötet, können Entlöten und undere Operationen leicht dazu führen, dass der LötPad hochgezogen wird.

Besondere Beachtung ist bei Abständen erfBestellunglich

Die Berücksichtigung der Pitchgröße ist auch sehr wichtig, besonders wenn die Leiterplatte in Fürm von SMD oder NSMD ist, wird die reservierte Pitchgröße von verschiedenen Lösungen auch geringfügig unterschiedlich sein, und die Pitchgröße bezieht sich auf den Abstund zwischen den Lötkugeln, der zwei ist. Je größer der Verdrahtungsraum zwischen den LötPads und den LötPads, die für die Verdrahtung verwendet werden können.

Für das 0,5 mm Entwurfsschema wird aufgrund des größeren Abstundes mehr Verdrahtungsraum bereitgestellt, oder der Entwurf kann breitere Leitungen und mehr Kupfermaterialien verwenden, was bedeutet, dass höhere Übertragungsströme in den Leiterbahnen angetrieben werden können, und der Isolationsabstund kann den Entwurf auch leicht vervollständigen. Für den Isolierungsabstund müssen im Allgemeinen die erfürderlichen Entwurfsspezifikationen überprüft werden, der allgemeine Isolierungsabstund ist 3~3.5 (mil)s (mil). Verglichen mit dem 0,4 mm PitchbreitenDesign ist es schwieriger zu entwerfen, weil der verfügbsind Verdrahtungsraum flexibelr ist und die verfügbsind IsolationsAnnhöhe aufgrund der schrumpfenden Pitch gleichzeitig reduziert wird. Dies stellt den Kupferwechsel dar, der in der Schaltung verwendet werden kann. Ist dieser geringer, wird der übertragene Antriebsstrom entsprechend reduziert.

In Bezug auf die Leiterplattenverdrahtung ist aufgrund der Eigenschaften von WLP- und WLCSP-Komponenten die verfügbsind Lötkugelposition recht klein. Grundsätzlich ist es unmöglich, mechanische Lochöffnungsgeräte zu verwenden, um Leiterplattenlöcher herzustellen. Da der Lochdurchmesser mechanischer Löcher zu groß ist, kann der Lochöffnungsprozess auch die Leiterplatte verursachen. Die obere dünnere Linie wird aufgrund von Fehlern im Lochöffnungsprozess beschädigt. Bei Leiterplatten, die WLP- und WLCSP-Komponenten verwenden, werden jedoch, da die Schaltungen viel enger sind, stattdessen Lasergebohrte Vias verwendet, die teurer sind.

Im Allgemeinen werden nur mittlere und hohe Einzelpreis-Endprodukte kostengünstige Laserperfürations-PCB-Produktionslösungen verwenden, und Laserperfüration wird auch mit Mehrschichtplatten für die Produktion verwendet, und die Kosten werden mehr als vier Schichten betragen. Das Brett ist viel größer. Für einige kostengünstige Anwendungen ist es grundsätzlich nicht kostengünstig, eine mehrschichtige Platine und ein LaseröffnungsDesign zu verwenden. Eine weitere relativ ungewöhnliche Designlösung ist die Verwendung eines gestaffelten Bump Arrays von WLP-Komponenten, mit denen die Lötkugeln auf dem WLP-Chip gestaffelt werden können, sodass Produktentwickler um mehr Platz kämpfen können. Führen Sie das LeiterplattenschaltungsLayraus aus. Aber tatsächlich sind die Kosten für WLP mit gestaffeltem Bump Array ziemlich hoch. Gleichzeitig muss diese Lösung bei der Entwicklung von WLP- und WLCSP-Komponenten gleichzeitig berücksichtigt werden. Die Schwierigkeit der Komponentenproduktion ist hoch, was die Komponentenkosten erhöhen wird.

Schlussbemerkungen

Die Chipgrößenverpackung auf Wafer-Ebene von WLP- und WLCSP-Komponenten hat einen ausgezeichneten Verbesserungsvorteil für die Reduzierung der Größe des Endprodukts, aber im Austausch für den PCB-Designplan muss auch gleichzeitig aktualisiert werden, mit hochdichten Mehrschichtplatinen und Präzisionsfertigungsprozessen von Laseröffnungen Während der Entwicklung, Der ursprünglich durch IC-Komponenten eingesparte Trägerplatz und Komponentenkosten werden teilweise auf das PCB-Design und die anschließende Massenproduktion übertragen. Stattdessen werden kleinere Komponenten in der Produktionslinie des Produkts verwendet. Die Verarbeitung oder Wartung wird auch einige Betriebsprobleme verursachen, die schwieriger zu implementieren sind, die vor dem jeweiligen Design einzeln berücksichtigt werden müssen.

WLP- und WLCSP-Komponenten sind Chipgrößenpakete auf Wafer-Ebene. Das endgültige IC-Aussehen und die Packungsgröße sind fast die gleichen wie die des Chips. Chipgrößenverpackungen auf Wafer-Ebene haben viele Vorteile, wie eine deutliche Reduzierung der Bauteilgröße, wodurch herkömmliche ICs reduziert werden. Aufgrund der Fläche und Dicke ist das Gewicht der Komponenten leichter, und die Komponenten können durch auzumatisches Zuführen und Trennen hergestellt werden, das für die Massenfertigung besser geeignet ist, was die Gesamtproduktionskosten und sogar die elektrischen Eigenschaften von WLP- und WLCSP-Komponenten selbst für Hochfrequenzanwendungen senken kann. Es wird in mobiln Geräten verwendet, die leicht und in der Größe reduziert sein müssen, wie Mobiltelefonen, Notebooks und tragbsindn Smart-Produkten. Sie können alle verwendet werden, um die Fläche des Trägers und das Gewicht des Produkts stark zu reduzieren. Wenn WLP- und WLCSP-Komponenten vor der Einführung für Wafer-Level-Verpackungstechnik stärker integriert werden können, wie z.B. mit ReVerkabelung Layer Technology, Bumps usw., um das Design von WLP- und WLCSP-Komponenten zu verbessern, kann die Kombination von WLP-, WLCSP-Komponenten und Leiterplatte in das Design integriert werden.