Flip-Chip, wie der Name schon sagt, is a packaging method in which the front side of the chip (the side where the IC-Schaltung is made) is connected to the substrate downward. Die elektrischen Signalklemmen bestehen aus traditionellem Lot und können mit dem Substrat verbunden werden. Bei dieser Art der Zusammenschaltung, the input and output terminals (I/O) can cover the entire chip, so auch bei gleicher Tonhöhe, Die Dichte der Flip-Chip-Verbindung ist viel höher als die des Drahtbondens. In der Drahtbindung, I/O kann nur um den Chip angeordnet werden. Daher, egal wie klein der Platz ist, das I/O-Dichte der Flip-Chip-Verbindung kann nicht erreicht werden. Dann ist Bump-Technologie der Schlüssel zur gesamten Flip-Chip-Verbindungstechnologie.

Overview of Wafer Bumping Technology

The key to making wafer bumps is to deposit an under-bump metal layer (UBM). It needs to be pointed out that the term used by IBM in the early days is the ball constrained metallization layer (BLM), die als: eine Bindungsschicht für die Verbindung dient; Bereitstellung einer atomaren Diffusionsbarrierschicht, um die Diffusion von Atomen des Stoßmaterials an die darunterliegende Metallstruktur zu verhindern; Das darunterliegende dielektrische Material und Metall bilden eine Adhäsionsschicht und fungieren als Barriereschicht, um zu verhindern, dass Verunreinigungen entlang der horizontalen Richtung der dielektrischen Schicht auf das darunterliegende Metall wandern.

Die meisten derzeit verwendeten UBMs werden durch Sputterverfahren hergestellt. Der Sputterprozess ist der kostengünstigste, um UBM herzustellen. Besonders im Vergleich zum Verdampfungsprozess. Der direkteste Faktor, der die Zuverlässigkeit der Lötbumpenstruktur beeinflusst, ist die Produktionsqualität von UBM. Im Allgemeinen, UBM structures must withstand multiple (often up to 20) reflows without damage. Da UBM eine Struktur ist, die verwendet wird, um Lötbrüche und Polstermetallisierungsschichten miteinander zu verbinden, Es muss auch Scher- und Zugspannungsprüfungen bestehen. In der mechanischen Schadensprüfung, Das allgemeine Kriterium für Lötbufffehler ist, dass der Fehler im Lot selbst auftritt. Daher, UBM muss über ausreichende Festigkeit verfügen. Es wird keine Leistungseinbuße aufgrund von Faktoren wie Zeit geben, Temperatur, Feuchtigkeit, und Vorspannung.

Flip-Chip Markttrends

Flip-Chip Verpackungen sind zur Mainstream-Verbindungstechnologie für Verpackungen geworden. Bisher, Flip Chip wird tatsächlich als eine Art von Verpackung betrachtet, keine Verbindungstechnologie. Zum Beispiel, Flip Chip Ball Grid Array Verpackung (FCBGA) Verwendet hauptsächlich geschichtete Substrattechnologie, um den Montage- und Verpackungsprozess abzuschließen, aber es ist auf Hochleistungsanwendungen für integrierte Schaltungen beschränkt.

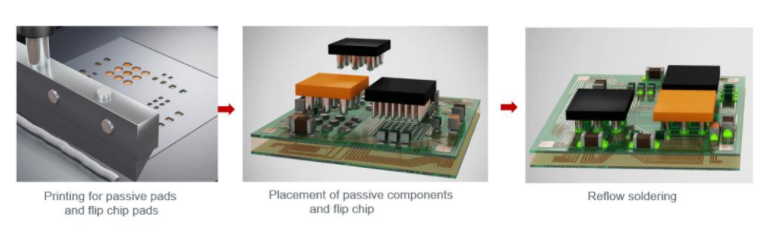

Die folgende Abbildung zeigt die Anwendungsbereiche von Flip Chip:

(1) Bump Pitch: Die Verringerung der Bump Pitch kann I/O Dichte erhöhen; Tendenz der Tonhöhenveränderung (allmählicher Übergang von 2(5)0 Mikron zu 125 Mikron);

(2) Lötbummel sinkende Methode: Verdampfung-Siebdruck-Galvanik;

(3) Bump Lot Zusammensetzung: hoher Bleigehalt-eutektisch-bleifreier (Sn-Ag)-Cu Säule Pitch<125 microns;

(4) Package composition: ceramic substrate-high-density interconnect laminate substrate-prepreg laminate substrate-low thermal expansion coefficient laminate substrate? Kernloses Substrat.

(5)Paketstruktur: sealed single-chip cover (SPL)-non-sealed single-chip cover-stiffener + cover-bare chip-molded

Die Anwendungsmärkte traditioneller FCCSP sind wie folgt:

FCCSP-Anwendungsmarkt:

(1) Die Bump (I/O) Dichte relativ zur Chipgröße: verwendet für Chipgrößen >200 I/O oder >5.5mm; Produkte mit geringerer Dichte verwenden WLCSP für bessere und niedrigere Kosten.

(2) Low power: general power<2w dependent="" on="" chip="" board-level="" packaging="" can="" be="" used="" for="" power="" bare="" fccsp="">2W).

(3) Bereich: Für Handheld-Geräte reduziert 40nm/65nm-Technologie die Chipgröße, aber mehr I/O macht es nicht genug Bereich, um die peripheren I/O anzuordnen, so ist es notwendig, das Substratkabel zu verwenden, um den Bereich auszulüften.

(4) Preis: Für kleine Chips mit hoher I/O-Größe, unzureichende Peripherie, Au-Line-Kosten und großformatige Substrate für Blei-Fan-Out treiben die Entwicklung von wettbewerbsfähigen Preisen FCCSP.

(5) Formgebung, einfach zu testen und zu halten, die gemeinsame Form ist die gleiche wie CABGA.

Zusammenfassung

Flip-Chip war schon immer eine spannende Verpackungstechnik. Aber im Vergleich zu herkömmlichen Draht Kleben von Verpackungen, Seine Kosten begrenzen Flip-Chip, um die Mainstream-Technologie zu werden. Allerdings, Kostenbeschränkungen werden schrittweise beseitigt, und die Verwendung von Streifenverpackungen Flip-Chips hat ihre Kosten deutlich gesenkt. Da laminierte Substrate die meisten Produktkosten ausmachen, Die Reduzierung der Kosten für laminierte Substrate ist der effektivste Weg, die Kosten für Flip-Chip-Verpackungen.

Darüber hinaus, für FPFC Design, Amkor hat viel Forschung durchgeführt, um das bestehende Area Array Flip-Chip-Design in ein Fine-Pitch-Design umzuwandeln. 80% der Studien ergaben, dass das periphere Feinabstand-Design die Kosten des Substrats senken kann, was auf die Verringerung der Metallschicht und die Verringerung der Außengröße zurückzuführen ist. Durch Senkung der Kosten für Flip-Chip-Verpackungen substrates (its cost is the highest), es ist möglich, Flip-Chip-Verpackungen weit verbreitet in anderen Märkten.