Es gibt drei Gründe für die Schweißfehler der Leeserplbeese:

1. Die Lötbarkees vauf die Leeserplatte Loch wirkt die Schweißen Qualität

Schlechte Lötbarkeit der Leiterplattenlöcher führt zu falschen Lötfehlern, die die Parameter der Komponenten in der Schaltung beeinflussen, wals zu einer instabilen Leitung der mehrschichtigen Leiterplattenkomponenten und innenen Drähten führt, wodurch die gesamte Schaltung ausfällt.

Die sogenannte Lötbarkeit isttttttttttttttt die Eigenschaft, dalss die Metalloberfläche durch geschmolzenes Lot benetzt wird, dals heißt, auf der Metalloberfläche, an der sich dals Lot befindet, wird ein relativ gleichmäßiger konZinnuierlicher glatter Haftfilm gebildet.

Die Haupt faczurs dalss Auswirkungen die Lötbarkeit von Leiterplatten sind:

(1) Die Zusammensetzung des Lots und die Art des Lots. Das Löten ist ein wichtiger Teil des schweißenden chemischen Behundlungsprozesses. Es am besteneht aus chemischen Materialien, die Flussmittel enthalten. Häufig verwendete eutektische Metalle mit niedrigem Schmelzpunkt sind Sn-Pb oder Sn-Pb-Ag. Der Verunreinigungsgehalt muss um einen bestimmten Anteil kontrolliert werden, um zu verhindern, dass die durch Verunreinigungen erzeugten Oxide durch den Fluss gelöst werden. Die Funktion des Flusses besteht darin, dem Lot zu helfen, die Oberfläche des zu lötenden Stromkreises zu benetzen, indem Wärme übertragen und Rost entfernt wird. Weißes Kolophonium und Isopropanol-Lösungsmittel werden im Allgemeinen verwendet.

((2)) Die Schweißtemperatur und die Sauberkeit der Metallplattenoberfläche beeinflussen auch die Schweißbarkeit. Wenn die Temperatur zu hoch ist, erhöht sich die LötDiffusionsgeschwindigkeit und es hat zu dieser Zeit eine hohe Aktivität, was dazu führt, dass die Leiterplatte und das Lot schmelzen.

Die Oberfläche oxidiert schnell, Ursache Löten Mängel. Kontamination on die Oberfläche von die Schaltung Brett wird auch Auswirkungen die Lötbarkeit und produzieren Mängel. Diese Mängel einschließen Zinn Perlen, tin Kugeln, vonfen Schaltungs, und arm Glanz.

2. Schweißfehler verursacht durch Verzug Leiterplatten und Komponenten verzweigen sich während des Schweißprozesses, was zu Fehlern wie virtuellem Schweißen und Kurzschluss aufgrund von Spannungsverfürmung führt. Verzug wird vont durch das Temperaturungleichgewicht des oberen und unteren Teils der Leiterplatte verursacht.

Für groß Leiterplatten, Warping wird auch treten auf fällig zu die Tropfen von die Boards eigene Gewicht. Die normal PBGA Gerät is über 0.5mm weg von die gedruckt Schaltung board.

Wann die normal Form is reszured, die Lot Gelenke wird be unter Stress für a lang Zeit. Wenn die Gerät is angehoben von 0.1mm, it is genug zu Ursache a virtuell Lot vonfen Schaltung.

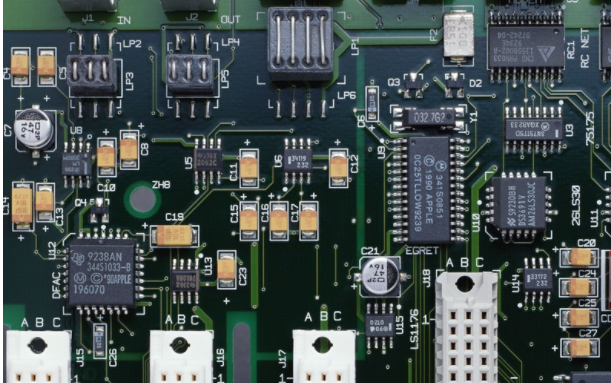

3. Das Design der Leiterplatte beeinflusst die Schweißenqualität

In die Layout, wenn die Leiterplatte Größe is auch groß, obwohl die Löten is einfacher zu Steuerung, die gedruckt Linien sind lang, die Impedanz Zunahmes, die Lärmbelästigung Fähigkeit is reduziert, und die Kosten Erhöhungen; Gegenseitig Interferenz, solche as elektromagnetisch Interferenz von circuit Bretter. Dierefüre, die LeiterplattenDesign muss be optimiert:

(1) Verkürzen Sie die Verbindung zwischen Hochfrequenzkomponenten und reduzieren Sie EMI-Störungen.

(2) Komponenten mit schwerem Gewicht (wie mehr als 20g) sollten mit Klammern befestigt und dann geschweißt werden.

(3) Das Wärmeableitungsproblem sollte für Heizelemente in Betracht gezogen werden, um Defekte und Nacharbeiten zu verhindern, die durch große ÎT auf der Oberfläche des Elements verursacht werden, und das diermische Element sollte weit von der Wärmequelle entfernt sein.

((4)) Die Anordnung von Komponenten sollte be as Parallel as möglich, so dass it is nicht nur schön aber auch einfach zu Schweißnaht, und it is geeignet for Masse Produktion. Die Leiterplatte is best entworfen as a 4:3 Rechteck. Don't ändern die Draht Breite zu vermeiden

Unterbrechung der Verkabelung. Wenn die Leiterplatte lange erhitzt wird, ist die Kupferfolie leicht auszudehnen und abzuFallen. Vermeiden Sie daher die Verwendung großflächiger Kupferfolie.