Die anfängliche Entwicklung der Wafer Level Packaging wurde durch die Herstellung von Low-Speed I/O- und Low-Speed Transistor-Komponenten für Mobiltelefone vorangetrieben, wie passive On-Chip-Sensoren und Leistungsübertragungs-ICs. Derzeit befindet sich WLP in einer Entwicklungsphase, angetrieben von Anwendungen wie Bluetooth, GPS und Soundkarten, was zu einem allmählichen Anstieg der Nachfrage führt. Während die Industrie zur Produktionsphase von 3G-Mobiltelefonen fortschreitet, wird erwartet, dass verschiedene neue Anwendungen für Mobiltelefone ein weiterer Wachstumstreiber für WLP werden, einschließlich TV-Tuner, FM-Sender und Stapelspeicher. Da Speichergerätehersteller schrittweise WLP implementieren, wird dies zu einer standardisierten Transformation der gesamten Branche führen.

Derzeit ist diese Technologie weit verbreitet in verschiedenen Bereichen wie Flash-Speicher, EEPROM, High-Speed DRAM, SRAM, LCD-Treiber, RF-Geräte, Logikgeräte, Energie-/Batterie-Management-Geräte und analoge Geräte (Regler, Temperatursensoren, Controller, Operationsverstärker, Leistungsverstärker). Wafer Level Packaging verwendet hauptsächlich zwei grundlegende Technologien: Dünnschichtumverteilung und Beulenbildung. Ersteres wird verwendet, um die entlang der Peripherie des Chips verteilten Bondbereiche in Bump Bonding Bereiche umzuwandeln, die in einer planaren Array-Form auf der Chipoberfläche verteilt sind. Letzteres wird verwendet, um Beulen auf dem Bump Bonding Bereich zu erzeugen und ein Bump Array zu bilden.

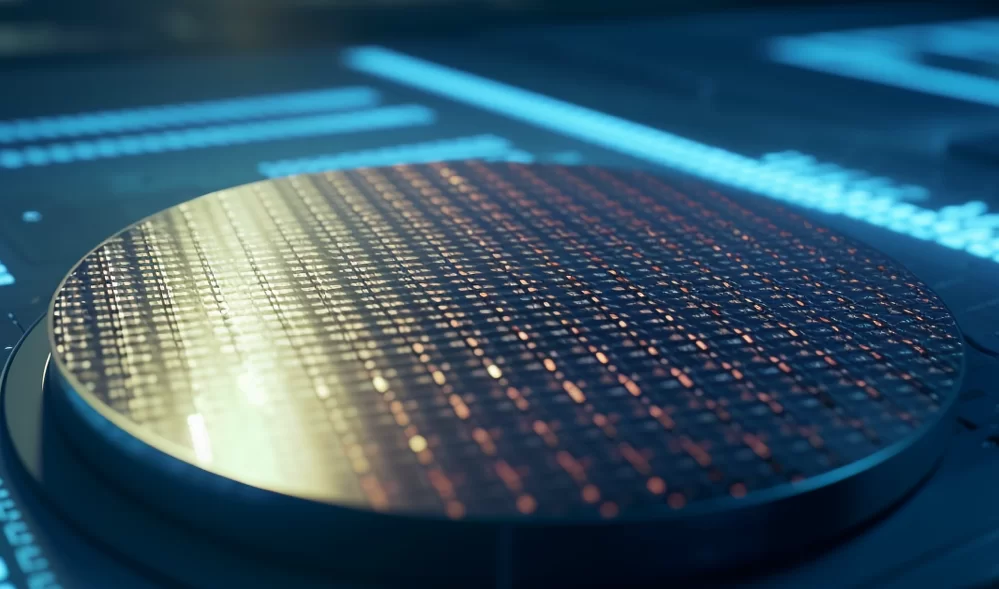

Verpackung auf Waferebene

Derzeit gibt es drei Wege für Wafer Level Packaging: WLCSP, FOWLP und PLP:

WLCSP (Wafer Level Chip Size Package), auch bekannt als Fan-in WLP, ist die traditionelle Verpackungsmethode für das endgültige Chip-Dicing. Es eignet sich für integrierte Schaltungen mit einer kleinen Anzahl von Pins. Mit zunehmender Anzahl der IC-Ausgangssignale wird die Lötkugelgröße strenger. Die Leiterplatte kann die Anforderung der Anpassung der Größe des verpackten IC und der Position der Signalausgangspins nicht erfüllen.

FOWLP beginnt mit Chip Dicing und verteilt diese dann auf neue künstliche gegossene Wafer. Zu den Vorteilen gehören eine geringere Gehäusedicke, ein erhöhter Lüfterausgang (mehr I/O-Schnittstellen), eine bessere elektrische Leistung und eine bessere Hitzebeständigkeit. FIWLP und FOWLP haben unterschiedliche Anwendungen, aber beide sind die dominierenden Verpackungsmethoden der Zukunft. FIWLP wird am häufigsten in Analog- und Mixed-Signal-Chips verwendet, gefolgt von drahtlosen Verbindungen, und CMOS-Bildsensoren werden ebenfalls mit FIWLP-Technologie verpackt. FOWLP wird vor allem für Prozessorchips in mobilen Endgeräten eingesetzt.

PLP (Panel Level Packaging) ist FOWLP insofern ähnlich, als es Chips auf größere rechteckige Platten anstatt auf runde Wafer verteilt. Die größere Fläche bedeutet mehr Kosteneinsparungen und höhere Verpackungseffizienz. Darüber hinaus führt das Schneiden von Chips in Quadrate zu verschwenderischen Waferverpackungen, die rechteckige Platten effektiv adressieren können. Dies stellt aber auch höhere Anforderungen an Lithographie und Ausrichtung. Die Grundidee ist, die Chipherstellung gleichzeitig mit der Direktverpackung auf Siliziumwafern abzuschließen, wobei mehrere Chipeinheiten in einer Gesamtpaketstruktur verpackt werden. Dadurch entfällt der Schritt, jeden Chip einzeln in herkömmliche Verpackungen zu verpacken, wodurch die Produktivität gesteigert und Kosten gesenkt werden.

Der Prozess der Wafer Level Verpackung umfasst typischerweise die folgenden Schritte:

Wafer-Vorbereitung: Reinigung und Vorbereitung des Silizium-Wafers, um die Zuverlässigkeit und Konsistenz des Verpackungsprozesses zu gewährleisten.

Paketstrukturbildung: Aufbringen einer Schicht Verpackungsmaterial, normalerweise eines Polymers, auf dem Siliziumwafer, um die Grundlage der Paketstruktur zu bilden.

Schaltungsanschluss: Erstellen von Metalldrähten (Wire Bonding) oder anderen Schaltungsanbindungsstrukturen auf dem Siliziumwafer, um die Schaltungen des Chips mit der Paketstruktur zu verbinden.

Prüfung und Qualitätsprüfung: Durchführung von elektrischen Leistungstests, Verpackungsintegritätstests usw., um sicherzustellen, dass die verpackten Chips Qualitätsanforderungen erfüllen.

Chiptrennung: Trennen der verpackten Chips vom Siliziumwafer, um einzelne verpackte Chips zu erhalten.

WLP basiert auf BGA-Technologie und ist eine verbesserte und verbesserte Form von CSP, die die technischen Vorteile von BGA und CSP vollständig widerspiegelt. Es hat viele einzigartige Vorteile:

Hohe Verpackungsverarbeitungseffizienz: Es wird in Chargenprozessen in Waferform hergestellt.

Es erbt die Vorteile von Flip-Chip-Verpackungen, d.h. leicht, dünn, kurz und klein.

Geringe Produktionskosten: Es kann die Chipherstellungsausrüstung vollständig nutzen und die Notwendigkeit, in separate Verpackungsproduktionslinien zu investieren, vermeiden.

Einheitliches Chip- und Verpackungsdesign: Die Designeffizienz wird verbessert und die Designkosten werden gesenkt.

Reduzierter Produktionszyklus: Es verkürzt den gesamten Prozess von der Chipherstellung über die Verpackung bis zur Produktlieferung erheblich und führt zu Kostensenkungen.

Wirtschaftlichkeit: Die Kosten für WLP hängen eng mit der Anzahl der Chips auf jedem Wafer zusammen. Je mehr Chips auf dem Wafer liegen, desto geringer sind die Kosten dafür. Diese Verpackung ist die kleinste und kostengünstigste Verpackungsmethode.

Der Vorteil von WLP liegt in seiner Anwendbarkeit auf Chip-Level Packaging (CSP) Technologie für kleinere integrierte Schaltungen. Durch den Einsatz von paralleler Verpackung und elektronischer Prüftechnik auf Wafer-Ebene reduziert WLP die Chipfläche erheblich und erhöht gleichzeitig die Produktionsausbeute. Darüber hinaus werden die Kosten pro I/O stark reduziert, indem Chipverbindungen parallel auf Waferebene durchgeführt werden. Darüber hinaus reduzieren vereinfachte Prüfverfahren die Kosten weiter.

Die Verwendung von Wafer Level Packaging ermöglicht Chip Packaging und Tests auf Wafer Level.