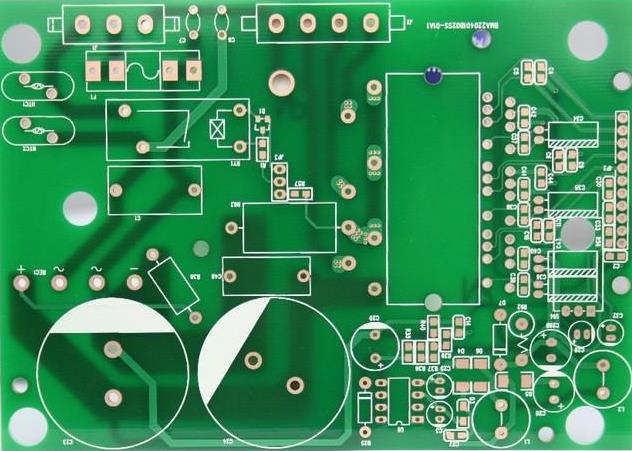

Heutzutage sind die Faktoren, die beim PCB-Board-Design berücksichtigt werden, immer komplexer, wie Uhr, Übersprechen, Impedanz, Erkennung, Herstellungsprozess usw., wodurch Designer oft viele Layout-, Verifizierungs- und Wartungsarbeiten wiederholen. Der Parameter Constraint Editor kann diese Parameter formulieren, um Designern zu helfen, diese manchmal sogar gegensätzlichen Parameter während des Entwurfs- und Produktionsprozesses besser zu handhaben. In den letzten Jahren sind die Anforderungen an Leiterplattenlayout und Verdrahtung immer komplexer geworden, und die Anzahl der Transistoren in integrierten Schaltungen nimmt immer noch mit der Geschwindigkeit zu, die durch Moores Gesetz vorhergesagt wird, was das Gerät schneller macht und die Anstiegszeit jeder Pulskante verkürzt. Gleichzeitig steigt auch die Anzahl der Pins. Immer mehr, oft bis 500 bis 2.000 Pins. All dies verursacht Dichte, Taktung und Übersprechen Probleme beim Design einer Leiterplatte. Vor einigen Jahren hatten die meisten Leiterplatten nur wenige "kritische" Knoten (Netze), die sich normalerweise auf einige Einschränkungen in Impedanz, Länge und Abstand bezogen. Leiterplattendesigner führten diese Spuren im Allgemeinen zuerst durch. Manuelle Verkabelung und dann verwenden Sie Software, um den gesamten Stromkreis automatisch in großem Maßstab zu routen. Heutige Leiterplatten haben oft 5.000 oder mehr Knoten, und mehr als 50% von ihnen sind kritische Knoten. Aufgrund des Time-to-Market-Drucks ist ein manuelles Routing derzeit nicht mehr möglich. Darüber hinaus hat sich nicht nur die Anzahl der kritischen Knoten erhöht, sondern auch die Einschränkungen für jeden Knoten. Diese Einschränkungen sind vor allem auf Parameterabhängigkeiten und immer komplexere Designanforderungen zurückzuführen. Beispielsweise kann der Abstand von zwei Leiterbahnen von einer Funktion der Knotenspannung und des Leiterplattenmaterials abhängen. Die Anstiegszeit der digitalen IC verringert sich. Sowohl hohe Taktgeschwindigkeit als auch niedrige Taktgeschwindigkeit haben Auswirkungen. Die Rüst- und Haltezeiten sind durch schnellere Impulserzeugung kürzer. Darüber hinaus ist die Verbindungsverzögerung ein wichtiger Teil der Gesamtverzögerung des Hochgeschwindigkeitsschaltungsdesigns. Es ist auch sehr wichtig für Low-Speed-Designs, etc. Warten. Einige der oben genannten Probleme wären einfacher zu lösen, wenn das Board etwas größer gestaltet werden könnte, aber der aktuelle Trend ist genau das Gegenteil. Leiterplatten werden aufgrund von Verbindungsverzögerungen und hohen Verpackungsanforderungen kleiner, was zu Schaltungsdesigns mit hoher Dichte führt, die Miniaturisierungsdesignregeln folgen müssen. Die Kombination aus reduzierter Anstiegszeit und diesen Miniaturisierungsentwurfsregeln hat das Problem des Übersprecherauschens immer deutlicher gemacht, während Ballgitterrays und andere Pakete mit hoher Dichte selbst Probleme wie Übersprechen, Schaltrauschen und Ground Bounce verschärfen können.

Feste Beschränkungen existDie traditionelle Art, mit diesen Problemen umzugehen, besteht darin, elektrische und prozessuale Anforderungen anhand von Erfahrungen, Standardwerten, Tabellen oder Berechnungen in feste Beschränkungsparameter zu übersetzen. Zum Beispiel kann ein Ingenieur beim Entwerfen einer Schaltung zuerst eine Nennimpedanz bestimmen und dann eine Nennlinienbreite "schätzen", die die erforderliche Impedanz entsprechend den Prozessanforderungen erreichen kann, oder eine Berechnungstabelle oder ein arithmetisches Programm verwenden, um die Störung zu testen und dann die Längenbeschränkungen zu finden. Dieser Ansatz erfordert in der Regel die Erarbeitung einer Reihe empirischer Daten als grundlegende Richtlinie für den Leiterplattendesigner, die beim Entwerfen mit automatischen Ort- und Routenwerkzeugen verwendet werden können. Das Problem dieses Ansatzes ist, dass empirische Daten nur ein allgemeines Prinzip sind und meistens korrekt sind, aber manchmal nicht funktionieren oder zu falschen Ergebnissen führen. Nehmen wir das Beispiel der Impedanzbestimmung oben, um zu sehen, welche Fehler diese Methode verursachen kann. Zu den impedanzbezogenen Faktoren gehören die dielektrischen Eigenschaften des Leiterplattenmaterials, die Höhe der Kupferfolie, der Abstand von jeder Schicht zur Erdungs-/Leistungsschicht und die Leitungsbreite. Da die ersten drei Parameter in der Regel vom Produktionsprozess bestimmt werden, verlassen sich Konstrukteure meist auf die Linienbreite. zur Kontrolle der Impedanz. Da jede Schaltungsschicht einen anderen Abstand zur Erdungs- oder Leistungsschicht hat, ist es offensichtlich falsch, für jede Schicht dieselben empirischen Daten zu verwenden. Verschärft wird das Problem dadurch, dass sich der Produktionsprozess oder die Platteneigenschaften während der Entwicklung jederzeit ändern können. Meistens werden diese Probleme in der Prototyping-Phase aufgedeckt, die normalerweise durch Reparatur der Leiterplatte oder Neugestaltung der Leiterplatte gelöst wird, nachdem das Problem gefunden wurde. Dies ist teuer, Fixes führen oft zu zusätzlichen Problemen, die ein weiteres Debuggen erfordern, und die verlorenen Einnahmen aufgrund von Verzögerungen in der Time-to-Market sind weit höher als die Kosten für das Debuggen. Fast jeder Elektronikhersteller steht vor diesem Problem, und es läuft darauf hinaus, dass herkömmliche PCB-Board-Design-Software nicht mit der aktuellen Realität der elektrischen Leistungsanforderungen Schritt halten kann. Zu diesem Zeitpunkt ist es nicht so einfach wie empirische Daten zum mechanischen Design. Lösung: Anbieter von parametrischen Einschränkungen versuchen derzeit, dieses Problem durch Hinzufügen von Parametern zu Einschränkungen zu lösen. Das Schöne an diesem Ansatz ist, dass es mechanische Spezifikationen spezifizieren kann, die die verschiedenen internen elektrischen Eigenschaften vollständig widerspiegeln, und solange es dem PCB-Design hinzugefügt wird, kann die Designsoftware diese Informationen verwenden, um automatische Platzierungs- und Routingwerkzeuge zu steuern. Wenn sich der nachfolgende Produktionsprozess ändert, ist eine Neugestaltung nicht erforderlich. Der Konstrukteur muss lediglich die Prozesskenngrößen aktualisieren, um die relevanten Einschränkungen automatisch zu ändern. Designer können dann eine DRC (Design Rule Check) durchführen, um festzustellen, ob der neue Prozess auch andere Designregeln verletzt, und um herauszufinden, welche Aspekte des Designs geändert werden sollten, um Fehler zu korrigieren. Constraints können in Form von mathematischen Ausdrücken eingegeben werden, einschließlich Konstanten, verschiedene Operatoren, Vektoren und andere Designbeschränkungen, wodurch Designer ein parametrisches regelgesteuertes System erhalten. Einschränkungen können sogar in Form von Nachschlagetabellen eingegeben und in der Designdatei auf der Leiterplatte oder im Schaltplan gespeichert werden. Leiterplattenrouting, Kupferfolienbereiche und Layoutwerkzeuge müssen den durch diese Bedingungen erzeugten Einschränkungen entsprechen. DRC prüft, ob das gesamte Design diesen Einschränkungen entspricht, einschließlich Linienbreite, Abstand und Platzanforderungen (z. B. Flächen- und Höhenbeschränkungen) usw. Ein sehr einfaches Beispiel ist die Anstiegszeit, die in der Regel auf eine Konstante 1,5ns gesetzt wird. Entsprechend dieser Bedingung kann die Spurlängenbeschränkung erhalten werden, das heißt, 5.800mil/ns mal die Anstiegszeit von 1.5ns. Ein etwas komplexeres Beispiel ist der Elementabstand, der durch Multiplikation der Tangente des Erfassungswinkels mit der Gerätehöhe bestimmt wird, was den Elementabstand ergibt. Hierarchisches Management: Ein großer Vorteil von parametrischen Einschränkungen ist, dass sie hierarchisch gehandhabt werden können. Beispielsweise kann die globale Linienbreitenregel als Designbeschränkung im gesamten Design verwendet werden. Natürlich gibt es einzelne Regionen oder Knoten, die dieses Prinzip nicht kopieren können. Zu diesem Zeitpunkt können die hohen Einschränkungen umgangen und die Low-Level-Einschränkungen im hierarchischen Design verwendet werden.1) Design-Einschränkungen für alle Objekte ohne andere Einschränkungen.2) Hierarchische Beschränkungen für Objekte auf einer bestimmten Ebene.3) Knotentyp-Beschränkungen für alle Knoten, die in einem bestimmten Typ enthalten sind.4) Knoten-Beschränkungen, die für einen bestimmten Knoten verwendet werden.5) Klassenbeschränkungen, die Beschränkungen zwischen zwei Arten von Knoten darstellen.6) Platzbeschränkungen für alle Geräte in einem Raum.7) Gerätebeschränkungen für ein bestimmtes Gerät. Beispiel 1: Linienbreite (Impedanz, Schichtabstand, Dielektrizitätskonstante, Kupferfolienhöhe)Hier ist ein Beispiel, wie parametrische Einschränkungen als Designregeln zur Impedanzsteuerung verwendet werden können. Wie bereits erwähnt, ist die Impedanz eine Funktion der Dielektrizitätskonstante, des Abstandes zur Nahschaltungsschicht, der Breite und Höhe der Kupferleitung. Da die für den Entwurf erforderliche Impedanz bestimmt wurde, können diese vier Parameter willkürlich als relevante Variablen genommen werden, um die Impedanzformel umzuschreiben. In den meisten Fällen ist der einzige Parameter, den der Designer steuern kann, die Linienbreite. Aus diesem Grund sind die Einschränkungen der Leitungsbreite eine Funktion der Impedanz, der Dielektrizitätskonstante, des Abstands zu linearen Schichten und der Höhe der Kupferfolie. Wenn die Formel als Niveaubegrenzung definiert ist und die Fertigungsprozessparameter als Designebene definiert sind, passt die Software automatisch die Linienbreite an, um zu kompensieren, wenn sich die entworfene Linienebene ändert. In gleicher Weise, wenn die entworfene Schaltung