Da sich die Computerindustrie in Richtung DC-DC-Wandler bewegt, die bis zu 200A bei 1V liefern können, müssen Leiterplattenlayouttechniken die Anforderungen dieses herausfordernden aufstrebenden Wandlers erfüllen. Um die Auswirkungen verschiedener Verdrahtungsfehler zu vergleichen, konzentrieren wir uns auf die Auswirkungen parasitärer Induktivitäten in der Schaltung, insbesondere diejenigen, die mit der Quelle, dem Drain und dem Gate von Schalt-MOSFETs verbunden sind. Wir haben eine Leiterplatte zum Testen eines DC-DC-Wandlers gebaut, der 12V DC aufnimmt und in 1,3V umwandelt und bis zu 20A ausgibt. Wir verwenden eine Steckplatine zur Montage und können die Induktivität an jeder MOSFET-Elektrode einzeln oder gleichzeitig jederzeit ändern. Wir haben uns entschieden, den Induktivitätswert als Prozentsatz der Gesamtinduktivität einer speziell entwickelten 2-Zoll-Platine zu verwenden, anstatt als tatsächlichen Wert, da die Verkabelungsperson nur die Länge einer bestimmten Leiterbahn und nicht unbedingt den Wert ihrer Induktivität kennt.

Versuchskonzept

Wir verwenden Konvertereffizienz, um die Wirksamkeit dieser parasitären Induktivitäten zu messen. Dies liegt daran, dass Effizienz ein Standardmaß für die Leistung von DC-DC-Wandlern ist. Der Test ist in die folgenden Teile unterteilt: justieren Sie den proportionalen Koeffizienten jedes Induktivitätswertes des MOSFET-Abflusses, der Quelle und des Gates und beobachten Sie den Effekt auf den Synchrongleichrichter, indem Sie die Umwandlungseffizienz messen. Durch die Kombination von zwei der oben genannten, um die Beziehung zwischen ihnen zu verstehen. Die Induktivitätsprüfplatine hat eine Induktivität von 43nH und wird typischerweise auf 0%, 25%, 50%, und 100%. In unseren Experimenten hat der parasitäre Widerstand auf der Induktivitätsprüfplatine wenig Wirkung und kann ignoriert werden. Da die schädlichen Auswirkungen parasitärer Induktivitäten frequenzabhängig sind, experimentierten wir mit drei voreingestellten Schaltfrequenzen: 300kHz, 600kHz und 1MHz. So können wir sehen, wie wichtig es für das Design sein wird, zukünftig von normalen Schaltfrequenzen auf höhere Frequenzen zu wechseln. Wir alle wissen, dass in Stromkreisen die Länge aller Leiterbahnen kurz gehalten werden muss, um Spannungs- und Stromklingeln zu vermeiden, das gesamte EMI der Platine zu reduzieren und die "stabileren" Komponenten in der Schaltung zu vermeiden (insbesondere für analoge Steuerkreise und verwandte Komponenten). Darüber hinaus zeigt das Referenzmaterial, dass die Quellinduktivität des Steuerungs-MOSFET einen nichtlinearen Effekt auf die Erhöhung der Quellstrom-Fallzeit hat, was zu einer höheren Verlustleistung und geringerer Umwandlungseffizienz führt. Zusätzlich zu den oben genannten Phänomenen kann die Quellinduktivität auch Klingeln am Schalterknoten verursachen.

Prüfschaltungen und Leiterplatten

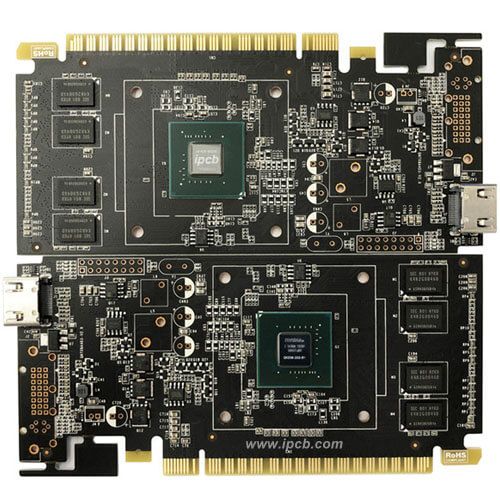

Der verwendete Schaltkreis ist eine synchrone Gleichrichtertopologie, die in einer offenen Schleife arbeitet. Dies soll jegliche Auswirkungen des Regelkreises auf die Schaltungsleistung ausschließen und es uns ermöglichen, uns auf die Leistungsumwandlungseffizienz, insbesondere auf die MOSFET-Leistung, zu konzentrieren. Wir wissen, dass hohe Induktivitätsbedingungen zu starken Klingeln führen können, insbesondere am Schalterknoten. Wählen Sie Gate-Treiber-ICs, die dieses Klingeln ohne negative Auswirkungen vertragen können. Diese vierschichtige Leiterplatte verwendet zwei Unzen Kupfermaterial, und die inneren beiden Schichten sind Erdungs- und Leistungsebenen. Alle Regeln der guten Verdrahtung sollten bei der Verdrahtung beachtet werden.

Einfluss der Gate-Induktivität

Die Gate-Induktivität hat wenig Einfluss auf den Wirkungsgrad bei einer Schaltfrequenz von 300kHz. Bei einer Schaltfrequenz von 600kHz ist der Effekt der Gate-Induktivität viel ausgeprägter, mit einer 1,2% Änderung der Effizienz bei 20A. Bei 1MHz verschwindet die Verschlechterung der Effizienz fast vollständig. Wir haben diesen Grund nicht untersucht und können vermuten, dass es eine 50% Wahrscheinlichkeit gibt, dass der Resonanzfaktor seinen Verlust ausgleicht. Das Resonanzphänomen des MOSFET Gate Antriebs sollte weiter untersucht werden. Wir beobachten, dass die Gate-Induktivität wenig Einfluss auf die Effizienz der Steuerung und synchronen MOSFETs hat.

Einfluss der Quellinduktivität

Die Quellinduktivität hat einen ausgeprägteren Einfluss auf die Effizienz. In einigen Fällen mussten wir den Test abbrechen, bevor wir den Strom erreichten, da die Temperatur des MOSFETs größer als 130°C war. Abbildung 5 zeigt die Ergebnisse der Kontroll-MOSFET-Studie. Eine genauere Betrachtung dieser Ergebnisse zeigt, dass bei einer Frequenz von 300kHz und einer Induktivität von 100%, der DC-DC-Wandler nicht mit voller 20A arbeiten kann, da die Temperatur des MOSFETs 130°C überschreitet. Dasselbe kann bei 50% Induktivität, 600kHz und 1MHz gefunden werden. Die Verschlechterung der Effizienz aufgrund der Quellinduktivität wird als schwerer beobachtet als ohne Quellinduktivität. Wenn die Induktivität 50% und der Strom 15A beträgt, wird der Wirkungsgrad sogar bei der Schaltfrequenz von 300 kHz um 7% reduziert. Wenn die Induktivität 100% beträgt, verschlechtert sich der Wirkungsgrad auf 11%. Bei Schaltfrequenzen von 600kHz und 1MHz ist der Effekt ausgeprägter und der Wirkungsgradverlust ist schwerer als ohne die Quellinduktivität. Es ist klar, dass selbst eine niedrige Quellinduktivität den Wirkungsgrad verringert, insbesondere beim Schalten von Frequenzen ⥠600kHz.

Wirkung der Drain Inductance

Drain Induktivität kann zu starken Klingeln führen, die ausreichen können, um den MOSFET unter extremen Bedingungen zu brechen (Abbildung 3). Es wirkt sich auch negativ auf die Effizienz aus. Die Effizienz ist eine Funktion des Laststroms und entleert die Induktivität bei verschiedenen Frequenzen. Darüber hinaus können die folgenden Ergebnisse beobachtet werden: Wenn der Strom 15A ist, bei 300kHz und 50% Induktivität, müssen wir den Test abbrechen, weil die Temperatur des MOSFET 130â. Bei der gleichen Frequenz, 100% Induktivität, konnten wir keine Messwerte erhalten, weil das Klingeln zu stark war. Bei 300kHz, 12A, 50% der Drainainduktivität ist 7% weniger effizient als 0%. Aufgrund der hohen Temperatur des MOSFET kann der Test nicht über 15A durchgeführt werden. Bei 600kHz, 12.5A, 50% der Drainainduktivität ist 8.5% weniger effizient als 0%. Da die MOSFET-Temperatur zu hoch ist, kann der Test nicht über 12.5A durchgeführt werden. Bei 1MHz kann der Test aufgrund der hohen Temperatur des MOSFETs nicht über 5A durchgeführt werden.

Einfluss der Gate-Source Induktivität

Eine größere Quellinduktivität verringert den Wirkungsgrad erheblich. Eine fundamentale Abhängigkeit der Effizienz von der Gate-Induktivität wurde gezeigt. In Kombination mit einer kleinen Quellinduktivität wird das Gesamtbild recht klar, da eine größere Gate-Induktivität notwendigerweise zu einem größeren Leistungsverlust führt. Die Interpretation dieses Ergebnisses erfordert weitere Studien. Wir können nun feststellen, dass innerhalb angemessener Induktivitätswerte für die Platine die Drain- und Quellinduktivitäten reduziert werden müssen, um eine hohe Konvertereffizienz zu gewährleisten. Die Simulation liefert folgende Ergebnisse: Die Gate- und Quellinduktivitäten resonieren mit der Gate-Source-Kapazität des MOSFET. Wenn das HS-FET die Gate-Quelle ausschaltet, entlädt sich der Kondensator über diese induktiven Pfade. Nachdem der MOSFET ausgeschaltet ist, zwingt die Induktivität den Gate-Strom weiter zu fließen und lädt die Gate-Source-Kapazität um. Diese Ladung wird wieder auf die gleiche Weise entladen und die Gate-Source-Spannung des HS-FET umkehren. Je nach Tauchgang kann sich das HS-FET mit einem großen Kurzschluss wieder einschalten. Die Wirkung wird bei solchen hohen Gate-Induktivitäten stark. In einigen Fällen ist sogar ein zweiter Kurzschlusseffekt zu erkennen. Als Teil dieses Resonanzkreises kann die Quellinduktivität auch auf eine zweite Weise wirken. Wenn ein Kurzschlussstrom auftritt, begrenzt die Quellinduktivität die di/dt (Veränderungsrate des Stroms über die Zeit) des Kurzschlussstroms und begrenzt dadurch Verluste. Die Quellinduktivität verursacht auch eine negative Rückkopplung zur Gate-Source-Spannung und begrenzt Kurzschlüsse. Diese Effekte treten vor allem dort auf, wo parasitäre Gate-Induktivitäten hoch sind. Für einen hohen Wirkungsgrad sollte dieser Effekt durch Design vermieden werden, das heißt, Gate Induktivität muss sorgfältig entworfen werden, um sie zu minimieren.

Einfluss der Induktivität der Quelle HS

Wir untersuchten den Einfluss der Lage der parasitären Quellinduktivität auf die Effizienz. Infolgedessen hat das SteuerFET einen größeren Einfluss auf seine Effizienz als das synchrone FET in der gleichen Menge parasitärer Quellinduktivitätsschleife. Der Grund für dieses Phänomen ist, dass die langsame Schaltsteuerung FET zusätzliche Schaltverluste verursacht, weil der VDS der Steuerung FET höher ist als der des synchronen FET (der Vorwärtsspannungsabfall des synchronen FET ist klein) während des Umwandlungsprozesses. Darüber hinaus hat die Rückkopplung der parasitären Induktivität auf die FET-Gate-Drain-Spannung einen signifikanten Einfluss auf den gesamten HS-FET-Leckstrom. Im Vergleich dazu ist der Effekt der parasitären Quellinduktivität auf den LS-FET-Leckstrom nur teilweise, da er von der Körperdiode des synchronen FET umgangen werden kann.

Auswirkungen paralleler MOSFETs

Wenn MOSFETs parallel geschaltet werden, ist es unwahrscheinlich, dass jede einzelne MOSFET-Schleife in vielen Fällen die gleichen Parasiten aufweist. Wir haben den Einfluss zusätzlicher Induktivität in der MOSFET Drain Loop auf den Wirkungsgrad untersucht. Wir zeigen experimentell den nachteiligen Einfluss parasitärer Induktivität auf die Effizienz von Schalten von MOSFETs in DC-DC Wandlern. Die Schlussfolgerungen sind wie folgt: Der Effekt der Induktivität im Quellkreis ist schwerwiegend, gefolgt von einer ähnlichen Induktivität im Drain-Kreislauf. In unserem Breadboard fanden wir keine ernsthaften Auswirkungen im Zusammenhang mit der Induktivität der Gate-Schaltung. Die Verringerung des Wirkungsgrades hängt eng mit der Schaltfrequenz des Umrichters zusammen. Die Reduzierung des Wirkungsgrades hat viel mit dem Laststrom zu tun. Bei Vorliegen parasitärer Induktivitäten in den Quell- und Drainageschaltungen ist der Wirkungsgradabfall umso größer, je größer der Laststrom ist. Bei heutigen DC-DC-Wandleranwendungen ist beim Routing der Stromversorgungs-Leiterplatte, insbesondere um die Schalt-MOSFETs, besondere Vorsicht geboten. Einer der Vorteile der Verwendung einer mehrschichtigen Platine besteht darin, den parasitären Widerstand und die Induktivität zu reduzieren, indem so viel Strom wie möglich in den Schichten versenkt wird. Dadurch werden Widerstandsverluste und Verluste durch parasitäre Induktivität reduziert. Bei der Entwicklung von Hochfrequenz-DC-Wandlern gibt es viele parasitäre Induktivitätsprobleme, die mit Quell- und Drain-Schaltungen verbunden sind. Die erste ist die Gehäuseinduktivität, und es ist möglich, die kürzlich eingeführten Niedriginduktivitätspakete zum Schalten von MOSFETs zu verwenden. Das zweite Element ist die parasitäre Induktivität der Leiterplatte, die durch Verwendung einer mehrschichtigen Leiterplatte gesteuert werden muss und die Spureninduktivität reduziert werden muss. Dadurch können Konstrukteure weniger Kondensatoren für ein schnelleres dynamisches Ansprechverhalten und erfolgreiche Hochfrequenz-Designs verwenden. Parasitische Induktivitäten, die konstruktiv nicht vermieden werden können, sollten in die synchrone FET-Schleife verschoben werden, da die Induktivität in der synchronen FET-Schleife einen geringeren Einfluss auf die Gesamteffizienz hat als die Induktivität in der SteuerFET-Schleife. Hinweis: Bei niedrigen Betriebszyklen kann der parasitäre Widerstand in der synchronen FET-Schleife die Effizienz erheblich reduzieren. Komplexe Kompromisse müssen im Design getroffen werden (Spurbreite, Kupferdicke, effektiver Schleifenbereich, Vorspannung usw.). Vermeiden Sie parallele MOSFETs. Der Weg, MOSFETs parallel zu ersetzen, besteht darin, zusätzliche Phasen hinzuzufügen oder bessere MOSFETs zu verwenden. Wenn Parallelisierung unvermeidbar ist, muss bei parallelen MOSFETs elektrische Symmetrie im Design gewährleistet sein, um die gleiche Stromverteilung und die gleiche Schaltzeit auf der Leiterplatte zu erhalten.