Die Größe einer einzelnen PCB sollte werden entsprechend der Gesamtstruktur der gesamten Maschine bestimmt. Größe und Form der PCB sollte geeignet für die Produktion von Fertigungslinien für Oberflächenmontage, entsprechend dem Größenbereich der Substrate für Druckmaschinen und Bestückungsmaschinen, und die Arbeitsbreite von Reflow-Lötöfen.

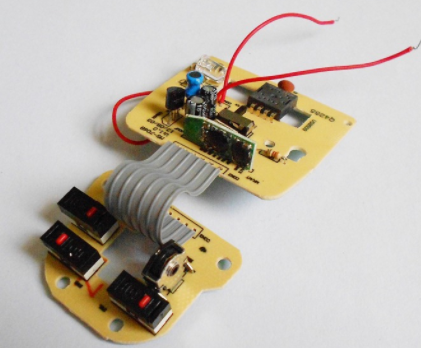

Aufgrund der geringen Größe der KMU, um besser geeignet zu sein für SMT automatisiert Produktion, Mehrere Bretter werden oft zu einem Brett kombiniert, und mehrere Leiterplatten derselben Einheit werden bewusst zu Rechtecken oder Quadraten kombiniert, das Puzzlebrett genannt wird.

Die Verwendung von Spleißplatten für kleine Leiterplatten kann die Produktionseffizienz verbessern, die Anwendbarkeit der Produktionslinie erhöhen und die Kosten für die Werkzeugvorbereitung senken. Einseitige Montage der Leiterplatte wird auf der gleichen Seite montiert, und doppelseitige Vollmontage ohne Wellenlöten kann die doppelt nummerierte Vorder- und Rückseite der Leiterplatte verwenden, und die Grafiken auf beiden Seiten sind in der gleichen Weise angeordnet. Diese Anordnung Es kann die Ausrüstungsauslastung verbessern (jede Investition kann unter den Bedingungen der mittleren und kleinen Chargenproduktion halbiert werden), und Produktionsvorbereitungskosten und -zeit sparen.

Die Stücke können durch V-Nut lineare Teilung, Stempelloch, Stanzen und andere technologische Mittel kombiniert werden, die genaue Gravur, gleichmäßige Tiefe, gute mechanische Stützfestigkeit erfordern, aber leicht von der Trennmaschine gebrochen oder von Hand gebrochen werden können.

Die Montage von Leiterplatten mit kleinen und identischen Leiterplatten kann ebenfalls nach diesem Prinzip durchgeführt werden, jedoch sollte auf die Methode der Zusammenstellung von Bauteilkennzeichen geachtet werden.

(1) Das Stempelbrett kann aus mehreren gleichen Leiterplatten oder mehreren verschiedenen Leiterplatten zusammengesetzt werden.

(2) Bestimmen Sie die maximalen Abmessungen des Stempelbrettes entsprechend der Situation der Oberflächenmontageausrüstung, wie die Platzierungsfläche der Platzierungsmaschine, die maximale Druckfläche der Druckmaschine und die Arbeitsbreite des Reflow-Förderbandes.

(3) Die Verbindungsrippen zwischen den verschiedenen Leiterplatten auf der Stempelplatte spielen die Rolle der mechanischen Unterstützung. Daher muss es eine bestimmte Stärke haben und leicht zu brechen sein, um den Stromkreis zu trennen.

Design von Leiterplattenprüfpunkten und Prüflöchern

Um Qualität zu sichern und Kosten in der SMT-Massenproduktion zu senken, Online-Tests sind unverzichtbar. Um den reibungslosen Ablauf der Prüfarbeiten zu gewährleisten, the design of the test points and test holes (electrical connection holes used for the electrical performance testing of PCB and PCB components) should be considered during PCB-Design.

(1) Entwurf der Kontaktzuverlässigkeitsprüfung. Grundsätzlich sollten die Prüfpunkte auf derselben Oberfläche liegen und gleichmäßig verteilt sein. Der Durchmesser des Pads am Testpunkt ist 09mm ~1.0mm, und es wird mit dem relevanten Prüfstift abgestimmt. Die Mitte des Testpunktes sollte auf das Gitter fallen und vorsichtig sein, nicht innerhalb von 5mm von der Kante der Platine entworfen zu werden, und der Mittelabstand zwischen benachbarten Testpunkten sollte nicht kleiner als 1.46mm sein.

PCB-Testpunkt und Testloch Design Kontakt Zuverlässigkeitstest Design

Keine anderen Komponenten sollten zwischen den Prüfpunkten entworfen werden, und der Abstand zwischen dem Prüfpunkt und dem Bauteilpad sollte nicht kleiner als 1mm sein, um Kurzschlüsse zwischen den Komponenten oder Prüfpunkten zu verhindern, und beachten Sie, dass die Prüfpunkte nicht mit irgendeiner Isolierschicht beschichtet werden können.

Design von Leiterplattenprüfpunkten und Prüflöchern

Grundsätzlich können die Testlöcher durch Prozesslöcher ersetzt werden, aber die Testlöcher sollten immer noch auf der Tochterplatine entworfen werden, wenn die einzelne Platine der Stichsäge getestet wird.

(2) Entwurf des elektrischen Zuverlässigkeitstests, alle elektrischen Knoten sollten Testpunkte bereitstellen, das heißt, Testpunkte sollten in der Lage sein, alle I/0-, Leistungserdungs- und Rücksignale abzudecken, und jeder IC sollte Leistungs- und Erdungsprüfpunkte haben. Wenn das Gerät über mehrere Netzteile und Massepunkte verfügt, sollten Prüfpunkte separat hinzugefügt werden. Die Stromversorgung und Masse eines integrierten Blocks sollten innerhalb von 2.54mm platziert werden, und die IC-Steuerleitung kann nicht direkt an die Stromversorgung, Masse oder gemeinsamen Widerstand angeschlossen werden. VLSI- und ASIC-Geräte mit Begrenzungsscan-Geräten sollten als zusätzliche Testpunkte hinzugefügt werden, um Begrenzungsscan-Funktionen wie Takt, Modus, serielle Dateneingangs-/Ausgabeklemme, Reset-Klemme zu realisieren, um die interne Funktionslogik des Geräts selbst zu testen. Erforderlich.