Abstract: Angesichts der Entwicklung elektronischer Produkte zur Miniaturisierung, hohe Dichte und hohe Geschwindigkeit, die Komplexität der PCB-Design hat stark zugenommen. Wie man die umfassende Qualität von komplexen PCB-Design ist ein Diema, dem wir gegenübertehen. Nach Einführung der VALOR Trilogy 5000 Software, the Prozess of applying DFM (manufacturability analysis technology) to the whole Prozess of product PCB-Design wurde beschrieben, und verglichen mit traditionellen PCB-Design und Prüfmethoden. The PCB-Design Prüfmechanismus kann das Design unterstützen, Prozess, Fertigungs- und Qualitätsinspektionspersonal bei der Qualitätskontrolle des Produktlebenszyklus. Als leistungsstarkes Werkzeug für die automatische Überprüfung vor PCB-Design bis zur Produktion abgeschlossen, es verbessert die Erfolgsrate des ersten Mal PCB-Design. Verkürzung des Produktentwicklungszyklus.

Mit der schnellen Entwicklung elektronischer Produkte wurde eine große Anzahl von hochintegrierten Geräten wie BGA, QFP, PGA und CSP im PCB-Design verwendet. Die Komplexität von PCB hat auch stark zugenommen. Das anschließende PCB-Design und die Herstellung sind schwierig und schwierig zu testen. Produktionsprobleme wie schlechtes Löten, Gerätefehler und schwierige Wartung. Dies führt zu Verzögerungen in der gesamten Produktbauzeit, längeren Entwicklungszyklen, erhöhten Kosten, hohen Reparaturraten und potenziellen Gefahren für die Produktqualität. Gleichzeitig können solche Produkte die Anforderungen an kurze Zeit, hohe Zuverlässigkeit und hohe Stabilität von Militärprodukten nicht erfüllen.

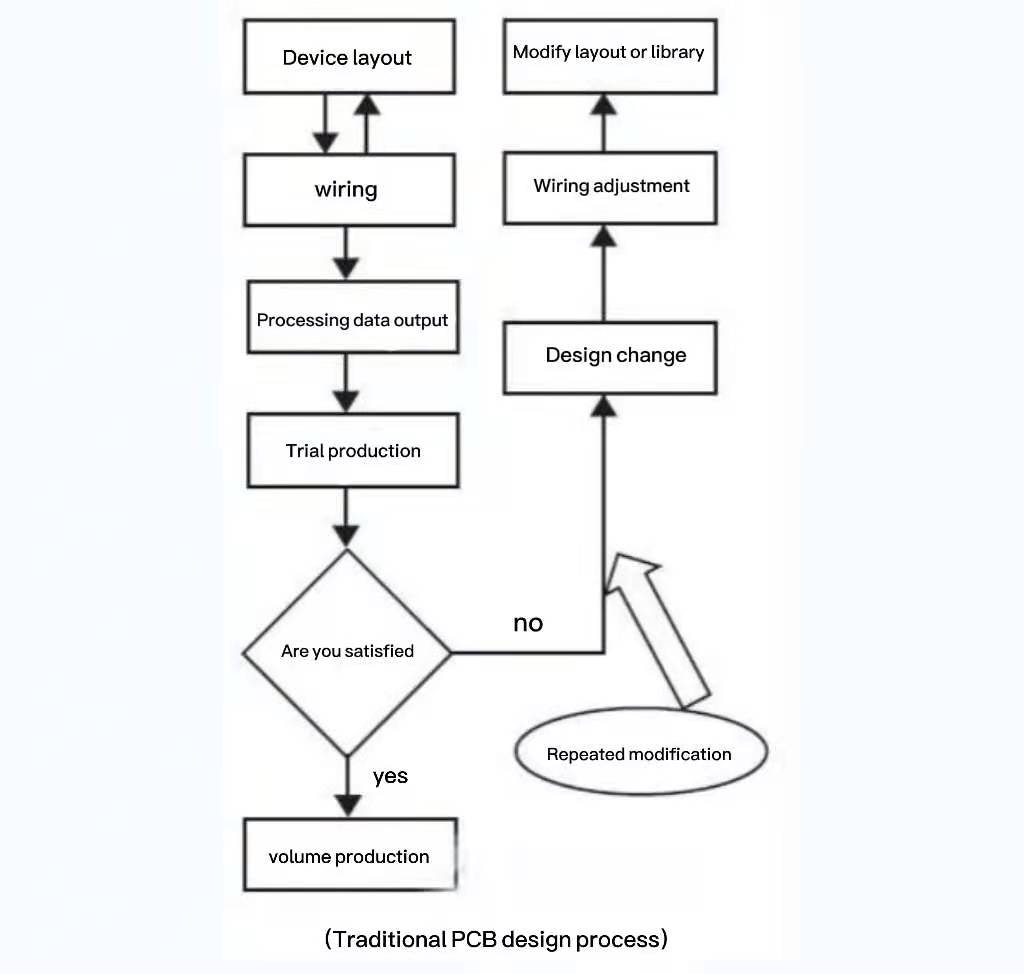

Im eigentlichen Design- und Produktionsprozess führten wir das Konzept "Design for Manufacturability" durch die Anwendung der VALOR-Software Trilogy 5000 DFM-Funktion ein und bewegten das Produktdesign-Qualitätszentrum nach vorne. Integrieren Sie Fertigungsregeln in die Designphase und etablieren Sie einen neuen PCB-Designprozess, wie in Abbildung 1 gezeigt. Um die Zyklusverlängerung durch die Designänderung zu reduzieren, sind die Produktionsqualität und Effizienz garantiert. Lösen oder entdecken Sie alle möglichen Qualitätsrisiken in der frühen Phase der Herstellung, minimieren Sie die Anzahl der Iterationen der Produktentwicklung, senken Sie Kosten und verbessern Sie die Wettbewerbsfähigkeit der Produkte auf dem Markt. Es macht auch die Produktqualität für die verwendete Designsoftware irrelevant und hat nichts mit dem Niveau der Designer zu tun, so dass das Unternehmen in ein standardisiertes Management einsteigen kann.

DFM-Technologiekonzept

DFM-Technologie, das heißt Herstellbarkeitstechnologie, untersucht hauptsächlich die Beziehung zwischen dem physischen Design des Produkts selbst und den verschiedenen Teilen des Fertigungssystems und verwendet es im Produktdesign, um das gesamte Fertigungssystem für die allgemeine Optimierung zu integrieren. DFM-Technologie kann den Entwicklungszyklus und die Kosten des Produkts reduzieren, so dass es reibungsloser in Produktion gebracht werden kann. Mit anderen Worten: DFM soll Probleme frühzeitig im gesamten Produktlebenszyklus finden und lösen.

2. DFM-Softwareanwendung

Die Trilogy 5000 DFM-Analyse umfasst hauptsächlich die Konstruktionsanalyse für die Leichtbauplattenherstellung, die Montageanalyse und die Netzlistenanalyse.

2.1 Vorbereitung für die Analyse

Die Vorbereitung der DFM-Analyse ist sehr wichtig, sie ist die Grundlage aller Analysen und Voraussetzung dafür, ob die DFM-Analyse fortgesetzt werden kann. Die folgenden fünf Punkte sind die wichtigsten Vorbereitungen.

2.1.1 Output ODB++ data generated by PCB-Design durch EDA-Tool

ODB++ Daten sind ein branchenübliches Datenformat. Es kombiniert traditionelle Verarbeitungs- und Montagedaten wie PCB-Netzwerkinformationen, Stapelbeziehungen, Komponenteninformationen, Leiterplattenverarbeitungsinformationen, Materialinformationen und verschiedene Produktionsdaten einschließlich Platzierungsverfahren und Die Testverfahren usw. werden zusammen gesammelt. Erzeugt durch den ODB++ Datengenerator eingebettet in das EDA Design Tool. Bieten Sie vollständige und echte Inspektionsgrundlage für VALOR Trilogy 5000 DFM.

2.1.2 Eine vollständige Stücklistenliste basierend auf jedem PCB-Design

Das Lesen in der Stücklistenliste bedeutet, die Stücklistenliste des Leiterplattendesigns in ein Stücklistenformat zu organisieren, das vom VALOR Trilogy 5000-System erkannt wird und dem Hersteller und der VPL-Paketbibliothek jedes Geräts entspricht. Das Problem, das wir in der Massenproduktion (traditioneller PCB-Designprozess) begegneten, wenn wir der Stücklistenliste entsprachen, war, dass die automatisch von unserem EDA-Werkzeug generierte Stückliste mit dem Materialbeschaffungssystem des Unternehmens übereinstimmt und das Materialbeschaffungssystem für die Lesbarkeit ausgelegt ist. Der Name des Herstellers von Haushaltsgeräten spiegelt sich meist auf Chinesisch wider, und das Gerätemodell enthält normalerweise einige markierte Chinesisch. Für den Abgleich der Stücklistenliste in der VALOR Software kann die herstellerbezogene Verknüpfung nicht erreicht werden. Durch wiederholte Experimente, wenn man bedenkt, dass der Materialcode jedem Gerät entspricht, wird es nicht passieren, dass verschiedene Geräte einen Materialcode verwenden, der einzigartig ist. Daher setzen wir bei der Interpretation der Stückliste das Attribut des Materialcodes auf MPN (Manufactor Part Number) und setzen die Attribute der beiden Spalten des Herstellers und des Gerätemodells auf Describe und setzen das Codeattribut dieser Einheit auf Manufactor (Hersteller), es gibt nur einen Hersteller, der allen Gerätemodellen entspricht, was der Codename der Einheit ist. Nachdem dies implementiert ist, werden die Schritte der Entsprechung der Stücklistenliste stark vereinfacht und viele Probleme, die uns geplagt haben, wie ungenaue Herstellernamen und Nichterkennung in Chinesisch, die erzeugt wurden, wenn entsprechende Hersteller geschickt vermieden werden.

Der Prozess des Lesens in der Stückliste kann die Genauigkeit der PCB-Design-Stücklistenliste überprüfen und früh das Phänomen finden, dass das im PCB-Design verwendete Paket nicht mit der tatsächlichen Gerätebibliothek der Komponenten übereinstimmt, und einen Bericht über die Inspektionsergebnisse generieren, was für das PCB-Design wichtig ist. Sagte, es ist ein sehr guter vorläufiger Inspektionsprozess. Wenn das Stücklistenformat des Unternehmens sicher ist, kann der Prozess des Lesens der Stückliste durch Erstellen einer Vorlage wieder vereinfacht werden.

2.1.3 Aufbau einer VPL-tatsächlichen Verpackungsbibliothek basierend auf Unternehmensmaterialcodes

Verwenden Sie das VALOR Trilogy 5000 Bibliothekstool PLM, um die eigentliche Paketbibliothek jedes Geräts zu erstellen. Die VPL-Bibliothek enthält die Marke des Herstellers, Spezifikationen und die tatsächliche Packungsgröße der Komponenten. Die VPL-Bibliothek unterscheidet sich von der PCB-Design-Verpackungsbibliothek, es ist eine dreidimensionale Komponentenverpackungsbibliothek, die die tatsächliche Größe von Komponenten beschreibt.

Bei der Benennung der VPL-Paketbibliothek verwenden wir die VPL-Standardbenennungsmethode, fügen aber dem Paket-Attribut das Attribut U_PCB_PACKAGE hinzu und schreiben den Wert dieses Attributs in den EDA-Paketnamen. Der Vorteil: Wenn Sie bei der DFM-Analyse auf das Gerät klicken, auf das Sie achten möchten, können Sie intuitiv den Namen des EDA-Pakets sehen, das diesem Gerät entspricht, was den Standort und die Ansicht des betreffenden Pakets erleichtert und Zeit spart.

Die Einrichtung der VPL-Paketbibliothek ist ein Prozess der schrittweisen Akkumulation. Sie können mit Widerständen und Kondensatoren beginnen. Verwenden Sie die von VALOR bereitgestellte COPYPART-Software, um ein Paket von Widerständen oder Kondensatoren in einer Excel-Tabelle zu organisieren und die Stapelverarbeitung durchzuführen. Die VPL-Paketbibliothek aller Geräte in der Tabelle kann gleichzeitig erstellt werden. Von den Tausenden von Paketen in der EDA-Paketbibliothek von allgemeinen Einheiten sollten zwei Drittel von ihnen aus Widerständen und Kondensatoren bestehen. Wenn die oben genannten Methoden verwendet werden, sollten zuerst die Widerstände und Kondensatoren festgelegt werden, die eine solide Grundlage und Vertrauen für die Einrichtung der VPL-Bibliothek schaffen. Zweitens sollten einige wichtige Komponenten wie Steckverbinder und CPUs etabliert werden. Dadurch kann sichergestellt werden, dass nach der Montageanalyse jeder Leiterplatte zumindest die in Produktion gebrachte Leiterplatte nicht unbrauchbar erscheint; Zweitens sollte es etabliert werden Das VPL-Paket der teureren Geräte garantiert die erste Erfolgsrate der Leiterplatten mit wertvollen Geräten. Wenn die teuren Geräte während des Montageprozesses durch Verpackungsfehler beschädigt werden, ist dies ein großer Verlust für das Unternehmen. Richten Sie dann die VPL-Bibliothek mit häufig verwendeten Geräten ein. Da die VPL-Bibliothek schrittweise angereichert wird, wird die VPL-Bibliothek allmählich aufgebaut, so dass die meisten Leiterplatten auf Assemblierbarkeit analysiert werden können.

2.1.4 Definieren Sie die Eigenschaften des Geräts

Als Grundlage für alle Inspektionen ist die Einrichtung einer ERF-Regelverwaltungsdatenbank von entscheidender Bedeutung. In der eigentlichen Konstruktion und Produktion haben wir die Fertigungsspezifikationen der Leiterplattenhersteller gesammelt, die Konstruktions- und Produktionsprozess-Spezifikationen der Konstruktionseinheit sortiert, einzeln analysiert und verglichen und eine ERF-Regelmanagement-Datenbank eingerichtet, die unserem Unternehmen entspricht. Sie wird in der Praxis schrittweise verbessert. Die ERF-Regelverwaltungsbibliothek umfasst die Regelverwaltungsbibliothek Light Board Analyse und die Regelverwaltungsbibliothek Assembly Analyse.

2.2 Design für die Montage

Wenn das PCB-Layout der Leiterplatte grundsätzlich abgeschlossen ist:

1) ODB++ Daten importieren;

2) Importieren Sie die Stücklistenliste des Designs;

3) Rufen Sie die VPL-Ist-Verpackungsbibliothek und die ERF-Assembly-Analyse-Regelbibliothek entsprechend dem festgelegten Materialcode auf;

4) Entsprechend den unterschiedlichen Anforderungen an die Leiterplattenmontage richten Sie den entsprechenden Montageprozess ein und teilen Sie den Prozessbereich für die Leiterplatte auf;

5) Geräteattribute definieren;

6) Führen Sie Montageinspektion durch, generieren Sie visuelle Grafiken und generieren Sie automatisch Montageanalyseberichte.

Die Montage-Inspektion umfasst Inspektionen wie Komponentenverpackung, Markierungspunktinspektion, Komponentenanalyse, Pad-Analyse, Pad- und Pin-Korrespondenzanalyse, Testpunktanalyse und Schablonenöffnungsanalyse. Die oben genannten Kontrollpunkte umfassen alle Unterpositionen. Beispielsweise umfasst die Komponentenanalyse Komponentenabstand, Bauteilrichtung, Bauteilhöhe, Bauteilsiebsieb und verbotenen Bauteilbereich. Durch Inspektion kann festgestellt werden, dass die Komponenten und PCB-Pads nicht übereinstimmen, Komponentenkollisionsstörungen und Komponentenlötenprobleme.

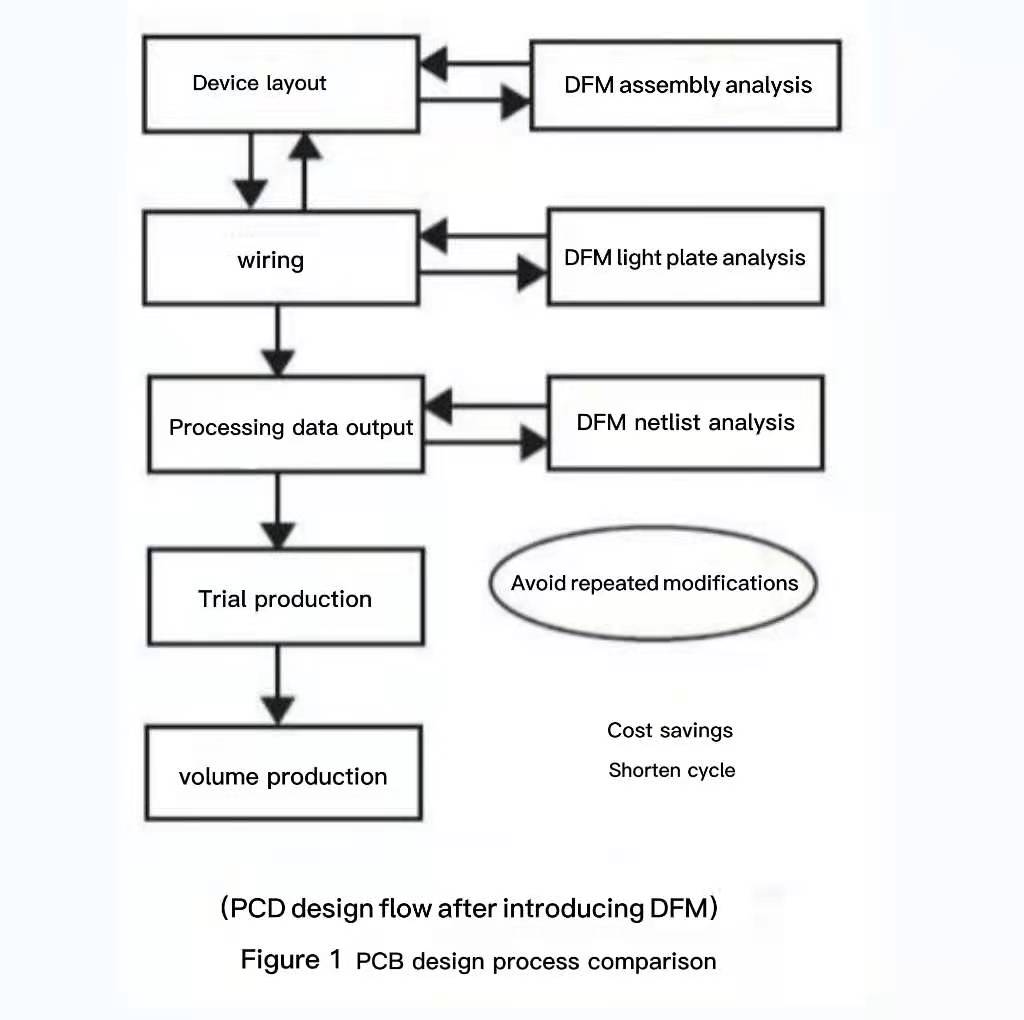

Mit der zunehmenden Komplexität der PCB-Design, eine Leiterplatte enthält Tausende von Geräten, und die zwischengeschalteten und oberflächenmontierten Geräte sind sehr dicht verteilt. Nachdem das Layout der Leiterplatte abgeschlossen ist, Das Anpassen des Siebdrucks verschiedener Geräte ist auch eine Menge Arbeit, und diese Art von komplizierter Arbeit wird unweigerlich zu einer unangemessenen oder sogar auf den Kopf gestellten Position des Tags führen. Die gewöhnliche EDA-Designsoftware bietet keine Prüfpunkte für diese Art von Problem, so sobald diese Art von Problem auftritt, Es wird oft nach dem Debuggen gefunden, nachdem die Leiterplatte verarbeitet und das Gerät installiert ist. Es brachte viel Ärger für die spätere Montage und Debugging, Verzögerung des Fortschritts der Produktforschung und -entwicklung, und brachte wirtschaftliche Verluste. Durch Bauteilanalyse, Das Problem der Bitzahlfehlausrichtung in Abbildung 2 kann leicht überprüft werden. Es ersetzt den manuellen Inspektionsprozess von PCB-Designers, Verbesserung der Effizienz, und garantiert die Qualität unserer PCB-Design. Diese Inspektion ist für unsere PCB-Design.

Abbildung 2 Bit Zahlenfehler

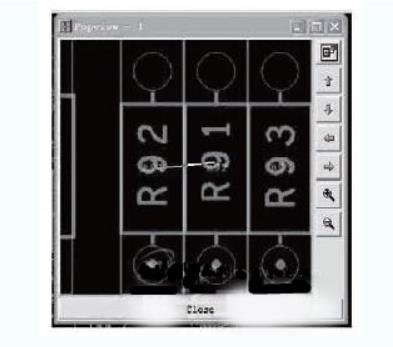

Die Bauteilabstandsanalyse bietet eine Methode zur Inspektion von zu engen Geräteabständen, die wir häufig beim Leiterplattendesign begegnen. Die Abstandsanforderungen zwischen verschiedenen Komponenten sind unterschiedlich, und die Höhe ist auch unterschiedlich, die durch die Korrespondenztabelle der ERF- und Geräteeigenschaften festgelegt werden kann. Durch Aufruf der VPL-Bibliothek analysieren wir, ob die unterschiedlichen Abstände verschiedener Komponenten den Anforderungen entsprechen. Wie in Abbildung 3 gezeigt, ist der Abstand zwischen den beiden Komponenten zu eng, was aufgrund des Höhenunterschieds der beiden Komponenten beim Wellenlöten zu unzureichendem Zinn an den Stiften kurzer Bauteile führt, was Leerlöten oder virtuelles Löten verursachen kann.

Abbildung 3 Der Abstand zwischen den beiden Komponenten ist zu eng

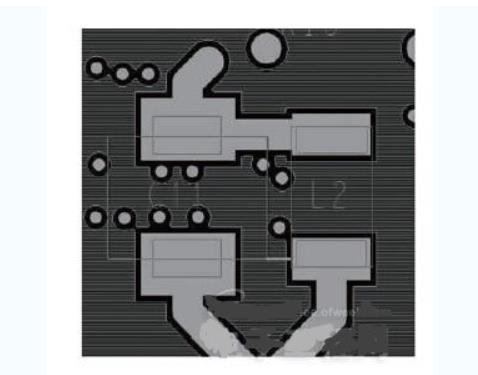

Die Komponentenverpackungsanalyse dient hauptsächlich dazu, die Richtigkeit der Komponentenverpackung auf der Leiterplatte zu überprüfen. Diese Inspektion ist besonders wichtig. Im PCB-Design verursacht der entsprechende Fehler des Komponentenpakets oder der Einrichtungsfehler der Paketbibliothek direkt, dass die bearbeitete Leiterplatte unbrauchbar ist, und sie muss neu produziert werden. Dies verschwendet nicht nur Kosten, reduziert die Effizienz, sondern verliert auch die Wettbewerbsfähigkeit des Marktes.

Wie in Abbildung 4 gezeigt, ist die graue Box die tatsächliche Gerätegröße der VPL-Bibliothek. Verglichen mit den schwarzen PCB-Designdaten unten ist es offensichtlich, dass das Verpackungspad-Design unangemessen ist, das Pad-Schweißteil zu kurz reserviert ist und die Pad-Breite nicht ausreicht, was leicht zu Schweißen während des Schweißvorgangs führt.

Durch die Anwendung der Assemblability-Analyse wird die Genauigkeit des PCB-Designs verbessert. Da wir viele Verarbeitungsanforderungen des verarbeitenden Herstellers in die ERF-Regeln aufgenommen haben, wurde die Anzahl der Hin- und Rück-Kommunikation mit dem verarbeitenden Hersteller reduziert und die Effizienz und die Ersterfolgsrate der Leiterplattenproduktion verbessert.

Abbildung 4 Unvernünftiges Pad Design

2.3 Netzlistenanalyse

Wenn die Leiterplattenlayout ist abgeschlossen, the ODB++ data generated during the design is extracted, und die Netzliste wird analysiert. Durch Vergleich des Standardnetzes, the design error (open circuit or short circuit) of the network integrity will be directly identified in der graph. Selbst der offene Stromkreis und Kurzschluss der Stromerde können durch den Inspektionsmodus, der in Pin-Point umgewandelt wird, genau gemeldet werden. Diese Funktion kann helfen PCB Inspektoren finden das Problem unvollständig PCB Inspektion aufgrund unzureichender Erfahrung, so dass PCB Inspektoren können die Integrität der endgültigen Konstruktionsdaten überprüfen, bevor das Produkt in Produktion genommen wird.

2.4 Light Board Analyse

Entpacken Sie gemäß ERF's Light Board Analysis Rule Management Library die ODB++ Daten, die durch das PCB Design generiert werden, um die Herstellbarkeit der PCB Light Board zu überprüfen. Leiterplattenanalyse umfasst hauptsächlich Bohranalyse, Signalanalyse, Leistungsschichtanalyse, Lötmaskenanalyse und Siebdruckanalyse.

Da verschiedene PCB-Designer unterschiedliche Designebenen und Methoden haben, sind im PCB-Designprozess aufgrund unterschiedlicher Erfahrungen die Regeln für die Einrichtung von Layout und Routing unterschiedlich und die Qualität des Designs ist auch sehr unterschiedlich. Wie die PCB-Qualität hergestellt wird, wird kontrolliert. Wir werden alle Design-Anforderungen und Spezifikationen bei den Inspektionen der Light Board Analyse berücksichtigen, indem wir die ERF Light Board Analyse Rule Management Bibliothek einrichten.

Zum Beispiel sollte im PCB-Design die Größe der wärmeisolierenden Frontplatte entsprechend den Leistungsanforderungen verschiedener Stromquellen eingestellt werden. Wenn die wärmeisolierende Frontplatte zu klein oder blockiert ist, verursacht sie eine zu schnelle Wärmeableitung während des Schweißens, schlechte Lötbarkeit und die Verbindung kann die Stromanforderungen usw. nicht erfüllen. Solange die PCB-Design-Software jedoch die Anforderungen an die Anschlussleitungsbreite erfüllt, wird kein Fehler angezeigt.

Wie in Abbildung 5 gezeigt, ist die wärmeisolierende Frontplatte zu klein. Die optische Panel-Analyse prüft entsprechend der Einstellung der ERF-Regeln, und die Klassifizierung fordert auf, ob sie die Anforderungen an Wärmeableitung und Anschlussleistung erfüllt und Fehler vermeidet, die durch Faktoren wie Erfahrung verursacht werden.

Anwendung der DFM-Technologie in PCB design

Abbildung 5 Die wärmeisolierende Frontplatte ist zu klein

Darüber hinaus bietet unser PCB-Design-Tool nur Inspektionselemente zwischen gedruckten Linien und Pads und bietet keine Inspektion des Abstands zwischen gedruckten Linien und Lötmaske. Wie in Abbildung 6 gezeigt, kann nach optischer Leiterplattenanalyse festgestellt werden, dass die gedruckten Linien zu nah an der Lötmaske sind, was das Kupferlecken der produzierten gedruckten Linien vermeidet, und die Oxidation von Kupfer wirkt sich direkt auf die Qualität des Signals aus. Diese Qualitätsprobleme, die nach längerem Gebrauch auftreten können, sollten auch berücksichtigt werden, wenn wir die Leiterplatte überprüfen.

Anwendung der DFM-Technologie im PCB-Design

Abbildung 6 Der Draht befindet sich zu nah an der Lötmaske

Wenn Sie in der Light Panel Analyse jeden Inspektionsschritt in eine Checkliste (Checkliste) kopieren, können Sie die Bedienung jeder Inspektion vereinfachen. Sie können auch Tastenkombinationen angeben, und Sie können Lichtpanelanalysen durchführen, indem Sie eine Taste drücken, was die Arbeitsbelastung der Inspektion erheblich reduziert.

2.5 Software-Synchronisation

Sobald die EDA-Datenbank als ODB++ gelesen wurde, kann Trilogy 5000 intelligente Grafiken zur Verbindung mit dem EDA-Tool bereitstellen. Mit den von der Software eingestellten Tastenkombinationen kann der Designer direkt vom Trilogy5000-Bildschirm mit dem gleichen Frame und Ort synchronisieren, der auf dem EDA-Tool angezeigt wird, was uns große Bequemlichkeit bietet, den Fehlerpunkt im EDA-Tool schnell und einfach zu finden.

3. Der Unterschied zwischen DFM-Software und PCB-Design-Software Regelprüffunktion

DFM-Software-Tools basieren auf tatsächlichen Produktionsregeln, während PCB-Design-Software-Prüfungen nur auf Design-Regeln basieren, die Werkzeuge in zwei verschiedenen Bereichen sind.

Die Analyse in der PCB-Design-Software wird im Allgemeinen auf die Konstruktionsabteilung angewendet, und die Daten werden am hinteren Ende des Designs überprüft, um sicherzustellen, dass es keine Probleme gibt, die gegen die elektrischen Regeln verstoßen und sich auf die Realisierung von Logikfunktionen konzentrieren; DFM wird auf die Prozessabteilung und die Produktionsmontageabteilung angewendet, um das Design sicherzustellen. Die Daten erfüllen alle Anforderungen der Herstellung, Montage und Prüfung.

Die Funktion der Herstellbarkeitsanalyse von verwandten Modulen in PCB-Design-Software ist relativ einfach, und die Regeln sind nicht reich genug. Tools wie Assemblability Analysis und Testability Analysis sind nicht verfügbar.

4. Schlussfolgerung

DFM Software bietet uns eine umfassende PCB-Design Prüfprogramm zur Automatisierung, which makes unsere products more standardized. Auch mit anderen PCB-Design Software und PCB-DesignPersonen mit unterschiedlichen Erfahrungen, die Qualität der von PCB-Designer ist garantiert. Prozessüberprüfung parallel an allen Phasen des Produktdesigns teilnehmen, Lösen und entdecken Sie alle verborgenen Qualitätsrisiken in der Konstruktionsphase, und die Qualität unserer PCB-Design. Die Effizienz der Leiterplattenbearbeitung, Prozessmanagement und Elektrogeräteprozess wurden stark verbessert, die Qualität des Produkts wurde verbessert, die Kosten für das Produkt und der Entwicklungszyklus wurden reduziert, und die Wettbewerbsfähigkeit des Produkts wurde erhöht.

Darüber hinaus fördert der Einsatz von DFM-Software auch die Standardisierung von Prozessen. Durch DFM-Spezifikationen sind die Konstruktions- und Fertigungsabteilungen organisch miteinander verbunden und gleichzeitig wird die Standardisierung der Produktionsprüfgeräte erreicht. Basierend auf dem aktuellen Trend des Outsourcings der Produktherstellung wird es möglich sein, den spezialisierten Transfer der Produkttechnologie zu realisieren, der der Realisierung einer größeren Entwicklung von Unternehmen förderlich ist.