Was sind die technologischen Schwierigkeiten von hochpräzisen Mehrschichtplatinen

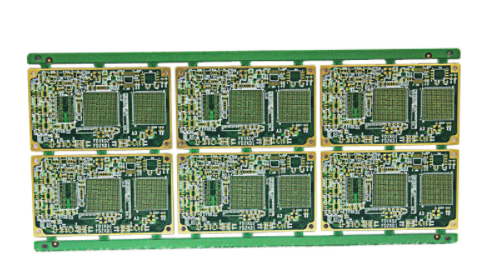

Mit der Entwicklung der Hochtechnologie, mehrschichtig Leiterplatten sind zur "Kernkraft" in den Bereichen Kommunikation geworden, medizinische Behandlung, industrielle Steuerung, Sicherheit, Automobile, Strom, Luftfahrt, Militärindustrie, und Computerperipherie in der Elektronikindustrie, und die Produktfunktionen werden immer höher., Leiterplatten werden immer anspruchsvoller, so wird es immer schwieriger zu produzieren.

1. Schwierigkeiten bei der Herstellung der inneren Linie

Leiterplatten mit mehreren Schichten besondere Anforderungen an hohe Geschwindigkeiten haben, dickes Kupfer, Hochfrequenz, und hoher Tg-Wert. Die Anforderungen an innere Schichtverdrahtung und grafische Größensteuerung werden immer höher. Zum Beispiel, Das ARM Development Board hat viele Impedanzsignalleitungen in der inneren Schicht. Um die Integrität der Impedanz sicherzustellen, erhöht sich die Schwierigkeit der Herstellung der inneren Schichtschaltung.

Es gibt viele Signalleitungen in der inneren Schicht, und die Breite und der Abstand der Linien sind im Grunde etwa 4mil oder weniger; Die dünne Produktion von Mehrkern-Leiterplattenschichten ist anfällig für Falten, Diese Faktoren erhöhen die Produktion der inneren Schicht.

Empfehlung: Die Linienbreite und der Linienabstand sind auf 3 ausgelegt.5/3.5mil or more (most circuit board factories have no difficulty in production).

Zum Beispiel, eine sechsschichtige Leiterplatte, Es wird empfohlen, ein gefälschtes achtschichtiges Strukturdesign zu verwenden, das die Impedanzanforderungen von 50ohm erfüllen kann, 90ohm, und 100ohm mit 4-6mil Linienbreite in der inneren Schicht.

2. Difficulties in alignment between inner layers

There are more and more layers of multi-layer circuit boards, und die Ausrichtungsanforderungen der inneren Schichten werden immer höher. Die Folie dehnt sich aus und zieht sich unter dem Einfluss der Temperatur und Feuchtigkeit der Werkstattumgebung zusammen, und die Kernplatte hat die gleiche Ausdehnung und Kontraktion, wenn produziert, was die Kontrolle der Ausrichtungsgenauigkeit zwischen den inneren Schichten erschwert.

3. Difficulties in the pressing process

The superposition of multiple core plates and PP (cured plate) is prone to problems such as delamination, Gleitplatte und Dampftrommelrückstände beim Pressen. Im strukturellen Entwurfsprozess der inneren Schicht, Faktoren wie dielektrische Dicke zwischen den Schichten, der Leimfluss, und die Hitzebeständigkeit der Platte sollte berücksichtigt werden, und die entsprechende laminierte Struktur sollte vernünftig ausgelegt sein.

Tipp: Halten Sie die innere Kupferschicht gleichmäßig verteilt, und das Kupfer in einer großen Fläche ohne die gleiche Fläche mit der gleichen Balance wie PAD verteilen.

4. Schwierigkeiten bei der Bohrproduktion

Leiterplatten mit mehreren Schichten Verwenden Sie hohe Tg oder andere spezielle Platten, und die Rauheit der Bohrlöcher verschiedener Materialien ist unterschiedlich, was die Schwierigkeit erhöht, die Schlacke im Loch zu entfernen. Mehrschichtige Leiterplatten mit hoher Dichte haben eine hohe Lochdichte und niedrige Produktionseffizienz, die leicht zu brechen ist. Zwischen den Durchgangslöchern verschiedener Netzwerke, Die Kante des Lochs ist zu nah, um das CAF-Effekt-Problem zu verursachen.

Empfehlung: Der Abstand der Lochkanten verschiedener Netze beträgt â0.3mm.