Jemand hat gesagt, dass es nur zwei Arten von Elektronikern auf der Welt gibt: diejenigen, die elektromagnetische Störungen erlebt haben und diejenigen, die keine elektromagnetische Störung erfahren haben. Mit der Zunahme von Leiterplattenführungsgeschwindigkeit, Das Design der elektromagnetischen Verträglichkeit ist ein Thema, das unsere Elektroniker berücksichtigen müssen. Angesichts eines Entwurfs, bei der Durchführung einer EMV-Analyse eines Produkts und Designs, Folgende fünf wichtige Attribute sind zu berücksichtigen:

(1) Schlüsselgerätegröße: die physikalische Größe des emittierenden Geräts, das Strahlung erzeugt. Der Hochfrequenzstrom erzeugt ein elektromagnetisches Feld, das durch das Gehäuse undicht und das Gehäuse verlässt. Die Länge der Leiterbahn auf der Leiterplatte als Übertragungsweg hat einen direkten Einfluss auf den HF-Strom.

(2) Impedanz Matching: die Impedanz der Quelle und des Empfängers und die Übertragungsimedanz zwischen den beiden.

(3) Die Zeitcharakteristik des Störsignals: Ist das Problem ein kontinuierliches (periodisches Signal) Ereignis oder existiert nur in einem bestimmten Betriebszyklus (z. B. eine einzelne Schlüsseloperation oder Einschaltstörung, periodischer Festplattenlaufwerksbetrieb oder Netzwerkburstübertragung).

(4) Die Stärke des Störsignals: wie stark ist das Quellenergieniveau und wie viel Potenzial es hat, schädliche Störungen zu erzeugen.

(5) Frequenzmerkmale des Störsignals: Verwenden Sie einen Spektrumanalysator, um die Wellenform zu beobachten, und wo das beobachtete Problem im Spektrum liegt, ist es leicht, das Problem zu finden.

Darüber hinaus benötigen einige niederfrequente Schaltungsdesigngewohnheiten Aufmerksamkeit. Zum Beispiel ist meine übliche Einpunkt-Erdung sehr geeignet für niederfrequente Anwendungen, aber später wurde sie als ungeeignet für HF-Signal-Gelegenheiten gefunden, da es mehr EMI-Probleme bei HF-Signal-Gelegenheiten gibt. Ich glaube, dass einige Ingenieure Single-Point-Erdung auf alle Produktdesigns anwenden, ohne zu wissen, dass die Verwendung dieser Erdungsmethode mehr oder komplexere Probleme mit der elektromagnetischen Verträglichkeit verursachen kann.

Wir sollten auch auf die Richtung des Stromflusses innerhalb der Schaltungskomponenten achten. Mit Schaltungswissen wissen wir, dass Strom von einem Ort fließt, an dem die Spannung hoch ist, zu einem Ort, an dem die Spannung niedrig ist, und der Strom fließt immer in einem geschlossenen Kreislauf durch einen oder mehrere Pfade, also eine Mindestschleife und ein sehr wichtiges Gesetz. Für die Richtungen, in denen der Störstrom gemessen wird, werden die Leiterplatten-Leiterbahnen so modifiziert, dass sie die Last oder empfindliche Schaltungen nicht beeinflussen. Anwendungen, die einen hochohmigen Weg von der Stromversorgung zur Last erfordern, müssen alle möglichen Wege berücksichtigen, durch die der Rückstrom fließen kann.

Es gibt auch das Problem der Leiterplattenrouting. Die Impedanz eines Drahtes oder einer Leiterbahn umfasst Widerstand R und induktive Reaktanz. Bei hohen Frequenzen, die Impedanz hat keinen kapazitiven Reaktanz. Wenn die Leiterbahnfrequenz höher als 100kHz ist, der Draht oder die Spur wird Induktivität. Drähte oder Leiterbahnen, die über Audio arbeiten, können zu Hochfrequenzantennen werden. In der EMV-Spezifikation, Drähte oder Leiterbahnen dürfen unter Î nicht arbeiten"/20 of a certain frequency (the design length of the antenna is equal to λ/4 oder Î"/2 of a certain frequency). Wenn das Design nicht sorgfältig ist, Die Verkabelung wird zu einer Hochleistungsantenne, which makes the later debugging more difficult

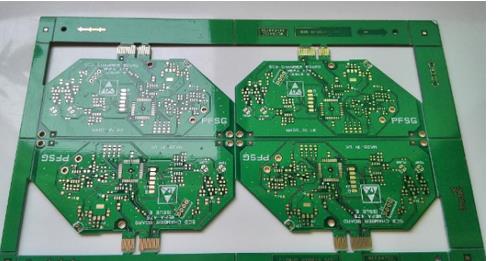

Finally, über die Leiterplattenlayout. Erstens, die Größe der Leiterplatte berücksichtigen. Wenn die Größe der Leiterplatte zu groß ist, Die Anti-Interferenz-Fähigkeit des Systems sinkt und die Kosten steigen mit der Zunahme der Spuren, und die zu kleine Größe verursacht leicht Wärmeableitung und gegenseitige Interferenzprobleme. Zweiter, determine the location of special components (such as clock components) (the clock traces are best not to be grounded and not to walk above and below the key signal lines to avoid interference). Drittens, Layout der Leiterplatte als Ganzes nach Schaltungsfunktionen. Im Bauteillayout, die zugehörigen Komponenten sollten so nah wie möglich sein, so dass eine bessere Anti-Interferenz-Wirkung erzielt werden kann.