A, PCB-Simulation und DDR3 Speicherdesign

1 Überblick Die heutige DDR3-Speichertechnologie des Computersystems wurde weit verbreitet, und die Datenübertragungsrate wurde wiederholt gefördert, und jetzt ist sie so hoch wie 1866Mbps.

Unter der Bedingung dieser Art von Hochgeschwindigkeitsbus, um die Zuverlässigkeit der Datenübertragungsqualität zu gewährleisten und die zeitlichen Anforderungen des Parallelbusses zu erfüllen, stellt es eine große Herausforderung an das Design und die Implementierung dar.

Dieser Artikel verwendet hauptsächlich Cadences Zeitbereichsanalysetool, um das DDR3-Design quantitativ zu analysieren, stellt die Hauptfaktoren vor, die die Signalintegrität der DDR3-Timing-Analyse beeinflussen, und verbessert und optimiert das Design durch die Analyse der Ergebnisse, um die Signalqualität zu verbessern. Seine Zuverlässigkeit und Sicherheit werden erheblich verbessert.

2 Einführung in DDR3 DDR3-Speicher ist ähnlich wie DDR2-Speicher, einschließlich 2-Controller und Speicherteile, die alle Quellsynchrones Timing verwenden, das heißt, das ausgewählte Signal (Takt) wird nicht von einer separaten Taktquelle gesendet, sondern vom Treiberchip.

Es hat eine höhere Datenübertragungsrate als DR2, bis zu 1866MBPS; DDR3 verwendet auch 8-Bit Prefetch-Technologie, die die Speicherbandbreite erheblich erhöht, und seine Betriebsspannung beträgt 1,5V, was einen reduzierten Stromverbrauch bei gleicher Frequenz gewährleistet. DDR3 Interface Design ist schwierig zu erreichen. Es verwendet eine einzigartige Fly-by-Topologie und verwendet die "Write Equalization"-Technologie, um das interne Offset-Timing des Geräts und andere effektive Maßnahmen zu steuern.

Obwohl es eine Rolle bei der Gewährleistung der Designimplementierung und Signalintegrität spielt, ist das Speichersystem, das hohe Frequenz und Bandbreite erreicht, nicht umfassend. Daher ist eine Simulationsanalyse notwendig, um die Integrität der Designimplementierung und Signalqualität sicherzustellen.

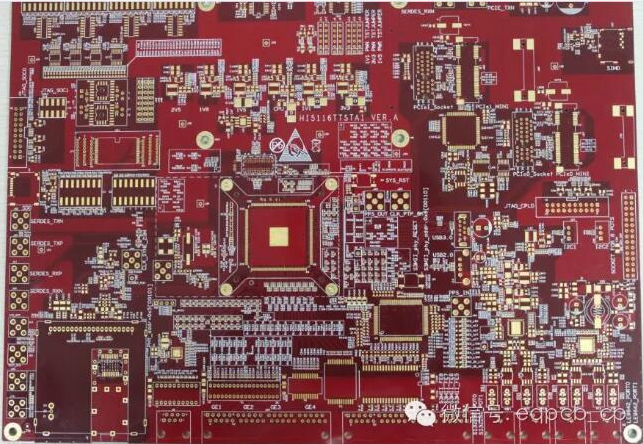

3 Simulationsanalyse DDR3 Simulationsanalyse kombiniert mit dem Projekt zu erklären: Wählen Sie PowerPC 64-Bit Dual-Core CPU Modul, dieses Modul verwendet Microns MT41J256M16HA-125IT für Speicher.

Bei der Analyse des Prozessors von P5020 ist das Modul mit einer Speicherbus-Datenübertragungsrate von 1333MT/s und einer analogen Frequenz von 666MHz konfiguriert.

3.1 Vorbereitung vor der Simulation Vor der Analyse, Es ist notwendig, mit dem Leiterplattenhersteller basierend auf der Impedanz von DDR3 zu kommunizieren, um seine laminierte Struktur zu bestätigen. Der Schlüssel zur Sicherstellung der Leistung der Übertragungsleitung bei Hochgeschwindigkeitsübertragung ist die kontinuierliche charakteristische Impedanz. Bestimmung der Impedanzsteuerung der Hochgeschwindigkeits-PCB-Signal Linie innerhalb eines bestimmten Bereichs, so dass die Leiterplatte zu einer "steuerbaren Impedanzplatte" wird, die Grundlage der analogen Analyse ist.

Die Einzelleitungsimpedanz des DDR3-Busses ist 50Ω, und die differentielle lineare Impedanz ist 100Ω. Stellen Sie den Spannungswert der Analyse-Netzwerkklemme, einschließlich des passiven Gerätezuordnungsmodells des analysierten Geräts, bestimmen Sie die Gerätetypattribute und stellen Sie die Gerätepin-Attribute sicher (Eingang und Ausgang, Stromerdung, etc.)......

Zweitens lösen Sie schnell die Signalintegrität im PCB-Hochgeschwindigkeitssystem

Lösen Sie schnell Signalintegritätsprobleme in PCB-Hochgeschwindigkeitssystemen. Mit der Zunahme der Datenraten sind Signalintegritätsprobleme zum kritischsten Faktor geworden, der von Konstrukteuren berücksichtigt wird. Dieser exponentielle Anstieg der Datenraten zeigt sich in Anwendungen wie Routern/Switches mit hoher Bandbreite wie mobilen Handheld-Geräten und Consumer Display-Produkten. Jitter (Rauschen) ist der Hauptgrund für die Reduzierung der Signalintegrität im Design. Neben der Verwendung von Layout, Impedanzanpassung und teureren Materialien, um Signalintegritätsverbesserungstechnologie zu erreichen, können Designer dem Design auch einfach Jitter-Empfänger wie Equalizer hinzufügen, um das Jitter-Problem zu lösen.

Auf diese Weise müssen sich Designer nicht auf Probleme der Signalintegrität konzentrieren, sondern auf das Kerndesign des Systems. Signalverdrahtung wurde in der Vergangenheit oft als einfaches Konzept angesehen, und es gibt keinen Unterschied zwischen Videosignalen, Sprachsignalen oder Datensignalen aus der Sicht der Verkabelung. Daher kümmerten sich in der Vergangenheit nur wenige Menschen um Signalverdrahtung. Nun hat sich die Situation jedoch völlig verändert. Die Videosignal-Übertragungsgeschwindigkeit hat jetzt 3.3Gbps pro Kanal erreicht, und das Datensignal übertrifft 5Gbps pro Kanal weit.

Serielle Hochgeschwindigkeitsstandards wie PCI Express, XAUI, SATA, TMDS und Display Port erfordern von Designteams und Ingenieuren nicht nur die Berücksichtigung von Problemen mit der Signalintegrität, sondern auch ein tiefes Verständnis dafür, wie sich dies auf die Systemleistung und Zuverlässigkeit auswirkt. Um dieses Wissen zu beherrschen, müssen Ingenieure zunächst die Faktoren verstehen, die die Signalintegrität im System beeinflussen. Der Verlust der Signalintegrität im System kann durch Erhöhung des Signaljitters beobachtet werden. Der Gesamtjitter des Systems besteht hauptsächlich aus zwei Arten von Jitter, nämlich zufälligem Jitter und deterministischem Jitter. Zufälliger Jitter ist unendlich und folgt im Grunde der Gaußschen Verteilung, während deterministischer Jitter endlich und vorhersehbar ist.

In 90% von Systemen ist deterministischer Jitter das wichtigste Problem der Signalintegrität, das Konstrukteure lösen müssen. Deterministischer Jitter umfasst Codeinterferenzen (ISI), Lastzyklusverzerrungen und periodischen Jitter, die durch Bandbreitenbegrenzungsprobleme, Taktzyklusasymmetrie und Kreuzkopplungs- bzw. EMI-Probleme verursacht werden.

Passive Komponenten wie Steckverbinder, Leiterplattenverdrahtung, lange Kabel und andere passive Komponenten entlang der Verdrahtung sind die wichtigsten Quellen für deterministischen Jitter. Je höher die Signalfrequenz, desto größer die Dämpfung, so dass der Leistungspegel im angegebenen Datenstrom nicht übereinstimmt, und diese Leistungspegelfehlübereinstimmung führt zu ISI im Signal.

ISI verringert die Signalintegrität, was ausreicht, um zu verhindern, dass der Empfänger tatsächliche Daten aus dem Signal am Empfangsende korrekt extrahiert. Der Grund für den Leistungspegelunterschied liegt darin, dass kein Konstrukteur die Datenübertragung im Design garantieren kann. Die Daten können sich ständig ändern (0-1-0-1-0-1-0-1, etc.) oder konstant (1-1-1-1-1-1-1, etc.). Offensichtlich ist das Duty-Free-Verhältnis der oben genannten 6-Wechselbits 6-mal das Duty-Verhältnis des 6"1"-konstanten Datenstroms. Da das Duty-Free-Verhältnis 6-mal kleiner ist, ist die Signalfrequenz 6-mal höher.

Wenn der Datenstrom diese beiden Typen enthält, hat das Empfängersignal sehr unterschiedliche Leistungsniveaus, denn je höher die Frequenz, desto größer die Dämpfung.

Die meisten Hochgeschwindigkeitssignalstandards schreiben vor, dass die Anzahl der kontinuierlichen Bits ohne Änderung minimiert werden sollte, z. B. 8B/10B-Kodierung. Dieses Codierungsschema stellt sicher, dass der Datenstrom vier aufeinanderfolgende Bits nicht überschreitet.

Es ist jedoch weiterhin möglich, den hohen Leistungsanteil des Empfängersignals zu vervierfachen. Um den Leistungspegelmissbrauch auszugleichen, um ISI zu reduzieren, können PCB-Designer Equalization- oder De-Empreciation-Techniken verwenden.

Die PCB-Ausgleichstechnologie erhöht die Leistung aller Hochgeschwindigkeitsbilder, so dass die empfangenen Signale in den Hochgeschwindigkeits- und Low-Speed-Bits den gleichen Leistungspegel haben, dadurch verminderte Leistungsunterschiede. Das Gegenteil von einer Verschärfung des Gleichgewichts, Aber das Ziel ist dasselbe: Minimierung des Leistungspegels Missmatch. Es wird getan, indem die Leistung des Low-Speed-Bits reduziert wird, die die Leistung des Hochgeschwindigkeitsbißes erhöhen wird.