Bei der Durchführung eines Online-Funktionstests an einem Leiterplattenbusgerät ((wie 74245)), Der Test schlägt fehl, weil sein bidirektionaler Eingang/Ausgangspins können von anderen Geräten beeinflusst werden, die über den Bus mit ihm verbunden sind. Das Busgerät kann sich nach dem Einschalten der getesteten Platine im eingeschalteten Zustand befinden, so dass seine Ausgabe/Input Pins befinden sich nicht im Tri-State High Impedanz Zustand. Testen Sie das Ergebnisfenster, wenn Buskonflikte im Testbusgerät auftreten. Um den Einfluss des Busstreits zu beseitigen und den Test des getesteten Chips zu bestehen, der Benutzer muss die zugehörigen Busgeräte isolieren.

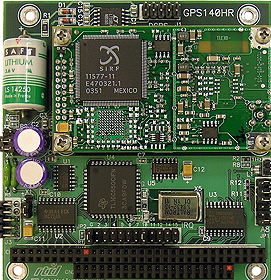

Ein Testergebnis zeigte, dass der dritte, vierte und neunte Pins von 74245 nicht kippten und der Test fehlschlug. Zu diesem Zeitpunkt sollte der Benutzer die dynamische Impedanz jedes Pin des Chips vom Pin-Status überprüfen, um festzustellen, ob es einen Pin gibt, der zur Masse kurzgeschlossen ist oder einen sehr niedrigen Widerstand zur Masse hat (weniger als 5 Ohms). Im oberen rechten Bild können Sie feststellen, dass die Impedanz der elften, 16ten und 17ten Pins zur Masse etwa 290 Ohms beträgt und die Impedanz der anderen Ausgangs- und Eingangspins zur Masse zwischen 17-23 Ohms liegt. Ersteres zeigt an, dass sich der Pin in einem logischen High-Zustand befindet, und letzteres zeigt an, dass sich der Pin in einem logischen Low-Zustand befindet. Der zweite Pin bestand den Test und war nicht von Buskonflikten betroffen, da sein Ausgangspin dem Pull-Down-Effekt des angeschlossenen Geräts standhalten kann.

Der Anwender muss unterscheiden können, ob der Prüffehler durch Buskonflikte oder durch beschädigte Gerätefunktionen verursacht wird. In diesem Beispiel ist der Grund für den Testausfall Buskonflikt. Um einen vollständigen Test am Gerät durchzuführen, muss der Benutzer das entsprechende Busgerät isolieren und seinen Ausgangspin in einem hochohmigen Zustand machen, ohne das zu prüfende Gerät zu beeinträchtigen.

Wenn der dritte Pin des Chips als Ausgangspin verwendet wird, wird er vom angeschlossenen Chip heruntergezogen und kann nicht umgedreht werden. Wenn Pin 3 als Eingangspin verwendet wird, da der maximale Antriebsstrom von QT200 650 mA beträgt, selbst wenn Pin 3 von anderen Chips heruntergezogen wird, kann QT200 Pin 3 immer noch auf ein hohes Potenzial ziehen, so dass Pin 17 getestet werden kann. Wenn die Funktion des Chips beschädigt ist, ist es zu diesem Zeitpunkt unmöglich, den Ausgangstest am Pin 17 zu bestehen.

Das tatsächliche Testergebnis ist, dass der 17-Pin-Ausgangstest bestanden hat, offensichtlich ist die Funktion des Chips nicht beschädigt, aber das Problem des Busstreits.

Wie kann festgestellt werden, welcher Chip PCB-Bus-Streit verursacht und isoliert werden muss?

Wenn der Benutzer den Schaltplan der getesteten Platine hat, finden Sie zuerst alle anderen Buschips heraus, die an den getesteten Chip angeschlossen sind. Normalerweise können die Buschips in der Schaltung in die folgenden drei Kategorien unterteilt werden:

a, die Enable-Klemme ist mit der Ausgangsklemme anderer Chips verbunden;

b. Die Enable-Klemmen von zwei oder mehr Buschips sind angeschlossen;

c. Die Enable-Klemme ist direkt mit der Masse oder +5v Stromversorgung verbunden.

Für den ersten Buschip-Typ sollte die Isolierung für jedes Aktivierungsterminal eingestellt werden, indem der entsprechende Logikpegel auf dem Flugleitkanal von QT200 (von FC0 bis FC7) eingestellt wird und dann an diese Aktivierungsterminals angeschlossen werden; Für Buschips ist nur ein Isolationskanal vorgesehen, der mit der Enable-Klemme eines der Chips verbunden ist; Für den dritten Typ von Buschips können Isolationseinstellungen nicht direkt durchgeführt werden, da der Isolationskanal keinen Rückwärtsantrieb auf seiner Enable-Klemme implementieren kann. Das allgemeine Verarbeitungsprinzip besteht darin, die ersten beiden Arten von Buschips zuerst einzustellen, um zu sehen, ob die Testergebnisse des geprüften Chips zufriedenstellend sind (d.h. die Qualität des Chips kann anhand der Ergebnisse beurteilt werden), wenn dies der Fall ist, wird die Isolierung des dritten Buschips nicht berücksichtigt; Wenn immer noch unzufrieden, und dann Maßnahmen ergreifen, um die dritte Art von Bus-Chip zu isolieren. Im Allgemeinen wird das Secant-Verfahren verwendet, um das Enable-Terminal von der Masse- oder +5V-Stromversorgung zu trennen und es dann zu isolieren.

Testen Sie den Chip erneut, nachdem Sie den Isolationspunkt eingestellt haben. Wenn der Test bestanden hat, entfernen Sie die eingestellten Isolationskanäle nacheinander und testen Sie erneut. Wenn der Test fehlschlägt, ist der Bus-Chip, dessen Isolationseinstellung entfernt wird, der Chip, der Buskonflikte erzeugt. Schließen Sie den Isolationskanal des Chips wieder an und überprüfen Sie weiterhin andere unbestimmte Buschips gemäß der obigen Methode. Bis zum letzten finden Sie alle Bus-Chips heraus, die isoliert werden müssen (starten Sie im Board-Lernmodus den Notizblock, notieren Sie, welche Chips für den Test von welchen Bus-Chips isoliert werden müssen, was bei der Reparatur des defekten Boards eine große Hilfe sein wird).

Wenn der Benutzer keinen Schaltplan hat, kann er mit dem Scan-Test im QSM/VI-Testverfahren weitere Buschips herausfinden, die mit dem zu prüfenden Chip verbunden sind. Die spezifische Methode ist: Geben Sie direkt das interaktive QSM/VI-Testfenster aus dem ICFT-Testmodus ein, passen Sie einen Namen des zu prüfenden Chips an, stellen Sie die Anzahl der Pins auf 40, die Messfrequenz auf 312Hz und verwenden Sie das QT200-Kabel für die Schaltungsverfolgung (es gibt zwei A 20-polige Vorrichtung), Verbinden Sie Befestigung 1 mit dem Buschip unter Funktionstest (der erste Stift der Befestigung steht dem ersten Stift des Chips gegenüber) und schließen Sie Befestigung 2 mit jedem anderen Buschip auf der getesteten Platine an und starten Sie dann den Scan-Test. Wenn zwischen den beiden Chips eine Verbindung besteht, wird diese in einem Fenster auf dem Bildschirm angezeigt. Unter ihnen repräsentieren Pins 1-20 den Chip, der mit der Vorrichtung 1 verbunden ist, und Pins 21-40 den Chip, der mit der Vorrichtung 2 verbunden ist. Wenn der fünfte Pin und der 35te Pin im Fenster mit dem L1-Symbol markiert sind, bedeutet dies, dass der fünfte Pin des ersten Chips mit dem fünften Pin des zweiten Chips verbunden ist.

Wie kann man die digitale Oszilloskopfunktion des Systems nutzen, um die Qualität der Busgeräte zu beurteilen?

Wenn beim Testen von Busgeräten die Qualität des Gerätes nicht isoliert beurteilt werden kann, können Sie die neueste Funktion dieses System-Digital Oszilloskops (DSO) zum Testen verwenden. Die grundlegende Arbeitsweise ist wie folgt:

Lösen Sie die Kristalle, die auf der zu prüfenden Leiterplatte gelötet wurden, auf, damit die Platine eine normale Uhr läuft.

Verbinden Sie den Prüfkopf mit dem entsprechenden Kanal (Hinweis: der gewählte Messkanal ist für verschiedene Versionen der Systemsoftware unterschiedlich)

Drücken Sie die DSO-Taste aus der Symbolleiste im Testfenster, um den digitalen Oszilloskop-Modus zu starten.

Schalten Sie das Netzteil der getesteten Leiterplatte

Verbinden Sie die Sonden wiederum mit verschiedenen Pins des getesteten Busgeräts, und Sie können das tatsächliche Signal des getesteten Pins auf dem Bildschirm sehen. Wechselt das Signal von hoch nach niedrig, so funktioniert der Pin normal. Wenn das Signalpotential zwischen 2v und 1.8v festgelegt ist, sollte dem Pin besondere Aufmerksamkeit geschenkt werden. Dies kann daran liegen, dass die Funktion des Pins beschädigt ist, oder der Pin ist ein Ausgangspin in einem offenen Schaltungszustand. Zu diesem Zeitpunkt kann der 7404-Chip in der Nähe des Kristalls erkannt werden, da dieser Chip häufig in Taktschaltungen verwendet wird. Testen Sie den Ausgangspin von 7404 mit einer Sonde, es sollte ein Wellenformsignal geben â . Wenn nicht, überprüfen Sie, ob die Stromversorgung der getesteten Leiterplatte normal ist und ob der Kristall beschädigt ist. Beachten Sie, dass das Oszilloskop beim Erfassen des Taktsignals 100K Impedanz auswählen sollte, um den Einfluss auf die Kristalloszillatorschaltung zu vermeiden.

Um zu erkennen, ob sich der Pin im schwimmenden Zustand befindet, Die Impedanz des Oszilloskops kann als 10K gewählt werden. If the pin is indeed floating (its impedance is greater than 1 megaohm), dann, wenn die Sonde den Stift berührt, Die 10K Impedanz zieht den Stift auf ein niedriges Niveau. Wenn der Stift nicht schwebend bleibt, hat aber einen festen Pegel, die Sonde wird nicht tief ziehen. Aus diesem, der wahre Zustand der Leiterplattenstifte kann beurteilt werden.