Technologie d'interconnexion pour puces encapsulées de circuits intégrés haute performance et haute fiabilité

Orientation du marché des composants électroniques (pour circuits imprimés PCBA)

Pour les technologies éprouvées de LSI avec un degré élevé d'intégration et de vitesse, il est nécessaire de développer, le cas échéant, des techniques d'isolation utilisant des matériaux à faible K. Mais pour répondre aux hautes performances de ces cellules, les couches d'isolation deviennent de plus en plus minces grâce aux structures poreuses et multicouches. En conséquence, le LSI devient vulnérable. D'autre part, le courant du LSI augmente constamment pour répondre aux exigences de vitesse élevée. En plus de la taille des puces allant du grand au petit, la densité thermique et la consommation d'énergie augmentent également. Pour les futurs substrats d'encapsulation semi - conducteurs (IC Substrate Encapsulation), il est donc nécessaire de résoudre ces problèmes, à savoir la fragilité du milieu inter - couches, la chaleur élevée, la vitesse élevée et le faible coût. Les futurs préréglages pour le processus de semi - conducteur seront à 20 nm et au - dessous, ce qui sera beaucoup plus faible.

Technologie d'encapsulation requise pour la génération 20nm

Les spécifications requises pour la prochaine génération de 20nm sont:

Faible contrainte de la couche K faible fragile

Rayonnement thermique élevé 5W pour LSI haute performance

Haute vitesse 10ghz pour des fonctions élevées

Direction de développement de l'emballage semi - conducteur

Pour s'adapter à la croissance fonctionnelle et à la réduction des coûts des appareils électriques, y compris les appareils mobiles, les règles de préréglage de Wafer évoluent vers des règles de préréglage plus grandes et plus fines. Pour ce faire, et afin de réduire les coûts, la technologie d'encapsulation semi - conductrice passe rapidement de la technologie de collage de fil d'or la plus standard à la technologie de collage de fil de cuivre, ce qui réduit la quantité d'or utilisée. En outre, l'utilisation de la technologie Flip - chip Bonding répond grandement aux niveaux d'intégration et de performance plus élevés de LSI. En 2010, le collage inversé sur puce représentait 15% de la technologie mondiale d'encapsulation des semi - conducteurs et le collage par fil 85%. D'ici 2015, la part du collage par puce inversée devrait atteindre 25% et celle du collage par fil devrait atteindre 75%. En particulier pour les LSI haute intégration et haute performance nécessitant un rayonnement thermique élevé et des vitesses de signal élevées, la technologie de collage par puce inversée est activement considérée comme appropriée.

Technologie de puce inversée de bon sens

Convient pour faible K

Technologie de puce inversée couramment utilisée:

. souder les côtés adjacents, la structure principale est C4 (conception collaborative de la puce de sédimentation contrôlable)

. pour le sertissage de type au - bosse et ACF

Collage ultrasonique pour signature de type au - au

Le collage par pression et le collage par ultrasons imposent des pressions élevées et des oscillations mécaniques au LSI, de sorte que ces méthodes ne peuvent pas être utilisées avec un LSI à faible K. Ainsi, dans le procédé décrit ci - dessus, le C4 peut être utilisé de manière appropriée et, grâce à la comparaison des trois procédés, la combinaison est cohérente avec le fait que le C4 nuit le moins à la puce.

La technologie C4 est née au début des années 40 pour les ordinateurs à usage général et est toujours utilisée. Comme le nombre de plaquettes à faible K augmente, le C4 est utilisé pour le faible K en remplaçant les structures UBM, les matériaux et les améliorations.

Les Plots Cu récemment développés (à peu près similaires aux avancées du C4) sont adaptés aux Plots en ligne ou superposés et non aux plaquettes à faible K. Il a été rapporté que l'encapsulation de la structure de la colonne de Cu peut endommager la couche K inférieure en raison du module d'élasticité élevé de Cu (130 GPA). La désadaptation du coefficient de dilatation thermique (CTE) est un facteur d'accélération.

En outre, la jonction métallique en fusion après l'utilisation initiale du flux par la technologie C4 et le module d'élasticité élevé du flux (50 GPA) sont considérés comme appropriés, de sorte que lors du collage et de l'installation de la plaque mère, la quantité de contraintes est ajoutée au LSI en raison des différences de dilatation thermique. Par conséquent, la technologie C4 ne peut pas être utilisée dans le futur LSI, qui est beaucoup plus faible.

Rayonnement thermique

Jusqu'à présent, les substrats organiques ont été utilisés pour l'encapsulation inversée de puces. Les substrats organiques ont une faible conductivité thermique de 0,5 W / MK et sont difficiles à appliquer aux LSI à forte consommation électrique. Si un système de refroidissement ou de refroidissement est ajouté pour améliorer le rayonnement thermique, le coût de l'emballage, les dimensions et la hauteur du plan ou de la surface augmenteront.

En effet, comme le rayonnement thermique est faible, un peu de LSI limite son potentiel pour ne pas générer de chaleur importante. En outre, la température de jonction augmente et le courant de fuite augmente en raison d'un mauvais rayonnement thermique, ce qui augmente encore la consommation d'énergie, qui augmente la température. C'est un cercle vicieux dangereux. L'amélioration du rayonnement thermique est donc un problème étroitement lié.

Haute vitesse du signal

La perte de dommage par le milieu est élevée (0,02) pour la couche centrale du substrat organique et l'impédance (T / h) des Vias de la couche centrale est élevée. En conséquence, la perte de dommages par insertion est élevée dans la gamme des hautes fréquences. Cependant, l'utilisation de substrats sans coeur dans le même matériau que les substrats organiques traditionnels n'est pas une solution fondamentale. En outre, les matériaux de couches composites peuvent être variés, de sorte que la difficulté pour l'utilisateur de choisir le meilleur matériau est plus grande, et l'ensemble des exigences prédéfinies doivent tenir compte de la question des performances à grande vitesse.

Comme le substrat est mince, une série d'installations doivent être remplacées. Cela devient un obstacle à la production. En raison de ce problème, le transfert vers un substrat sans coeur est à haut risque et ne convient qu'aux produits localisés.

Les technologies traditionnelles ont du mal à répondre aux besoins de la future génération 20nm. Il est donc nécessaire de développer de nouveaux boîtiers semi - conducteurs avec de nouvelles technologies de base.

Types de monsterpac et points clés du processus

Monsterpac type a été développé pour répondre aux processus 20nm difficiles à adapter avec les techniques d'encapsulation traditionnelles. C'est complètement différent des processus et des structures d'emballage traditionnels.

Structure d'encapsulation

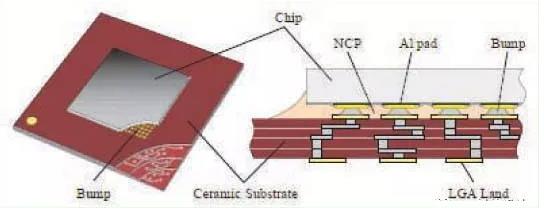

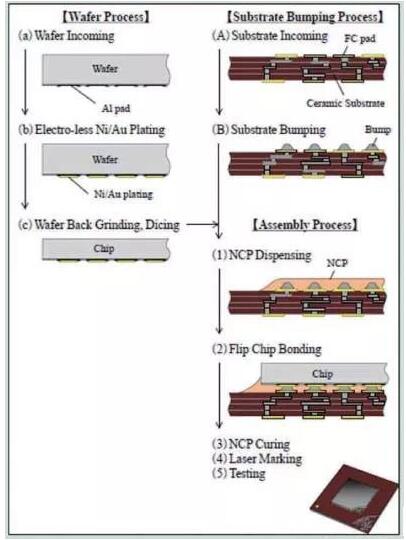

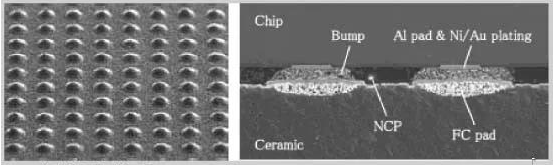

Notre structure d'encapsulation, le substrat est en céramique, la puce semi - conductrice avec l'inversion de la bosse, la puce et le substrat sont complémentaires NCP (pâte non conductrice). Il n'est pas moulé avec un gaz époxy ou une résine naturelle. Donc le dos de la puce est exposé. Le gauchissement à haute température du soudage à reflux est plus faible, inférieur à 30 - 50 µm, et est donc encapsulé en LGA (Contact Array Packaging) sans billes de soudage au lieu de BGA (Grid Array Packaging). La pâte conductrice contenant de l'argent est utilisée pour les points convexes qui sont imprimés sur le substrat, de sorte que les modules ne sont plus fabriqués sur les Plots. Nickelé et doré uniquement sur les Plots al de la puce, sans processus de point convexe de plaquette (figures 1 - 3).

FIC - 1 Structure d'emballage

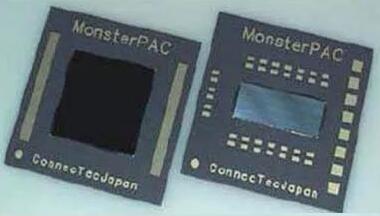

Images de Packaging FIC - 2

Processus FIC - 3

À peu près comme ci - dessus, notre boîtier est composé de seulement 4 matériaux (puce, bosse, céramique et NCP). Cette structure simple rend le boîtier petit, mince et léger.

Il existe deux principaux types de matériaux de base en céramique: htcc (Céramique Co - cuite à haute température) et LTCC (Céramique Co - cuite à basse température). Les propriétés spéciales de la céramique (telles que les propriétés électriques, la conductivité thermique, le CTE et le gauchissement) et le collage inversé de la puce permettent à nos boîtiers de répondre aux meilleures solutions pour un large éventail d'exigences, des produits électriques aux puces semi - conductrices.

Monsterpac type structure unique

Ces lieux uniques sont décrits ci - dessous:

. Aucun collage endommagé

. rayonnement thermique élevé

. faible perte d'insertion

. haute fiabilité

En combinant ces principaux avantages, monsterpac typec a réussi à fournir les meilleures performances possibles pour la génération de LSI 20nm.

Adhésif sans dommage

La technologie de base de notre Encapsulation est la technologie de collage de puce inversée sans dommage, qui permet avec succès un collage sans dommage et très fiable des puces semi - conductrices fabriquées avec un usinage de précision de pointe.

Par puce semi - conductrice non endommagée, on entend:

Collage basse pression

Nous pouvons atteindre une pression de collage de 0,12 G / Bump, soit 1 / 20 de la pression de 2,4 G / Bump du C4 normal. En réduisant la charge de collage à cette limite, il est possible d'éviter l'endommagement du milieu inter - couches par collage.

Faible contrainte de rétraction pendant la solidification convexe

La contrainte de contraction pendant la solidification du point convexe est inférieure à 10 MPa / point convexe et très faible. Grâce à la réduction de la température, de la charge et des contraintes de rétraction appliquées aux couches intermédiaires de milieux fragiles, telles que les Plots et les lignes à faible teneur en K et en al, par une limite supérieure, un soudage à l'envers fiable et à haut rendement a été réalisé avec succès, évitant ainsi la rupture et la fissuration des lignes.

Il ressort de ces avantages qu'il s'agit de la seule Encapsulation présentant une structure évitant les dommages causés par une faible couche K.

Rayonnement thermique élevé

Conscient que la chaleur de la puce semi - conductrice est rayonnée par le substrat d'encapsulation, nous avons choisi un substrat en céramique au lieu d'un substrat organique ordinaire (conductivité thermique de 0,5 W / MK), car sa conductivité thermique est supérieure de 14 W / MK à celle du substrat organique. Lorsque la taille de l'encapsulation est de 21 * 21 mm et que le substrat en céramique est utilisé, la consommation d'énergie atteint 6 w, Il est 1,7 fois plus puissant qu'un substrat organique avec une consommation d'énergie de 3,6 W.

Une insertion basse peut vous blesser

L'électronique exige un haut niveau de performance dans la gamme des hautes fréquences. La perte d'insertion du substrat céramique est de 0,42 DB (@ 20 GHz, l = 5 mm) alors que celle du substrat organique est de 0,62 db. Les fréquences autorisées sont supérieures à 10 GHz pour les substrats céramiques et à 3 GHz pour les substrats organiques.

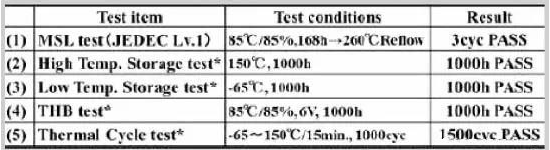

Haute fiabilité et haute résistance à l'humidité

La résistance de retour normale (MSL: niveau de mouillage) est de classe 3 (@ 30deg / 60 100% rh192hr). Monsterpac types ont chacun une puce semi - conductrice non endommagée avec des bosses en matériau non fondu. Au reflux à haute température, les billes ne fondent pas et ne sont donc pas refondues et reconsolidifiées à plusieurs reprises, et le substrat en céramique n'absorbe pas l'humidité. Ainsi, avec un MSL de classe 1 (@ 85deg / 85 100% rh192hr) qui élimine l'humidité et l'emballage résistant à l'humidité sans cuisson préalable, la durée de vie des plantes du monsterpac type C est illimitée.

Taux de croissance élevé des plantes

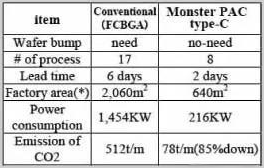

Pour faciliter la production, nous avons développé une structure de billes de gaz époxy au lieu de billes soudées. Un grand nombre d'installations de traitement des plots de plaquette est donc nécessaire, tout comme le coût d'un grand nombre de soudures can + adjacentes au reflux. Ainsi, les dimensions planes ou superficielles de l'installation peuvent être réduites de 69% et la consommation d'énergie de l'installation peut être réduite de 85% par rapport à une unité de traitement C4 classique de même taille. Les centrales électriques à économie d'énergie et à faible charge de fond peuvent être réalisées avec succès.

Capacité

Monsterpac typec processus unique

Technologie céramique surélevée

Monsterpac type considère qu'il convient d'utiliser une pâte conductrice contenant de l'argent comme matériau de billes. Les renflements (le cas échéant) sont formés sur le substrat céramique à l'aide des techniques habituelles d'impression de pièces SMD par soudage. Il n'est pas nécessaire de prétraiter et de nettoyer la surface du substrat en céramique avant le traitement des points hauts, ni de galvaniser la surface après la formation des points hauts. Les fcbga organiques classiques nécessitent de longs points convexes, tels que des points convexes au, Cu et Fluid, sur les Plots Al des plaquettes semi - conductrices. Cependant, les Plots à base de céramique ne nécessitent pas un tel procédé de plots de longueur de plaquette. Au lieu de cela, ils produisent ni et au non plaqués sur des puces semi - conductrices. Les bosses basées sur la technologie céramique permettent avec succès un processus simple à manipuler et peu coûteux.

En outre, contrairement aux points durs et convexes (dureté 10hv) utilisés dans les techniques de bon sens telles que les points au et Cu convexes, les points doux et convexes (1hv) ont été développés pour maintenir les motifs à faible dureté.

Pour les boues conductrices molles et convexes contenant de l'argent, nous avons développé des points de fixation pertinents expérimentés dans l'impression de faible contrainte, de faible résistance au contresignage et d'asphalte détaillé. La force de travail des plots que nous avons formés jusqu'à présent est les plots de matrice de faces: pas 150 angströms; Pads périphériques: espacement 75 îles. Cependant, la règle de préréglage pratique tient compte de cet espacement des plots, de sorte qu'un espacement surfacique de 60° m ne s'applique qu'aux Plots ouverts.

Adhésif sans dommage

À l'aide de la technologie de collage de puce à inversion douce, NCP est utilisé pour distribuer les bosses douces formées par la technologie des bosses en céramique, puis pour assembler la puce semi - conductrice avec la puce à inversion. Lors du collage, la pâte conductrice des plots et le NCP sont solidifiés simultanément. En conséquence, la signature conjointe et la fiabilité ont été atteintes avec succès.

La température dans les installations de FCB est inférieure à 200 degrés Celsius, soit plus de 40 degrés Celsius de moins que la technologie de collage normale. La pression de collage est inférieure à 0,12 G / dot, soit 1 / 20 de la technologie de collage ordinaire. Grâce à ces collages à chaud basse température et basse tension, les puces semi - conductrices ne sont pas affectées par les contraintes et les forces externes lors du collage et du durcissement post - Collage. En utilisant une pâte conductrice nouvellement développée et NCP, un collage à grande vitesse inférieur à 1,0 seconde a été réalisé avec succès. NCP comprend des suppléments qui se trouvent généralement sur les deux côtés des plots de puce et des bosses. Cependant, il est courant de retourner la clé de la puce à basse pression. Ce complément est enterré dans les Plots et n'affecte donc pas la signature entre les plots de puce et les Plots. C'est l'un des avantages des bosses douces. Après la distribution des NCP avant le soudage à l'envers, les NCP se complètent facilement entre les points convexes et les espaces étroits, et avec des touches à faible charge, aucun alignement entre la puce et le substrat ne se produit. Cette technique de collage est donc adaptée à un espacement étroit des plots.

Le problème avec les techniques de collage courantes est que dans le cas d'un collage de puce inversée avec des plots de soudage, des contraintes de rétraction très importantes (de l'ordre de 200 à 500 MPa / plot) sont appliquées sur les Plots et les Plots d'Al de la puce semi - conductrice lors de la fusion du flux jusqu'à la solidification. La technique de collage sous faible contrainte est un succès car le faible module d'élasticité du matériau convexe non fondu nécessite une très faible contrainte de rebond (inférieure à 10 MPa / convexe).

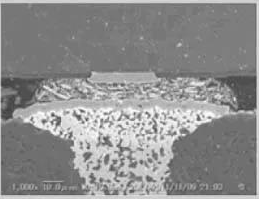

C'est grâce au processus de développement de ces technologies de base décrit ci - dessus que le succès du soudage à l'envers est sans perte. La figure 4 est une vue de profil des points clés et du contresignet de la puce inversée.

Image - 4 photos d'apparence et de profil

Fiabilité de l'emballage

TC a testé le profil du point convexe arrière, mais n'a pas testé et mesuré les fissures et les détartrages pouvant résulter du couplage de rupture.

APIC (Applied Device IC)

Aujourd'hui, l'usinage APIC évolue vers un usinage de précision avec des matériaux à faible teneur en K, ce qui nécessite des tolérances de température élevées et des vitesses élevées. Le monsterpac typec offre les avantages suivants pour répondre à ces exigences.

. Aucun collage endommagé

. rayonnement thermique élevé

Lorsque la vitesse est élevée

Certains clients APIC évaluent la production à grande échelle de monsterpac typec

Type de PAC C

A la suite d'une évaluation pratique entre le fcbga organique et le monsterpac type C dans les mêmes conditions (même jupe, même puce et même espacement des plots), la température tj du monsterpac type C est inférieure de 10°C à celle du boîtier organique. Après une comparaison très précise de TJ, la différence sera d'environ 20 degrés Celsius.

Plaque RF (plaque RF):

Actuellement, pour les communications à haut débit LSI, l'encapsulation de la carte est en constante amélioration. Ces Parties nécessitent les caractéristiques particulières suivantes:

. convient pour haute vitesse et haute fréquence

Petite taille

Pour les applications haute vitesse et haute fréquence, comme indiqué ci - dessus, l'utilisation d'un substrat céramique, le cas échéant, permet d'améliorer les pertes d'insertion, qui peuvent être utilisées à 10 GHz.

En outre, plusieurs Puces et un grand nombre de composants SMD peuvent être utilisés dans de petits boîtiers, car il est possible d'utiliser de petites puces inversées avec un pas de détail.

Travailler avec les clients pour développer des échantillons de plaques RF, dont les performances ont été reconnues par les clients, se préparent à la production à l'échelle

Module RF

Pour ces boîtiers de plaques, l'humidité du substrat est très serrée. Le monsterpac typec a un MSL de classe 1, il n'y a donc pas d'étouffement humide.

Comme on peut le voir, monsterpac typec est le mieux adapté au boîtier plat, où le boîtier organique traditionnel SMD et les puces inversées nécessitent plusieurs soudures à reflux.

Le juge

Pour la prochaine génération de processus 20 nm, l'encapsulation est nécessaire pour s'adapter à un rayonnement thermique plus élevé et à des vitesses plus élevées. Cependant, les techniques d'emballage de bon sens peuvent difficilement répondre à ces exigences. Il est donc nécessaire de développer une nouvelle technique d'encapsulation adaptée au procédé 20 nm.

Notre monsterpac typec est adapté pour le processus 20nm à venir et maximise les performances LSI. Sa haute performance est comme un produit étonnamment bizarre. Le monsterpac que nous avons développé rend le C4 obsolète et constitue une technologie majeure pour la prochaine génération de semi - conducteurs.

Développé pour la prochaine génération de technologies

Recherche et développement de nouveaux substrats céramiques

Le développement de la technologie des substrats céramiques a toujours été brillant. Jusqu'à présent, la cartographie précise et détaillée à haute densité a pris beaucoup de retard sur les substrats IC organiques.

Pour résoudre ce problème et progresser, nous avons entrepris de développer un substrat en céramique de précision avec une densité élevée sans compromettre les coûts. Nous visons un espacement des lignes de 20 ° m pour une précision appropriée et l'utilisation de graphiques détaillés plus flexibles. Par défaut, l'espacement des trous traversants doit également être plus précis et détaillé, avec un objectif de 50 ° m.

Jusqu'à présent, les substrats céramiques ont été réalisés à l'aide d'estampages et, le cas échéant, d'impressions à masque. Ces techniques existantes se limitent à des dessins précis et détaillés. Nous envisageons de les remplacer par des procédés d'impression laser et directe. La mise en oeuvre de cette technique permettra d'obtenir de meilleures performances que les substrats organiques. Jusqu'à présent, les substrats en céramique étaient généralement utilisés dans les produits haut de gamme, mais ce nouveau type de substrat ciblera les produits de consommation. Le substrat a vraiment besoin de produits de consommation de haute performance pour se développer.

La combinaison de ce substrat avec la technologie monsterpac fournira au monde les meilleures performances et une grande fiabilité pour les circuits imprimés (PCB).