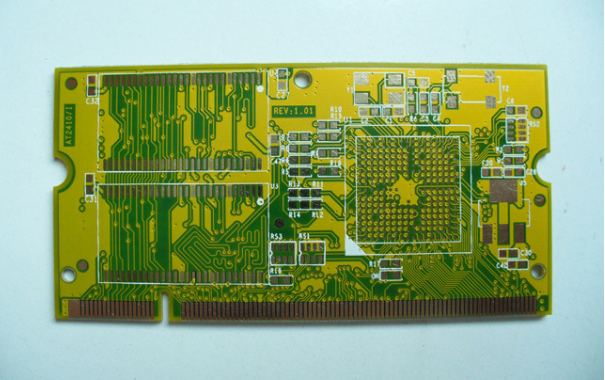

L'impact des tendances de développement de l'industrie électronique sur les circuits imprimés

Tendances et développements en assemblage

La polyvalence, la vitesse de transmission élevée et la miniaturisation de l'électronique portable sont les principaux moteurs de l'amélioration continue du semi - conducteur global, de l'emballage, de l'assemblage et des cartes PCBA. Voici une analyse des tendances de développement à chaque niveau de construction au cours des 5 prochaines années.

1 la dynamique du changement en raison de la nécessité d'une révolution rapide des produits et de l'innovation du marché, la conception de l'électronique portable a développé un certain nombre de caractéristiques de tendance, notamment la miniaturisation, la légèreté, la faible consommation d'énergie, l'augmentation des fonctionnalités, l'interface avancée, la connectivité sans fil, le style de mode et bien plus encore. Répondre au besoin de protection de l'environnement vert. Le marché se caractérise par un cycle de vie des produits plus court, l'intégration d'applications 3c, une plus grande échelle de production, une réponse du marché plus rapide et en temps réel et une complexité et une diversité accrues des produits. Pour répondre à ces exigences, il est nécessaire de modifier les processus d'emballage et d'assemblage électroniques. Un aperçu des dernières tendances, de leurs transformations et de leurs défis; Les tendances des composants individuels, des plaques porteuses et des assemblages seront un peu mieux comprises à partir de ce qui suit.

En général, maximiser le nombre de broches et la taille du boîtier peut accueillir plus d'E / s en petites quantités. Afin de limiter l'augmentation de la taille du boîtier, l'espacement doit être réduit à 0,3 mm, en fonction du prix du développement BGA et CSP. À la même surface, les boîtiers BGA et CSP peuvent contenir plus d'E / s et ont un espacement plus large des points convexes ^ 3. À l'avenir, les prix des BGA et des CSP baisseront encore, ce qui remplacera de nombreux marchés d'encapsulation qfp. Il est particulièrement intéressant de noter que Seated hcight (distance du haut du boîtier à la surface du PCB) sera réduit.

Deux paquets BGA d'ici 2006, le nombre d'E / s passera à 1 200, ce qui constitue une certaine tendance pour les applications informatiques portables. Afin de limiter les dimensions du corps et d'éviter les problèmes de fiabilité, la configuration de surface des plots évoluera vers un type de matrice pleine surface. Pour la même raison, l'espacement des renflements sera légèrement réduit. La hauteur du siège sera réduite pour installer un produit final plus mince. Les tendances les plus importantes de l'évolution de la BGA sont présentées dans le tableau 9.2.

Les CSP (triple Chip level Package) ont deux types de broches externes, l'un est un plot (type BGA) et l'autre est un plot (type LGA). Le LGA a une hauteur de chute maximale inférieure, car il n'a pas de bosse. En conséquence, le LGA devient de plus en plus populaire, bien que la faible hauteur de la butée réduira la durée de vie des interconnexions de deuxième niveau. Le développement commun de ces deux types d'emballage est que la hauteur d'assise maximale sera réduite et le nombre d'E / s augmentera. En raison de l'espacement des matrices intégrées / terrestres, la taille du boîtier est réduite à 0,3 mm, ce qui sera également réduit. Les dimensions des bossages / Plots seront également réduites. Le tableau 1 présente les tendances les plus importantes en matière de PSC.

Une forme particulière de CSP est le CSP au niveau de la plaquette (Wafer level CSP), qui est un type d'encapsulation qui est réalisée avant la découpe de la plaquette dans un moule. Le principal avantage est le faible coût de ces boîtiers, car les unités de production sont des plaquettes et non des puces, et l'augmentation de la taille des plaquettes est également favorable à la réduction du coût de ce type de boîtier.

Dans le domaine des produits de consommation portables, le nombre d'E / s de type FC directement connecté à la carte mère a légèrement augmenté et la taille de la puce n'a pas beaucoup changé. La technologie 1c permet de fabriquer des circuits à plus haute densité. Avec la même taille, le moule peut avoir plus de fonctions.

Parce que le processus d'amélioration du signal sur la puce a peu d'effet sur le nombre d'E / S. L'épaisseur du noyau et l'espacement des points convexes seront réduits. L'espacement minimal des points convexes varie en fonction de la technologie de connexion utilisée, qui sera discutée plus loin. Le processus de remplissage par le bas ajouté pour assurer sa fiabilité empêche l'application directe du FC sur la carte mère. Une fois que les technologies alternatives auront mûri, l'application de FC augmentera considérablement. Les alternatives possibles sont l'apprêt IIO Flow (mélange de flux et d'apprêt à haute viscosité) et la colle d'étanchéité arrière sur la plaquette.

Cinq comparaisons des différents types d'encapsulation 1c le tableau 3 est une comparaison des différents types d'encapsulation décrits ci - dessus. De qfp, BGA, CSP à WL - CSP, la densité des puces inversées et des E / s a augmenté, tandis que l'espacement et la taille des boîtiers ont diminué. Les propriétés électriques et thermiques ont été améliorées, mais la capacité de charge lourde, l'usinabilité, les tests électriques, le degré de protection des grains, la compatibilité avec la conception 1C et le reflux standard et la polyvalence des composants ont été médiocres. En termes de fiabilité, qfp et FC fournissent les meilleurs résultats. Qfp, WL - CSP et Flip - chip ont des avantages en termes de coûts, en particulier le qfp le plus bas.

Six composants passifs composants passifs la taille des condensateurs et des résistances devrait être réduite à la taille 0101 d'ici 2006. Par élément passif intégré, on entend l'intégration de plusieurs fonctions passives (nombre d'E / s > 2) dans une âme en silicium ou en céramique. Certains éléments passifs sont également intégrés dans le silicium 1C (par example des condensateurs de découplage).

Les plaques porteuses multicouches (céramiques ou organiques) sont utilisées pour l'assemblage anti - moisissure et intègrent certaines fonctions passives spécifiques.