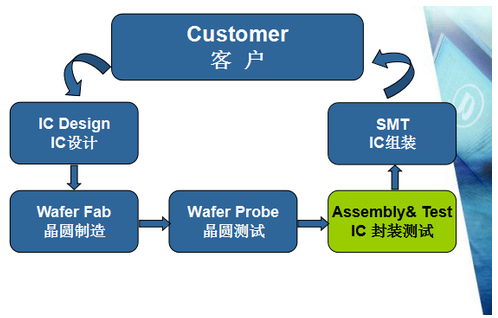

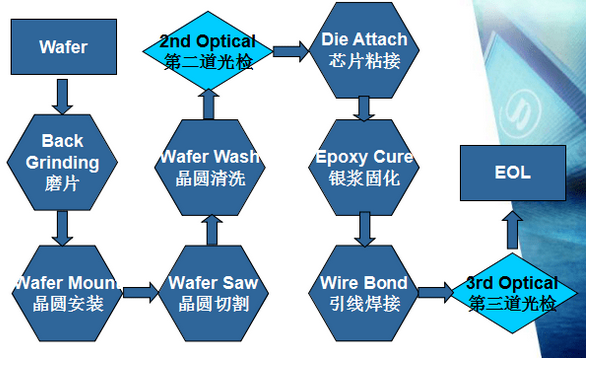

Processo di imballaggio e collaudo dei chip IC:

Processo

Il pacchetto IC si riferisce al chip (Die) e ai diversi tipi di telaio (L/F) e materiale di sigillamento plastico (EMC) formati da diverse forme del corpo del pacchetto.

Ci sono molti tipi di pacchetto IC, che possono essere classificati come segue:

Secondo i materiali di imballaggio, può essere suddiviso in:

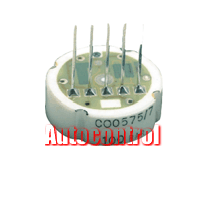

Imballaggi metallici, imballaggi ceramici, imballaggi in plastica

L'imballaggio metallico è utilizzato principalmente nella tecnologia militare o aerospaziale, nessun prodotto commerciale;

L'imballaggio ceramico è migliore dell'imballaggio metallico, utilizzato anche in prodotti militari, una piccola quantità di mercato commerciale;

Imballaggio in plastica per elettronica di consumo, il suo basso costo, processo semplice, alta affidabilità e occupano la stragrande maggioranza della quota di mercato;

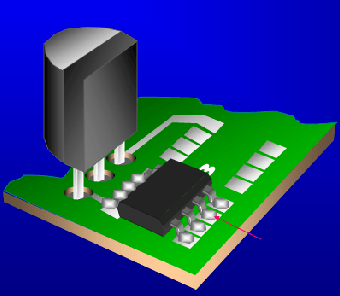

Secondo la modalità di connessione con scheda PCB, può essere divisa in:

Imballaggi PTH e imballaggi SMT

PTH-Pin Through Hole;

SMT-Surface Mount Technology. Attualmente, la maggior parte dei IC sul mercato sono adottati per il tipo SMT.

Secondo l'aspetto del pacchetto, può essere diviso in:

SOT, SOIC, TSSOP, QFN, QFP, BGA, CSP, ecc.

Due fattori chiave determinano la forma di incapsulamento:

Efficienza di incapsulamento. area chip/area pacchetto, il più vicino possibile a 1:1;

Numero di pin. Più perni, più avanzati, ma anche la difficoltà del processo aumenta di conseguenza;

Tra questi, CSP, a causa dell'uso della tecnologia Flip Chip e del pacchetto Chip nudo, area Chip / area pacchetto =1:1, che è la tecnologia più avanzata al momento.

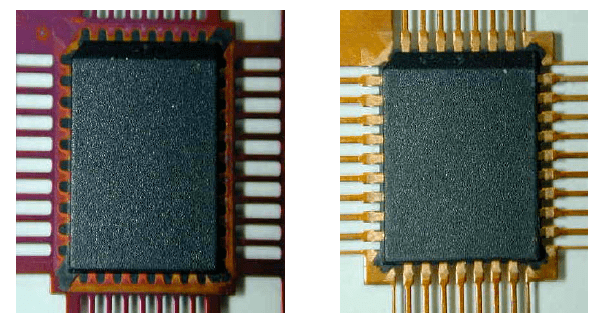

QFN -- Quad Flat No-lead Package QFN -- Quad Flat No-lead Package

SOIC - Small Outline IC Package

TSSOP - Thin Small Shrink Outline Package

QFP - Quad Flat Package

BGA -- Pacchetto array griglia sferica

CSP - Pacchetto Chip Scale Pacchetto Chip Scale

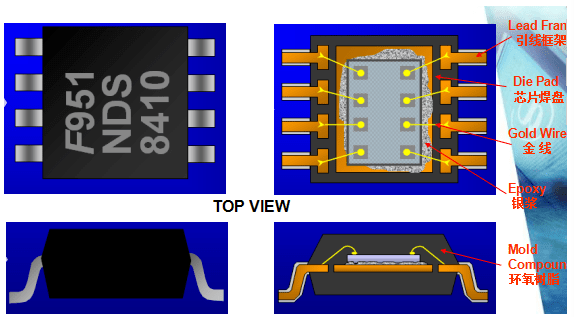

Struttura del pacchetto IC

Materie prime in Assemblyã? Waferã"

"Lead Frame"

Fornisce il collegamento del circuito e la fissazione di Die;

Il materiale principale è rame, che sarà rivestito con argento e NiPdAu.

Il processo L/F include Etch e Stamp;

Facile da ossidare, immagazzinato in un gabinetto di azoto, l'umidità è inferiore a 40% RH;

Tranne BGA e CSP, altri pacchetti utilizzeranno Lead Frame, mentre BGA utilizzerà Substrato;

# Fili d'oro #

Realizzare il collegamento elettrico e fisico tra il chip e il telaio esterno del cavo;

Filo d'oro è oro di alta purezza 99,99%;

Allo stesso tempo, a causa di considerazioni sui costi, vengono attualmente utilizzati processi di filo di rame e filo di alluminio. Il vantaggio è che il costo è ridotto e la difficoltà di processo è aumentata, il rendimento è ridotto;

Il diametro del filo determina la corrente conduttiva; 0.8mil, 1.0mil, 1.3mils, 1.5mils e 2.0mils;

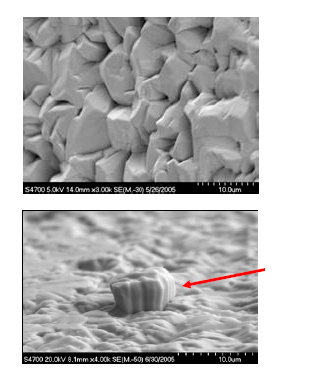

I componenti principali del composto dello stampo / resina epossidica sono: resina epossidica e vari additivi (agente indurente, modificatore, agente spogliante dello stampo, agente colorante, agente ritardante di fiamma, ecc.);

Le funzioni principali sono le seguenti: Il dado e il telaio del piombo sono avvolti nello stato fuso per fornire protezione fisica ed elettrica e prevenire interferenze esterne;

Condizioni di stoccaggio: 5° sotto lo zero, 24 ore alla temperatura normale;

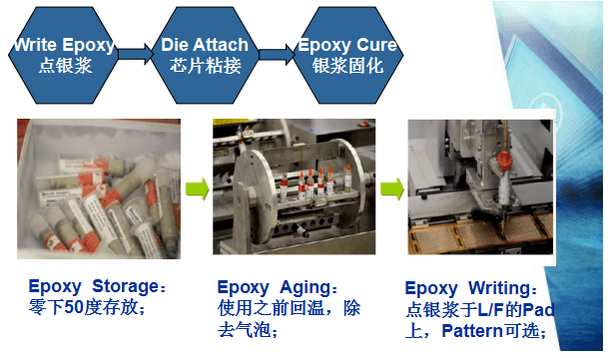

"Epoxy"

Polvere metallica riempita di resina epossidica (Ag); Ha tre funzioni: fissare il Die sul Die Pad; dissipazione del calore, effetto conduttivo;

-50° sotto lo stoccaggio, prima dell'uso temperatura posteriore 24 ore;

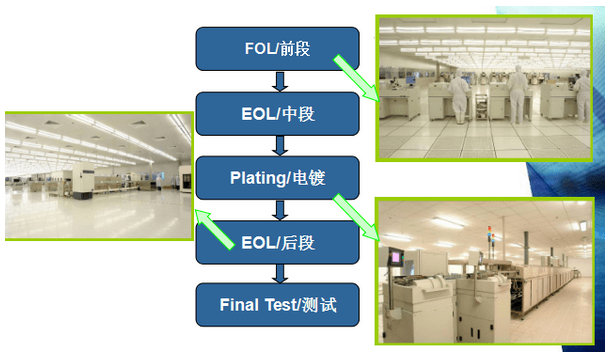

FOL-Front of Line

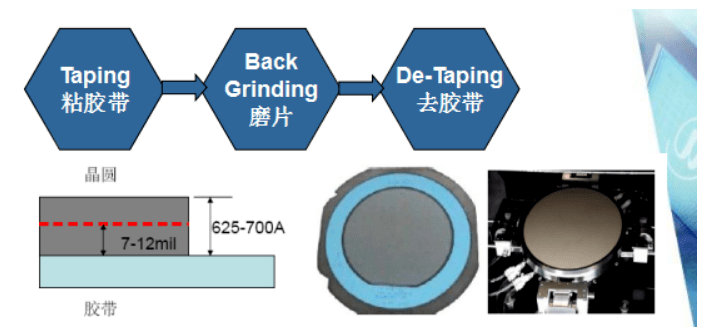

Grinding FOL-Back

Il Wafer dalla fabbrica Wafer è macinato sul retro per ridurre lo spessore del Wafer richiesto per l'imballaggio (8mils ~ 10mils).

Durante la rettifica, è necessario mettere del nastro sull'area attiva per proteggere il circuito e macinare il retro allo stesso tempo. Dopo la macinazione, rimuovere il nastro e misurare lo spessore;

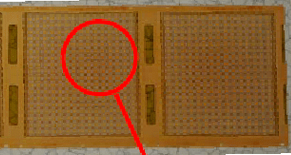

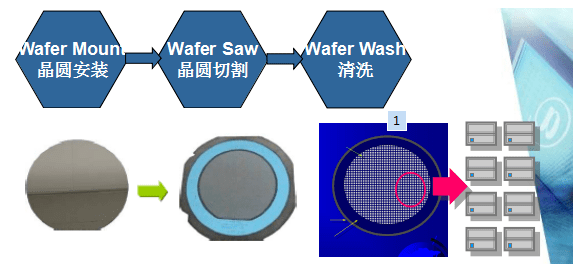

FOLâ Wafer Saw

Il wafer è incollato su una pellicola blu (Mylar) in modo che non cada a pezzi anche dopo essere stato tagliato;

Tagliare l'intera cialda in dadi indipendenti attraverso la lama di sega per facilitare Die Attach e altri processi dietro.

Pulire principalmente la polvere prodotta dalla sega, pulire il wafer;

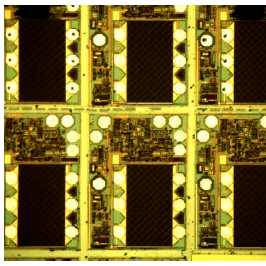

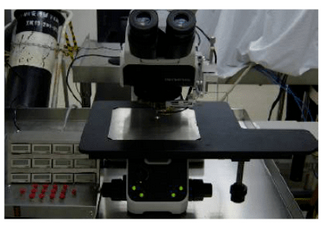

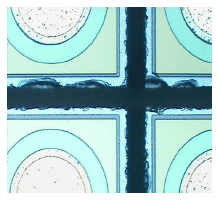

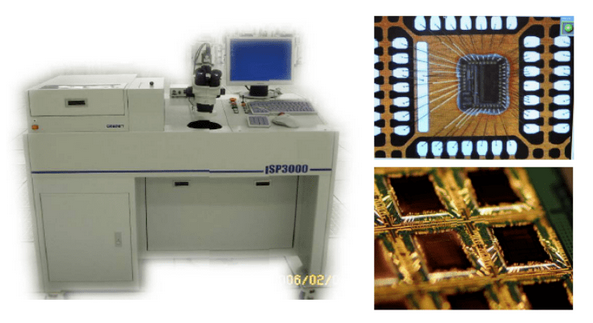

FOL -- 2a ispezione ottica

Lo scopo principale è quello di ispezionare l'aspetto del Wafer sotto microscopio dopo Wafer Saw per vedere se ci sono rifiuti.

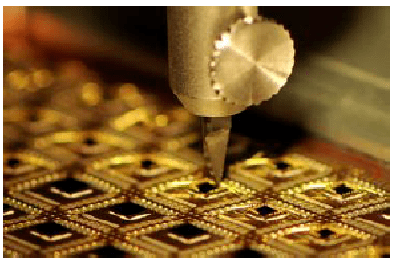

FOLâ Die Attach

Processo di raccolta trucioli:

1. Pin dell'Ejector che solleva il chip da Mylar sotto il wafer, rendendo facile staccarsi dal film blu;

2. Il chip viene prelevato dall'alto per completare il processo di trasporto da Wafer a L/F;

3. raccogliere il chip Bond sul Pad L/F con pasta d'argento con una certa forza e la posizione specifica è controllabile;

4, risoluzione della testa di legame: x-0.2um; Y - 0,5 um; Z - 1,25 um;

5. velocità della testa di legame: 1.3m/s;

FOLâ Epoxy Cure

175°C, 1 ora; Ambiente N2, per prevenire l'ossidazione:

Controllo qualità dell'attacco:

Die Shear

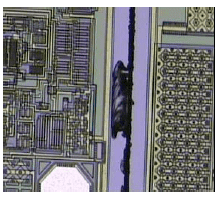

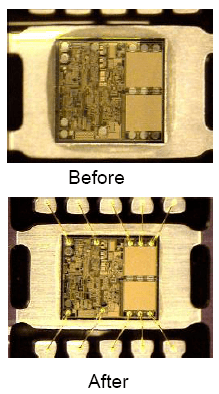

FOLâ Legatura metallica

I fili di oro (Au), rame (Cu) o alluminio (Al) ad alta purezza sono utilizzati per collegare il Pad e il piombo tramite saldatura. Il Pad è il punto di connessione esterno del circuito sul chip e il cavo è il punto di connessione sul telaio del cavo.

Il W/B è il processo più critico nel processo di confezionamento.

3a ispezione ottica

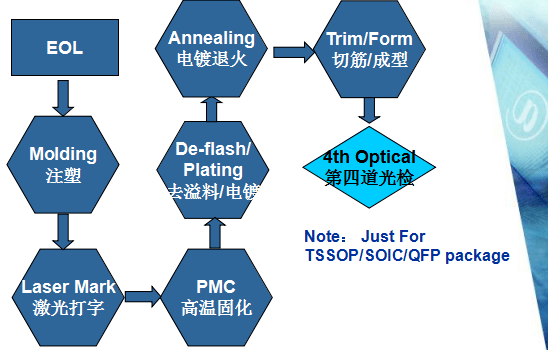

EOLâ Fine linea

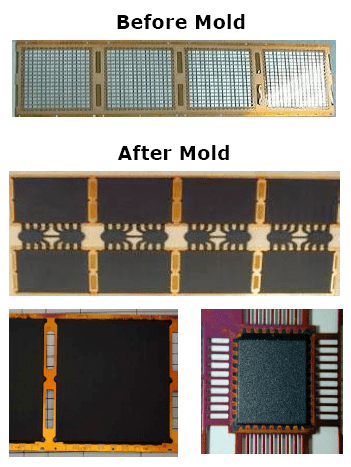

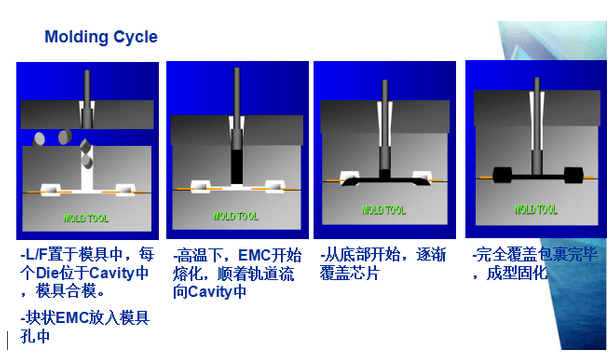

EOLâ Molding

EOLâ Laser Mark

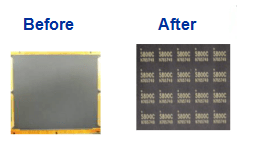

Letteratura laser sulla parte anteriore o posteriore del pacchetto. Il contenuto include: nome del prodotto, data di produzione, lotto di produzione, ecc.

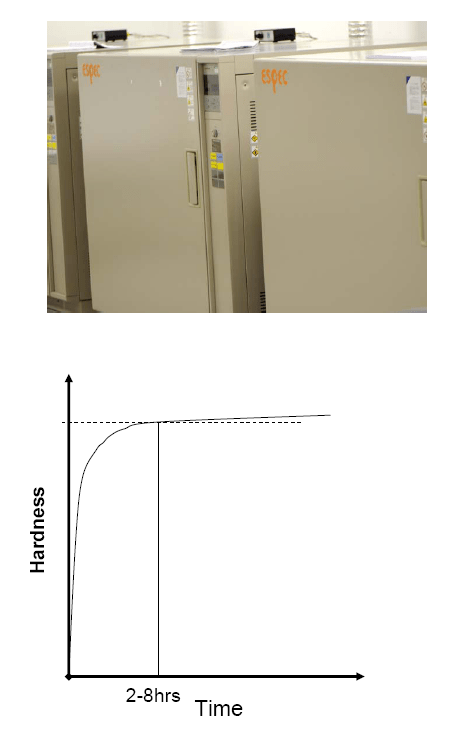

EOLâ Post Mold Cure

Utilizzato per la polimerizzazione della plastica dopo lo stampaggio per proteggere la struttura interna di IC ed eliminare lo stress interno. Temperatura di cura: 175 + / - 5 ° C; Tempo di cura: 8 HRS

EOLâ De-flash

Scopo: lo scopo di de-Flash è quello di rimuovere lo stampaggio in eccesso tra i cavi intorno al corpo del tubo dopo lo stampaggio; Metodi: Immergere con acido debole e risciacquare con acqua ad alta pressione.

EOLâ Plating

Utilizzando metodi metallici e chimici, viene applicato un rivestimento sulla superficie del Leadframe per prevenire gli effetti dell'ambiente esterno (umidità e calore). E rendere i componenti sulla scheda PCB facili da saldare e migliorare la conducibilità elettrica.

Ci sono generalmente due tipi di galvanizzazione:

Pb-free: galvanizzazione senza piombo, utilizzando >99,95% di stagno ad alta purezza (stagno), per l'attuale tecnologia ampiamente utilizzata, in linea con i requisiti RoHS;

E' una lega di stagno-piombo. Lo stagno rappresenta l'85% e il piombo il 15%. Poiché non è conforme alla RoHS, è fondamentalmente eliminato al momento.

EOLâ Post Annealing Bake

Obiettivo: Lasciare cuocere il prodotto dopo la galvanizzazione senza piombo ad alta temperatura per un periodo di tempo, al fine di eliminare il potenziale problema di crescita del Whisker della galvanizzazione; Condizione: 150 + / - 5 - c; 2 ore;

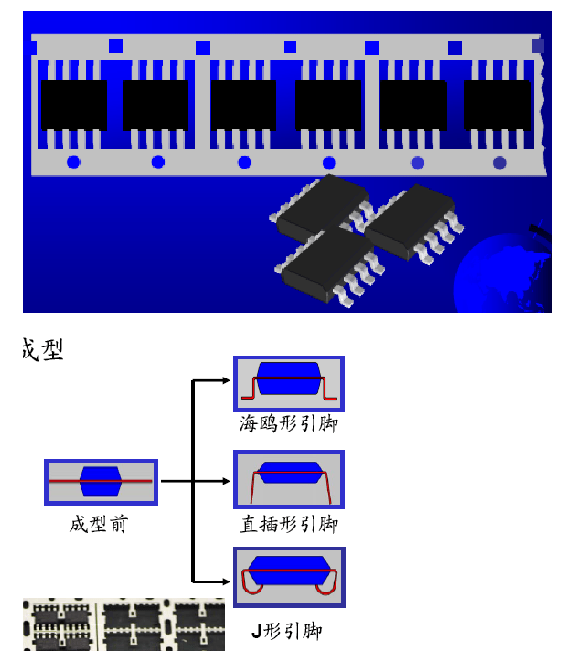

Il processo di taglio del telaio di piombo di una fetta in singole unità (IC); Forma: modellare il prodotto IC dopo Trim, raggiungere la forma richiesta dal processo e metterlo nel tubo o vassoio;

EOLâ Ispezione visiva finale

Ispezionare l'aspetto del prodotto sotto una lente di ingrandimento a bassa potenza.

5. concentrarsi sui potenziali prodotti di scarto dal processo EOL come difetti di stampaggio, difetti di placcatura, difetti di Trim/Form ecc.