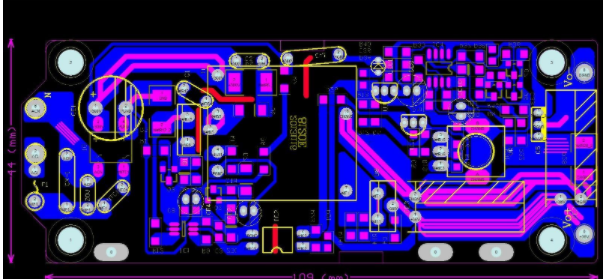

Dieser Artikel konzentriert sich auf PCB-Designer die IP verwenden, und verwendet weiterhin Topologieplanungs- und Routing-Tools, um IP zu unterstützen, um das gesamte PCB-Design schnell abzuschließen. Wie aus Abbildung 1 ersichtlich ist, Der Konstrukteur hat die Verantwortung, IP zu erhalten, indem er eine kleine Anzahl notwendiger Komponenten anordnet und die kritischen Verbindungswege zwischen diesen Komponenten plant..

Sobald die IP erhalten ist, können die IP-Informationen dem PCB-Designer zur Verfügung gestellt werden, und der PCB-Designer wird das verbleibende Design abschließen. PCB-Designer verwenden außerdem Topologieplanungs- und Routing-Tools, um IP zu unterstützen, um das gesamte PCB-Design schnell abzuschließen. Jetzt gibt es keine Notwendigkeit, die richtige Designintention durch die Interaktion und den iterativen Prozess zwischen dem Konstrukteur und dem Leiterplattendesigner zu erhalten. Der Konstruktionsingenieur hat diese Informationen erhalten und das Ergebnis ist ziemlich genau, was dem PCB-Designer eine große Hilfe ist. In vielen Designs müssen Konstrukteure und Leiterplattendesigner interaktives Layout und Routing durchführen, was für beide Parteien viel wertvolle Zeit verbrauchen kann. Erfahrungsgemäß sind interaktive Operationen notwendig, aber zeitaufwendig und ineffizient.

Der vorläufige Plan des Konstrukteurs darf nur eine manuelle Zeichnung sein, ohne entsprechende Komponentenskala, Busbreite oder Pin-Ausgabe Aufforderungen.

Da Leiterplattendesigner am Design teilnehmen, können Ingenieure, die Topologieplanungstechnologie verwenden, das Layout und die Verbindung bestimmter Komponenten erhalten. Dieser Entwurf kann auch das Layout anderer Komponenten, die Sammlung anderer IO- und Busstrukturen und die Fertigstellung aller Verbindungen erfordern.

PCB-Designer Notwendigkeit, Topologieplanung zu übernehmen und mit dem Leiterplattenlayout Komponenten unter dem Layout, um das beste Layout und interaktive Planung zu erreichen, dadurch die Effizienz des PCB-Designs zu verbessern. Mit der Fertigstellung des Layouts von Schlüsselflächen und Gebieten mit hoher Dichte und dem Erwerb der Topologieplanung, Das Layout kann der endgültigen Topologieplanung vorausgehen. Daher, Einige topologische Pfade müssen möglicherweise das vorhandene Layout verwenden. Obwohl sie eine geringere Priorität haben, sie müssen noch angeschlossen werden. Daher, Ein Teil der Planung dreht sich um das Layout der produzierten Komponenten.

Darüber hinaus kann diese Planungsstufe detailliertere Details erfordern, um anderen Signalen die erforderliche Priorität zu geben. Einige Hindernisse vor dem automatischen Routing eines bestimmten Busses können dem Algorithmus Optionen für andere Routing-Layer bieten. Da der Bus in engen Linien auf der ersten Schicht organisiert ist, beginnt der Designer, den Umwandlungsteil als dritte Schicht mit den Details "3" zu planen und die Entfernung zu berücksichtigen, die der Bus durch die Leiterplatte führt. Beachten Sie, dass dieser Topologiepfad auf Schicht 3 breiter ist als die oberste Schicht, da er zusätzlichen Platz benötigt, um die Impedanz aufzunehmen. Darüber hinaus gibt das Design auch die genaue Lage des Schichtübergangs (17-Löcher) an. Wenn sich der topologische Pfad vom rechten Teil der Abbildung 3 bis zum Detail "4" nach unten bewegt, müssen aus der topologischen Pfadanbindung und jedem Bauteilpin viele einzelne T-förmige Verbindungspunkte gezogen werden. PCB-Designer entscheiden sich dafür, die meisten Verbindungen auf Schicht 3 zu halten und andere Schichten zu durchdringen, um Komponentenpins zu verbinden.

Daher zeichneten sie einen topologischen Bereich, um die Verbindung vom Hauptgurt zur vierten Schicht (rosa) anzuzeigen, und verbanden den Einheit T-Kontakt mit der zweiten Schicht und verwendeten dann andere Durchgänge, um die Gerätepins anzuschließen. Der topologische Pfad führt auf Ebene 3 weiter zu detaillierten Informationen "5", um aktive Geräte anzuschließen. Diese Verbindungen werden dann von den aktiven Pins an die Ausziehwiderstände unter dem aktiven Gerät angeschlossen.

Der Designer verwendet eine andere Topologiebereiche Spezifikation, um von Schicht 3 zu Schicht 1 zu verbinden, wo die Komponenten Pins aktive Geräte und Pull-Down Widerstände sind. Diese Detailplanung kann in etwa 30 Sekunden abgeschlossen werden. Nach Erhalt dieses Plans möchten PCB-Designer möglicherweise sofort routen oder eine weitere Topologieplanung erstellen und dann die gesamte Topologieplanung durch automatisches Routing abschließen. Es dauert weniger als zehn Sekunden von der Fertigstellung des Plans bis zum Ergebnis der automatischen Verkabelung. Tatsächlich ist diese Geschwindigkeit nicht wichtig. Wenn Sie die Absicht des Designers ignorieren, ist die Qualität des automatischen Routings sehr schlecht, was eine komplette Zeitverschwendung ist. Es dauert etwa zehn Sekunden, um eine hochwertige automatische Verkabelung durchzuführen. Durch die Anhebung des Abstraktionsniveaus zur Topologieplanung wird die gesamte Verbindungszeit erheblich verkürzt. Bevor die Verbindung beginnt, hat der Designer ein wirklich klares Verständnis für die Dichte und das Potenzial, das Design zu vervollständigen. Warum zum Beispiel die Linie an dieser Stelle im Design behalten? Warum nicht weiter planen und Linien auf der Rückseite hinzufügen? Wann ist die komplette Topologie geplant?

Wenn Sie das obige Beispiel betrachten, kann die Planabstraktion mit einem anderen Plan anstelle von 17-unabhängigen Netzwerken mit vielen Segmenten und vielen Löchern in jedem Netzwerk verwendet werden. Dieses Konzept ist sehr wichtig bei der Betrachtung technischer Änderungsaufträge (Ökologie, Projekt).

Engineering Change Order (ECO) Im folgenden Beispiel ist der FPGA-Pin-Ausgang noch nicht abgeschlossen. Konstrukteure haben PCB-Designer über diese Realität informiert, aber aus Fortschrittsgründen müssen sie das Design so weit wie möglich vorantreiben, bevor der FPGA-Pin-Ausgang abgeschlossen ist. Im Falle eines bekannten Pin-Ausgangs beginnen PCB-Designer, den FPGA-Raum zu planen, und die Designer schließen die Planung gleichzeitig ab, während sie auch erwägen, von anderen Geräten zum FPGA zu führen. Ursprünglich sollte sich das IO auf der rechten Seite des FPGA befinden, befindet sich aber jetzt auf der linken Seite des FPGA, wodurch sich der Pin-Ausgang völlig vom ursprünglichen Plan unterscheidet.

PCB-Designer kann Topologieplanungstools zu Beginn des Entwurfs verwenden, oder sie können sie verwenden, nachdem der Konstrukteur die IP erhalten hat, Je nachdem, wer dieses flexible Tool nutzt, um sich am besten an seine Designumgebung anzupassen. Topologische Verkabelung folgt nur dem Plan oder der Absicht des Designers, zur Verfügung zu stellen hochwertige Leiterplatte Verdrahtungsergebnisse. Bei ECO, Topologieplanung ist viel schneller als ein separater Verbindungsvorgang, So kann Topologie-Verdrahtungsausrüstung ECO schneller annehmen, dadurch schnelle und genaue Ergebnisse.