Multi-Chip-Verpackungen (MCP) erfüllen seit langem die Notwendigkeit, mehr Leistung und Funktionen in einem immer kleineren Raum (PCB) zu verpacken. Es ist natürlich zu erwarten, dass der MCP des Speichers um ASICs wie Basisband oder Multimedia-Prozessoren erweitert wird. Dabei gibt es jedoch Schwierigkeiten, nämlich hohe Entwicklungskosten und Betriebs-/Reduktionskosten. Wie kann man diese Probleme lösen? Das Konzept der kaskadierenden IC Packaging (POP) gewinnt in der Industrie breite Akzeptanz.

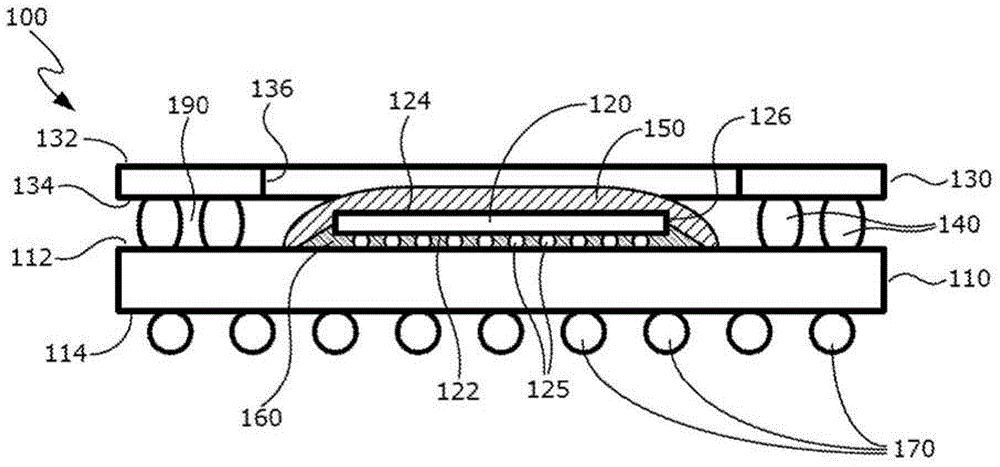

POP (Packaging on Packaging), auch bekannt als Stapelmontage, auch bekannt als Packaging Layer. POP ist ein Paket bestehend aus zwei oder mehr übereinander gestapelten Bgas (Ball-Grid Array Paket). Im Allgemeinen nimmt die Stapelpaketstruktur von POP BGA-Lötkugelstruktur an, die digitale oder gemischte Signallogikgeräte mit hoher Dichte an der Unterseite des POP-Pakets integriert, um die Eigenschaften von mehrpoligen Logikgeräten zu erfüllen. Als neue Art der hochintegrierten Verpackungsform wird POP hauptsächlich in modernen Smartphones, Digitalkameras und anderen tragbaren elektronischen Produkten verwendet und spielt eine sehr große Rolle.

MCP ist eine Hybridtechnologie, die verschiedene Arten von Speicher- oder Nicht-Speicher-Chips unterschiedlicher Größe vertikal in einem Kunststoffgehäuse stapelt. Auf diese Weise spart es Platz auf kleinen Leiterplatten-Leiterplatten.

Aus der Perspektive der Architektur besteht SIP darin, mehrere funktionale Chips, einschließlich Prozessor, Speicher und andere funktionale Chips in einem Paket zu integrieren, um eine grundlegende vollständige Funktion zu realisieren. Aus der Sicht der elektronischen Endprodukte kümmert sich SIP nicht nur um die Leistung/Leistungsaufnahme des Chips selbst, sondern realisiert auch den kurzen, dünnen, multifunktionalen und niedrigen Stromverbrauch der gesamten elektronischen Endprodukte. Nach dem Aufkommen von Leichtbauprodukten wie mobilen Geräten und Trägergeräten wird die SIP-Nachfrage immer deutlicher.

Das Grundkonzept von SoC besteht darin, mehr Geräte auf demselben Bare-Metal-Chip zu integrieren, um das Ziel zu erreichen, Größe zu reduzieren, Leistung zu steigern und Kosten zu senken. Im Mobilfunkmarkt, wo Projektlebenszyklen sehr kurz sind und die Kostenanforderungen sehr anspruchsvoll sind, haben SOC-Lösungen jedoch erhebliche Einschränkungen. Aus Sicht der Speicherkonfiguration erfordern verschiedene Speichertypen viel Logik, und die Beherrschung verschiedener Designregeln und -techniken kann sehr herausfordernd sein, was sich auf die Entwicklungszeit und die Flexibilität der Anwendung auswirkt.

SOC und SIP

SOC ist SIP insofern sehr ähnlich, als beide ein System mit logischen Komponenten, Speicherkomponenten und sogar passiven Komponenten zu einer Einheit kombinieren. Aus konstruktiver Sicht ist SOC ein hoher Grad an Integration der vom System benötigten Komponenten auf einen Chip. Aus Verpackungssicht ist SIP ein Side-by-Side- oder Überlagerungsverfahren für verschiedene Chips. Es ist ein einziges Standardpaket, das mehrere aktive elektronische Komponenten mit verschiedenen Funktionen, optionale passive Geräte und andere Geräte wie MEMS oder optische Geräte integriert, um bestimmte Funktionen zu erreichen.

Im Hinblick auf die Integration integriert SoC grundsätzlich nur logische Systeme wie AP, während SIP AP+ MobiledDR integriert. In gewissem Maße SIP=SoC+DDR. Mit zunehmender Integration in Zukunft wird EMMC wahrscheinlich in SIP integriert werden. Aus der Perspektive der Verpackungsentwicklung hat sich SOC als Schlüssel- und Entwicklungsrichtung des zukünftigen elektronischen Produktdesigns aufgrund der Anforderungen elektronischer Produkte in Bezug auf Volumen, Verarbeitungsgeschwindigkeit oder elektrische Eigenschaften etabliert. Angesichts der steigenden Kosten für die SOC-Produktion und häufigen technischen Hindernissen in den letzten Jahren ist die Entwicklung von SOC jedoch mit Engpässen konfrontiert, wodurch die Entwicklung von SIP in der Industrie immer mehr Aufmerksamkeit erhält.

Entwicklungspfad von MCP zu POP

Combo(Flash+RAM)-Speicherprodukte, die mehrere FLASH NOR, NAND und RAM in einem einzigen Paket integrieren, werden häufig in Mobiltelefonanwendungen verwendet. Diese Einzelpaket-Lösungen umfassen Multi-Chip-Paket (MCP), System-Level-Paket (SIP) und Multi-Chip-Modul (MCM).

Die Notwendigkeit, mehr Funktionalität in immer kleineren Mobiltelefonen bereitzustellen, ist ein wesentlicher Treiber für das Wachstum von MCP, jedoch ist die Entwicklung von Lösungen, die die Leistung verbessern und gleichzeitig eine kleine Größe beibehalten, eine große Herausforderung. Nicht nur die Größe ist ein Problem, sondern auch die Leistung ist ein Problem, wie die Verwendung von MCP-Speicher mit SDRAM- und DDR-Schnittstellen bei der Arbeit mit Basisband-Chipsätzen oder Multimedia-Coprozessoren in Mobiltelefonen.

POP Stack Packaging ist eine gute Möglichkeit, Miniaturisierung mit einem hohen Integrationsgrad zu erreichen. In der Stapelverpackung gewinnt Out-of-Package (POP) in der Verpackungsindustrie, insbesondere in mobilen Anwendungen, aufgrund seiner Fähigkeit, logische Einheiten mit hoher Dichte zu stapeln, zunehmend an Bedeutung.

Vorteile der POP-Verkapselung

1.storage-Geräte und Logikgeräte können separat getestet oder ersetzt werden, um den Ertrag sicherzustellen;

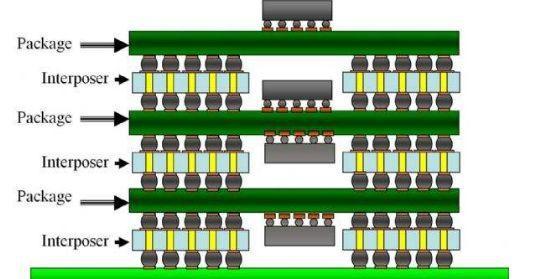

2.Double Schicht POP Paket spart den Substratbereich, und der größere Längsraum ermöglicht mehr Schichten der Verpackung;

3.Mixed DRAM, DDRAMRAM, FLASH und Mikroprozessor entlang der Längsplatte;

4.For verschiedene Hersteller von Chips, bieten Designflexibilität, können einfach gemischt werden, um Kundenbedürfnisse zu erfüllen, die Komplexität und die Kosten des Designs zu reduzieren;

5.Derzeit kann die Technologie verwendet werden, um den Schichtchip in vertikaler Richtung zu überlagern und zusammenzubauen;

6.Die elektrische Verbindung der oberen und unteren Geräte, die zusammen gestapelt werden, realisiert schnellere Datenübertragungsrate und kann mit der Hochgeschwindigkeitsverbindung zwischen Logikgeräten und Speichergeräten fertig werden