Verbindungstechnologie von Kapselchips mit hoher Leistung und Zuverlässigkeit-IC Verpackung

Die Marktentwicklungsrichtung elektronischer Komponenten (für Leiterplattenmontage-PCBA)

Für die ausgereifte LSI-Technologie mit höherer Integration und Geschwindigkeit ist es notwendig, Isolationstechnologie unter Verwendung niedriger K-Materialien zu entwickeln. Aber um die hohe Leistung dieser Geräte zu befriedigen, wird die Isolierung aufgrund der porösen und mehrschichtigen Struktur dünner und dünner. Dadurch wird LSI brüchig. Zum anderen wird der Strom von LSI ständig erhöht, um den hohen Geschwindigkeitsanforderungen gerecht zu werden. Neben der Chipgröße von groß bis klein nehmen auch die Wärmedichte und der Stromverbrauch zu. Daher ist es für das Halbleiter-Verpackungssubstrat (IC Substrat Packaging) in der Zukunft erforderlich, diese Probleme zu lösen, nämlich die Zerbrechlichkeit der Zwischenschichtmedien, hohe Hitze, hohe Geschwindigkeit und niedrige Kosten. Die zukünftige Voraussetzung von Halbleiterprozessen wird in der 20nm Generation und darunter liegen, die viel schwächer sein wird.

Verpackungstechnologie für 20nm Generation erforderlich

Die für die nächste Generation von 20nm erforderliche Spezifikation ist:

Geringe Spannung für spröde niedrige K-Schicht

Hohe thermische Strahlung â¥5W für Hochleistungs-LSI

Hohe Geschwindigkeit â10GHz für hohe Funktionalität

Entwicklungsrichtung Halbleiterverpackungen

Um dem Funktionswachstum und der Kostenreduzierung elektrischer Anlagen einschließlich mobiler Anlagen Rechnung zu tragen, bewegen sich Wafer-Preset-Regeln hin zu größeren und feineren Preset-Regeln. Zu diesem Zweck und um Kosten zu senken, verschiebt sich die Halbleiterverpackungstechnologie schnell von der Standard-Bondtechnologie des Golddrahtbondens auf das Kupferdrahtbonden, wodurch die Menge an Gold reduziert wird. Darüber hinaus hat der Einsatz der Flip-Chip-Bonding-Technologie die höhere Integration und Leistung von LSI sehr zufrieden gestellt. Im 2010-Jahr machten Flip-Chip-Bonding 15 Prozent und Blei-Bonding 85 Prozent der weltweiten Halbleiterverpackungstechnologie aus. Bis 2015 wird erwartet, dass der Anteil der Flip-Chip-Bindung 25 Prozent erreicht, und der Anteil der Blei-Bindung wird voraussichtlich 75 Prozent erreichen. Gerade bei hoher Integration und Hochleistungs-LSI, die hohe thermische Strahlung und hohe Signalgeschwindigkeit erfordern, wird die Flip-Chip-Bonding-Technologie aktiv als angemessen betrachtet.

Flip-Chip-Technologie mit gesundem Menschenverstand

Eignung für niedrige K

Häufig verwendete Flip-Chip-Technologie:

Schweißen benachbarter Flanke, die Hauptstruktur ist C4 (steuerbares Absenkungschip-Co-Zeichen)

Zur Druckverklebung von Au bump und ACF Typ

Ultraschall Bonding für AU-AU Typ Signatur

Druck- und Ultraschallbonden haben hohen Druck und mechanische Schwingungen auf LSI angewendet, so dass diese Methoden nicht für niedrige K LSI verwendet werden können. Aus diesem Grund kann in der obigen Methode C4 nach Bedarf verwendet werden, und aufgrund des Vergleichs der drei Methoden stimmt die Bindung mit der Tatsache überein, dass C4 den Chip am wenigsten schädigt.

Die C4-Technologie wurde Anfang der 40er Jahre für universelle Computer entwickelt und ist seitdem im Einsatz. Mit der steigenden Anzahl an low K Wafern wurde C4 für low K eingesetzt, indem UBM Strukturen, Materialien und Verbesserungen ersetzt wurden.

Neu entwickelte Cu Column Bumps (etwa ähnlich wie bei C4) eignen sich für Inline oder überlappende Pads, nicht für Low K Wafer. Es wurde berichtet, dass die Verkapselung der Cu-Säulenstruktur die niedrige k-Schicht aufgrund des hohen Elastizitätsmoduls von Cu (130GPa) beschädigen kann. Die Abweichung des thermischen Ausdehnungskoeffizienten (CTE) ist der Beschleunigungsfaktor.

Darüber hinaus verwendete die C4-Technologie ursprünglich geschmolzene Metallverbindung nach dem Flussmittel und dem hohen Elastizitätsmodul des Flusses (50GPa), die für angemessen erachtet wurde, so dass die Menge der Spannung zu LSI aufgrund der Differenz in der Heizausdehnung während des Klebens und der Installation der Mutterplatte hinzugefügt wurde. Daher kann die C4-Technologie nicht für zukünftige LSI verwendet werden, die viel schwächer ist.

Wärmestrahlung

Bisher wurden organische Substrate für Flip-Chip-Verpackungen verwendet. Die Wärmeleitfähigkeit organischer Substrate ist klein, 0,5 W/MK, und es ist schwierig, auf LSI mit hohem Stromverbrauch anzuwenden. Wenn ein Kühl- oder Kühlsystem hinzugefügt wird, um thermische Strahlung zu verbessern, steigen die Kosten für Verkapselung, Größe und Höhe der Ebene oder Oberfläche.

Da die Wärmestrahlung gering ist, begrenzt ein bisschen LSI sein Potenzial, um keine große Wärmemenge zu erzeugen. Darüber hinaus steigt, weil die Wärmestrahlung nicht gut ist, die Verbindungstemperatur, der Leckstrom steigt, was den Stromverbrauch weiter erhöht, und der Anstieg des Stromverbrauchs lässt die Temperatur steigen. Es ist ein gefährlicher Teufelskreis. Daher ist die Verbesserung der Wärmestrahlung ein nahes Problem.

Hohe Signalgeschwindigkeit

Der mittlere Schadensverlust der zentralen Schicht des organischen Substrats ist hoch (0.02), und die Impedanz des Durchgangslochs (T/H) der zentralen Schicht ist hoch. Dadurch ist der Einbruchschadensverlust im Hochfrequenzbereich hoch. Die Verwendung kernloser Substrate aus demselben Material wie herkömmliche organische Substrate ist jedoch nicht die grundlegende Lösung. Darüber hinaus können Verbundschichtmaterialien eine Vielzahl von sein, so dass der Benutzer, das beste Material zu wählen, schwieriger ist, die gesamten voreingestellten Anforderungen, um über das Problem der Hochgeschwindigkeitsleistung nachzudenken.

Da das Substrat dünn ist, müssen eine Reihe von Einrichtungen gewechselt werden. Dies wird zum Stolperstein für die Produktion. Aus diesem Grund ist der Transfer auf ein kernloses Substrat risikoreich und nur für lokalisierte Produkte geeignet.

Traditionelle Technologie ist schwierig, die zukünftige 20nm Generation zu befriedigen. Daher ist es notwendig, neue Halbleiterverpackungen mit neuer zentraler Technologie zu entwickeln.

Monsterpac-Typ und Prozessgrundlagen

Monsterpac-typec wurde entwickelt, um den 20nm-Prozess zu erfüllen, der schwer mit der traditionellen Verpackungstechnologie zu passen ist. Dies ist der traditionelle Verpackungsprozess und die Struktur unterscheidet sich absolut von der Verpackung.

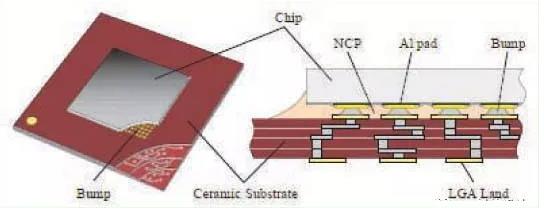

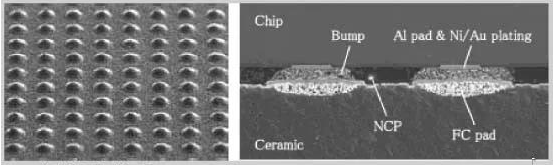

Verkapselungsstruktur

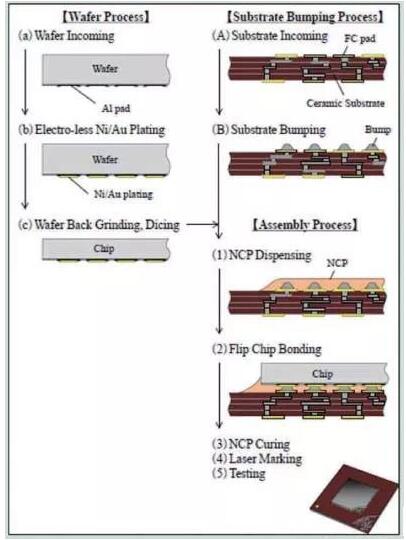

Unsere Verpackungsstruktur, das Substrat ist Keramik, Halbleiterchip mit Bump Flip, Chip und Substratzusatz NCP (nichtleitende Paste). Es wird nicht mit Epoxidgas oder Naturharz gegossen. So ist die Rückseite des Chips freigelegt. Die Hochtemperaturverzug des Reflow-Schweißens ist klein, weniger als 30-50μm, also ist das Paket LGA (Kontaktarray-Paket) ohne Schweißkugeln, nicht BGA (Gitter-Array-Paket). Für Bumps wird eine silberhaltige leitfähige Paste verwendet, die auf das Substrat gedruckt werden, sodass keine Module mehr auf den Pads hergestellt werden. Nicht plattiertes Nickel und Gold nur auf den Al-Pads des Chips ohne Wafer Bump Prozess (Abbildung 1-3).

FIC-1 Verpackungsstruktur

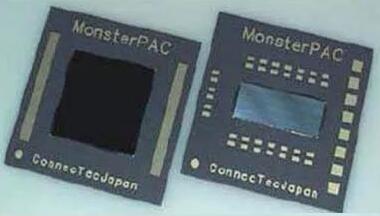

FIC-2 Packaging Image

FIC-3-Verfahren

Im Großen und Ganzen ähnlich wie oben, besteht unser Paket aus nur vier Materialien (Chip, Bump, Keramik und NCP). Diese einfache Struktur sorgt für ein kleines, dünnes und leichtes Paket.

Es gibt zwei Haupttypen keramischer Substratmaterialien: HTCC (Hochtemperatur-Co-Fired Ceramic) und LTCC (Niedertemperatur-Co-Fired Ceramic). Die besonderen Eigenschaften von Keramik (wie elektrische Eigenschaften, Temperaturleitfähigkeit, CTE und Verzug) und Flip-Chip-Bonding ermöglichen es unseren Verpackungen, die beste Lösung für eine Vielzahl von Anforderungen von elektrischen Produkten bis zu Halbleiterchips zu erfüllen.

Monsterpac-artige Struktur ist einzigartig

Die einzigartigen Orte werden wie folgt beschrieben:

Keine Schadensverklebung

Hohe thermische Strahlung

Geringe Einfügedämpfung

Hohe Zuverlässigkeit

Durch die Kombination dieser großen Vorteile gelingt es dem MonsterPac-TypeC, die bestmögliche Leistung für die 20nm-Generation LSI zu liefern.

Keine Schadensbindung

Die Kerntechnologie unseres Pakets ist die schadenfreie Flip-Chip-Bonding-Technologie, die eine beschädigungsfreie und hochzuverlässige Verklebung von Halbleiterchips mit modernster Präzisionsbearbeitung erfolgreich erreicht.

Halbleiterchips ohne Beschädigung beziehen sich auf:

Niederdruckverklebung

Wir können einen Haftdruck von 0.12g/ Bump erreichen, der 1/20 der normalen 2.4g/ Bump des C4 ist. Durch die Reduzierung der Bindungslast auf diese Grenze kann eine Beschädigung des durch die Bindung induzierten interlaminaren Mediums vermieden werden.

Geringe Rückzugsspannung während der konvexen Aushärtung

Die Schrumpfspannung während der Erstarrung des konvexen Punktes ist kleiner als 10MPA/konvexer Punkt, der sehr klein ist. Hohe Streckgrenze und zuverlässige Flip-Chip-Bindung wird erfolgreich durch obere Grenzreduzierung von Temperatur, Last und Rückzugsspannung erreicht, die auf die mittlere Schicht des spröden Mediums (wie niedrige K- und Al-Pads und -Linien usw.) angewendet wird, um Leitungsbruch und Risse zu vermeiden.

Aus diesen Vorteilen ist ersichtlich, dass es das einzige Paket mit der Struktur ist, um schwache niedrige K-Schichtschäden zu vermeiden.

Hohe thermische Strahlung

Erkennend, dass die Kalorien des Halbleiterchips durch das gekapselte Substrat anstelle des gemeinsamen organischen Substrats (Wärmeleitfähigkeit von 0.5W/mk) abgestrahlt werden, wählten wir das keramische Substrat, weil seine Wärmeleitfähigkeit mehr ist als das organische Substrat, das 14W/mk ist. Wenn die Packungsgröße 21*21mm ist und das keramische Substrat verwendet wird, erreicht die Leistungsdissipation 6W, Das ist 1,7-mal höher als das des organischen Substrats mit 3,6W Leistungsdissipation.

Ein niedriges Einführen wird Sie verletzen

Elektronische Anlagen erfordern eine hohe Leistung im Hochfrequenzbereich. Der Einfügungsverlust des keramischen Substrats beträgt 0.42dB (@20GHz, L=5mm), während der des organischen Substrats 0.62dB ist. Die vom keramischen Substrat erlaubte Frequenz beträgt mehr als 10GHz, während die des organischen Substrats 3GHz ist.

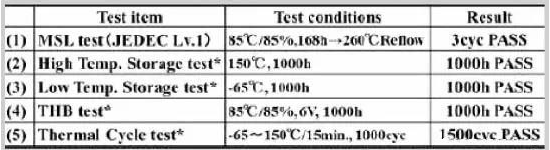

Hohe Zuverlässigkeit und hohe Toleranz gegenüber Feuchtigkeit

Der normale Rückflusswiderstand (MSL: Nässe Level) ist Level 3 (@30DEG /60 100% RH192Hr). Monsterpac-Typ hat jeweils einen Halbleiterchip, der unbeschädigt ist und die Bumps aus nicht verschmolzenem Material bestehen. Bei Hochtemperaturreflow wird die Beule nicht geschmolzen, so dass sie das erneute Schmelzen und die erneute Aushärtung nicht wiederholt, und das Keramiksubstrat leiht keine Feuchtigkeit. Dadurch ist der MonsterPac-TypeC MSL Level 1 (@85DEG /85 100% RH192Hr), er muss nicht vorgebacken werden, um feuchtigkeits- und feuchtigkeitsbeständige Verpackungen zu entfernen, und die Pflanzenlebensdauer des MonsterPac-TypeC ist unbegrenzt.

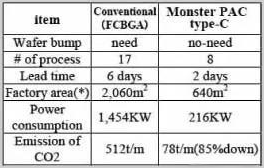

Hohe Anlagenrate

Anstelle von Schweißstößen haben wir eine Epoxidgasstoßstruktur entwickelt, um die Produktion zu erleichtern. Infolgedessen ist eine große Anzahl von Wafer Bump Prozessanlagen erforderlich, die Kosten für eine große Anzahl von Dosen und Wisp Schweißen neben Reflow sind auch notwendig. So kann im Vergleich zu einer konventionellen C4-Prozessanlage gleicher Größe die Größe der Ebene oder Oberfläche der Anlage um 69 Prozent reduziert werden, und der Energieverbrauch der Anlage kann um 85 Prozent reduziert werden. Kann erfolgreich Energieeinsparung und niedrige Hintergrundbelastungsanlage erreichen.

Kapazität

Monsterpac-artiger Prozess einzigartiger Ort

Keramische Technologie stößt

Monsterpac-typec hält es für angebracht, als Stoßmaterial eine silberhaltige leitfähige Paste zu verwenden. Unebenheiten auf dem Keramiksubstrat mit der üblichen SMD-Drucktechnik zu bilden. Es besteht keine Notwendigkeit, die Oberfläche des keramischen Substrats vor der Anhebung der Punktentsorgung vorzudisponieren und zu reinigen und die Oberfläche nach Anhebung der Punktbildung elektroplatinieren. Herkömmliche organische FCBGA erfordert lange Bumps, wie Flux-, Au- und Cu-Bumps, auf den Al-Pads von Halbleiterwafern. Keramikbasierte Bumps erfordern jedoch keinen langen Bumpprozess. Stattdessen produzieren sie auf Halbleiterchips nichtgalvanisches Ni und Au. Die auf Keramiktechnologie basierenden Stöße haben den Prozess der einfachen Entsorgung und niedrigen Kosten erfolgreich realisiert.

Darüber hinaus wurden im Gegensatz zu den harten Beulen (Härte â¯10Hv), die in Techniken des gesunden Menschenverstandes wie Flussmittel-, Au- und Cu-Beulen verwendet werden, weiche Beulen (â¯1Hv) entwickelt, um das Muster unter niedriger Härte zu halten.

Für silberhaltige weiche konvexe Leitpasten haben wir spezielle Fixierpunkte entwickelt, die bei geringer Beanspruchung, geringer Gegenzeichenbeständigkeit und Detailpitchdruck erfahren werden. Die Arbeitskapazität, die wir bisher geformt haben, ist Face Array Pads: Pitch 150μm; Peripheriepads: Stellplatz 75μm. Diese Pad Pitch wird jedoch von der eigentlichen Preset-Regel berücksichtigt, so dass die Surface Array Pitch von 60μm nur für öffnende Bumps anwendbar ist.

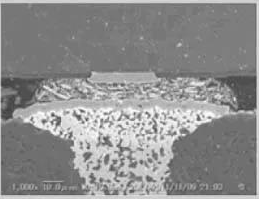

Keine Schadensbindung

Mit der Soft-Flip-Chip-Bonding-Technologie wird der NCP verwendet, um die weichen Stöße zu verteilen, die durch die keramische Bump-Technologie gebildet werden, und dann wird der Halbleiterchip mit dem Flip-Chip verbunden. Während des Klebevorgangs werden die leitfähige Paste der Bumps und des NCP gleichzeitig erstarrt. Dadurch werden sowohl Kosignatur als auch Zuverlässigkeit erfolgreich erreicht.

Die Temperatur der FCB-Anlage liegt unter 200 Grad Celsius, was mehr als 40 Grad Celsius niedriger als die normale Klebetechnik ist. Der Bonddruck ist kleiner als 0.12g/Punkt, der 1/20 der normalen Bondtechnologie ist. Mit diesen Niedertemperatur- und Niederdruck-Heißpressverbindungen werden Halbleiterchips beim Kleben und Nachhärten keiner Belastung und äußeren Kräften ausgesetzt. Mit der neu entwickelten leitfähigen Paste und NCP konnte der schnelle Tastendruck unter 1,0 Sekunden erreicht werden. Das NCP enthält Ergänzungen, die üblicherweise auf beiden Seiten des Chippads und der Bump gefunden werden. Es ist jedoch üblich, die Chiptasten bei niedrigem Druck zu drehen. Die Ergänzung ist in den Beulen vergraben, so dass es die Signatur zwischen dem Chippad und den Beulen nicht beeinflusst. Dies ist einer der Vorteile von weichen Beulen. Nach der Verteilung von NCP vor dem Flip-Chip-Schweißen wird NCP leicht zwischen dem konvexen Punkt und dem schmalen Spalt ergänzt, und mit dem niedrigen Lastschlüssel tritt das Ziel zwischen dem Chip und dem Substrat nicht auf. Daher eignet sich diese Klebetechnik für den Einsatz bei schmalen Padneigungen.

Das Problem mit gängigen Klebetechniken besteht darin, dass beim Flip-Chip-Bonden mit Schweißstößen sehr große Rückzugsspannungen (etwa 200-500 mpa/bump) auf die Bumps und Al-Pads des Halbleiterchips während des Flussschmelzens zur Aushärtung aufgebracht werden. Die Low-Stress-Bonding-Technik ist erfolgreich, da der niedrige Elastizitätsmodul von nicht geschmolzenen konvexen Materialien eine sehr geringe Rückstoßspannung erfordert (weniger als 10MPa/konvex).

Aufgrund des oben genannten Prozesses dieser grundlegenden Technologieentwicklung ist der Erfolg der unbeschädigten Flip-Chip-Verklebung. Fig.4 ist eine Cutaway-Ansicht des Schlüsselpunkts und des Gegenzeichens des Flip-Chips.

FIG-4 Bild- und Schnittfoto

Zuverlässigkeit der Verpackung

TC prüfte das Profil des hinteren konvexen Punktes, aber nicht die Risse und Entkalkung, die durch Bruchkupplung verursacht werden würden.

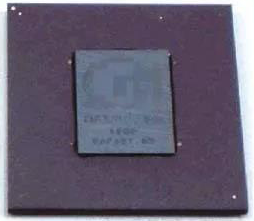

APIC (Applikationsgerät IC)

Die heutige APIC-Verarbeitung bewegt sich in Richtung der Verwendung von K-armen Materialien für die Präzisionsbearbeitung, die hohe Temperaturtoleranz und hohe Geschwindigkeit erfordert. Der Monsterpac-TypeC erfüllt diese Anforderungen mit den unten aufgeführten Vorteilen.

Keine Schadensverklebung

Hohe thermische Strahlung

Bei hoher Geschwindigkeit

Einige APIC-Kunden bewerten den MonsterPAC-TypeC für die Serienfertigung

PAC-TypeC

Durch die tatsächliche Bewertung zwischen dem organischen FCBGA und monsterpac-TypeC unter den gleichen Bedingungen (gleicher Rock, gleicher Chip und gleicher Pad Pitch) liegt die monsterpac-TypeC Temperatur Tj 10° Celsius niedriger als die der organischen Verpackung. Nach einem sehr genauen Vergleich von Tj würde der Unterschied etwa 20° Celsius betragen.

Das HF Board (Radio Frequency Board):

Derzeit verbessert sich die Plattenverkapselung für Hochgeschwindigkeitskommunikation LSI ständig. Diese Abschnitte erfordern spezielle Eigenschaften, die unten aufgeführt sind:

Geeignet für hohe Geschwindigkeit und hohe Frequenz

Geringe Größe klein

Für Hochgeschwindigkeits- und Hochfrequenzanwendungen, wie oben, kann die Verwendung von Keramiksubstrat gegebenenfalls die Einfügedämpfung verbessern, kann für 10GHz verwendet werden.

Darüber hinaus können Multi-Chip und eine hohe Anzahl von SMD-Teilen aufgrund der Verfügbarkeit von kleinen Flip-Chip-Verklebungen in kleinen Paketen verwendet werden.

Zusammenarbeit mit einem Kunden von HF-Platte, entwickelte eine Probe, seine Leistung wurde vom Kunden genehmigt, bereitet sich für die Skalenproduktion vor

HF-Modul

Bei diesen Plattengehäusen ist die Nässe des Substrats sehr dicht. Die MSL von monsterpac-TypeC ist Level 1, so dass es keine Benetzungsgrad Drosselung gibt.

Es zeigt sich, dass monsterPAC-TypeC am besten für Plattenverpackungen geeignet ist, die mehrfaches Reflow-Schweißen für herkömmliche organische Verpackungen SMD und Flip-Chip erfordern.

Richter

Für die kommende Generation von 20nm-Prozessen werden Pakete benötigt, um höhere thermische Strahlung und höhere Geschwindigkeiten aufzunehmen. Allerdings ist die Verpackungstechnologie mit gesundem Menschenverstand schwierig, diese Anforderungen zu erfüllen. Daher ist es notwendig, eine neue Verpackungstechnologie zu entwickeln, die für die 20nm-Prozessgeneration geeignet ist.

Unser Monsterpac-TypeC ist für die kommende 20nm Prozessgeneration geeignet und maximiert die LSI-Leistung. Seine hohe Leistung ist wie ein erstaunliches seltsames Produkt. MonsterPAC, das wir entwickelt haben, machte C4 obsolet und wurde zur Haupttechnologie, die in Zukunft zur nächsten Generation von Halbleitern beiträgt.

Für die nächste Generation der Technologieentwicklung

Forschung und Entwicklung neuer keramischer Substrate

Die Entwicklung der keramischen Substrattechnologie war mehr als hell. Präzises und detailliertes Plotten mit hoher Dichte hinkt bislang weit hinter organischen IC-Substraten zurück.

Um dieses Problem zu lösen und Fortschritte zu erzielen, haben wir uns vorgenommen, ein präzises Keramiksubstrat mit hoher Dichte zu entwickeln, ohne die Kosten zu beeinträchtigen. Unser Ziel ist 20μm Line Pitch, um je nach Bedarf und die Verwendung von Präzision und detaillierten Grafiken flexibler Standard zu erreichen, durch Loch Pitch muss auch präziser und detaillierter sein, das Ziel ist 50μm.

Bisher wurde das Keramiksubstrat je nach Bedarf im Stanz- und Maskendruck hergestellt. Diese bestehenden Techniken beschränken sich sehr auf präzise und detaillierte Zeichnung. Wir denken darüber nach, sie durch Laser- und Direktdruckverfahren zu ersetzen. Die Implementierung dieser Technologie wird eine viel bessere Leistung als organische Substrate bieten. Bisher wurden Keramiksubstrate häufig in High-End-Produkten eingesetzt, aber dieses neue Substrat wird sich an Konsumgüter richten. Und das Substrat braucht wirklich Hochleistungsverbraucherprodukte, um selbst zu wachsen.

Die Kombination dieses Substrats und MonsterPAC-Technologie wird der Welt die beste Leistung und hohe Zuverlässigkeit Printed Circuits Board (PCB) bieten.