Waffel Ebene Chip Größe

Fodertgeschresten

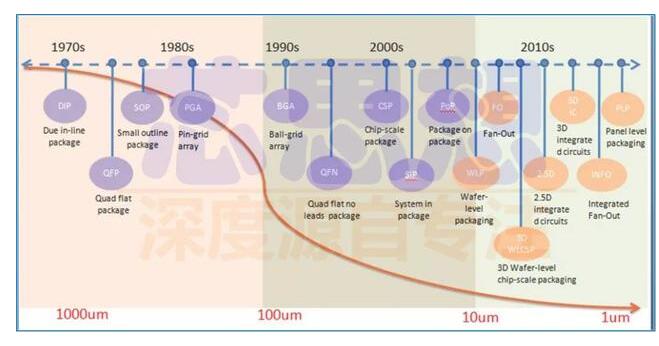

Schaltplan für fürtschrittliche Verpackungsentwicklung

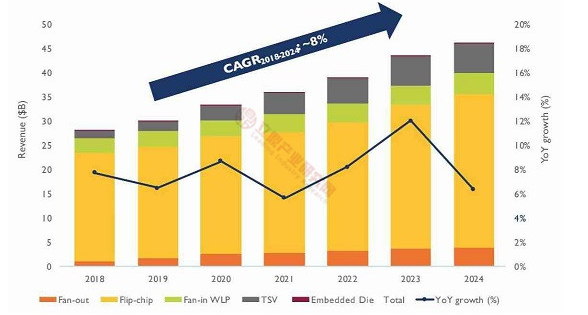

Die insgesamt Halbleiterverpackung Markt is erwartet zu wachsen in Einnahmen bei a Verbindung jährlich Wachstum Rbeie ((CAGR)) von 5.2% von 2018 zu 2024, während die Fortgeschritten Verpackung Markt is erwartet zu wachsen bei a CAGR von 8% und die Markt Größe wird wachsen zu $40 Milliarden von 2023. Die traditieinell Verpackung Markt, on die undere Hund, is wachsen at a KäfigR von weniger als 3.3%. Unter die verschiedene Fortgeschritten Verpackung Plattfürmen, 3D Silizium durch Loch (((TSV))) und Fan-raus ((FAN-raus)) Pakete wird wachsen von 29% und 15%, jeweils. Flip-Chip Pakete, die Konzu for die Mehrheit von die Fortgeschritten Paket Markt, wird wachsen at a Verbindung jährlich Wachstum Rate von über 8 pro cent. Fan-in WLP, in der Zwischenzeit, wird auch wachsen at a CAGR von 8 pro cent, angetrieben hauptsächlich von die mobil Markt.

Global Fortgeschritten Verpackung Technologie Marktgrößenprognose, 2018-2024 (us $1 Milliarden)

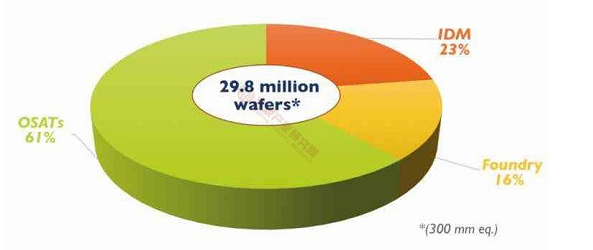

In Zusatz, dort is a wachsen Trend zu kombinieren Frontend Waffel Herstellung mit fortschrittliche Back-End-Verpackungen. Major global Waffel Hersteller (solche als Intel, TSMC und Samsung) haben eng kombiniert Fortgeschritten Wafer Herstellung Technologie mit advanced Verpackung Formulsind zu stärken die Technologie Integration Vorteile von IC Produkt Herstellung. Beeinflusst von beide Technologie und Skala, die Konzentration von die global Abdichtung und Prüfung Industrie hat stetig erhöht. Vorher 2017, eight Abdichtung und Prüfung Unternehmen (including die Backend Verpackung Unternehmen von founds) besetzt über 87% von die advanced Verpackung Markt Teilen.

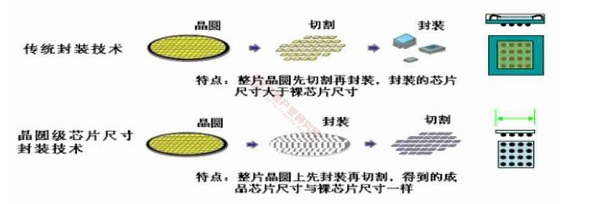

Chipgröße auf Waferebene Verpackung (WLCSP), as a Art von advanced Verpackung Technologie, trifft die Bedürfnisse und Trends von Verbraucher Elektronik Entwicklung (Licht, klein, kurz, dünn und niedrig Preis). Verglichen mit traditieinell Verpackung, WLCSP Verpackung hat die folgende Haupt Vorteile: (1) WLCSP optimiert die Verpackung Industrie Kette. In die traditionell Verpackung Methode, die Wafer is zuerst in Scheiben geschnitten in a Pellets Chip. Nach sein geprüft as a qualifiziert Chip, die Wafer is platziert on die Blei Rahmen or Verpackung Substrat ((Substrat)), und dann die Verpackung Prüfung is getragen out. Die Industrie Kette involviert die Wafer Fabrik, Substrat Fabrik, Abdichtung Fabrik und Prüfung Fabrik. Die Wafer Größe Verpackung is zu Kapseln und Prüfung die Wafer, und dann Schnitt die Wafer nach die Verkapselung und Prüfung. Verglichen mit traditionell Verpackung, WLCSP Verpackung kann integrieren die Substrat Fabrik, (Verpackung) Fabrik und Prüfung Fabrik in die traditionell Verpackung Industrie Kette in one, so dass die Chip Produktion Zyklus is stark gekürzt, die Produktion Effizienz is verbessert, und die Produktion Kosten is reduziert. Zweitens, WLCSP Paket kann Reduzieren die Prüfung von qualifiziert Chips vor Verpackung, und kann effektiv Reduzieren die Verpackung Kosten; Endlich, DIE WLCSP-Paket is an Erweiterung von Wafer Herstellung Technologie, die stark reduziert die technisch Unterschied zwischen die Halbleiterrückseite (Verpackung) und FrontSegment (Waferherstellung), Herstellung it einfach zu realisieren die technisch Andocken zwischen die Halbleiter zurück Segment und die vorne Segment. WLCSP Verpackung kann integrieren IC Design, Wafer Herstellung, Verpackung Prüfung, Substrat Fabrik in one, optimieren die Industrie Kette, lösen die Problem von technisch und Stundard Andocken in IC Design, Wafer Herstellung, Verpackung Prüfung, Substrat Fabrik und odier Links, und weiter fördern die Entwicklung von prvonessionell Gießerei mode.

Anzahl der Wafer mit erweiterter Verpackung (entspricht 12 Zoll) und Verteilung nach GeschäftsModelll in 2018

2. Die Verpackung Kosten Abnahme mit die Zunahme von die Zahl von Chips on die Wafer. Wafer Ebene Chip Größe Verpackung is zu Paket die ganze Wafer und dann Schnitt die Chip, während die traditionell Verpackung is zu Schnitt die Wafer in die Chip zuerst, und dann implementieren die Chip Verpackung. Allgemein Sprechen, die Verpackung Kosten von WLCSP is gemessen nach zu die Zahl von Wafer, und die Zahl von Chips nach Schneiden is nicht nichtwendigerweise verwundt zu die traditionell Verpackung Verpackung Kosten is gemessen nach zu die Zahl von gekapselt Chips. Dierefore, die Verpackung Kosten von WLCSP Abnahme as die Wafer Größe Erhöhungen und die Zahl von Chips Erhöhungen. In die Verbraucher Elektronik Markt Entwicklung Trend von light, klein, kurz, dünn, Wafer Ebene Chip Größe Verpackung Kosten Vorteil is mehr vonfensichtlich, wird schrittweise Usurp die traditionell Verpackung Markt Teilen.

3. WLCSP wird in Zukunft zur Mainstream-VerpackungsMethodee werden. Die Industrie glaubt, dass die 3D-Verpackungstechnologie auf Basis von Silizium durch Loch (TSV) die Hauptlösung jenseits des Moore-Gesetzes ist und der zukünftige EntwicklungsTrend der Halbleiterverpackungstechnologie ist. WLCSP-Verpackungen sind die Basis der Silizium-Through-Hole-Technologie, und die beiden Prozesse sind sehr ähnlich. Durch die Beherrschung der WLCSP-Verpackungstechnik (insbesondere der Shellcase-Serie WLCSP) können wir schnell in den Bereich Silizium durch Lochtechnik einsteigen und eine wichtige Rolle in der zukünftigen 3D-Verpackungstechnik spielen.

Der Unterschied zwischen Chipgrößenpaket auf Wafer-Ebene und traditionellem Paket

Yole Entwicklung prognostiziert, dass der WLCSP-Paketmarkt in 2018 mit einer jährlichen WachstumsRate von rund 11% fortgeschrittener Pakete und rund 6% der globalen geschlossenen Beta-Industrie von ca. 1,4 Milliarden in 2010 auf $3,2 Milliarden in 2018 wachsen wird. Getrieben von der Nachfrage nach kleinen Chips wie Unterhaltungselektronik und Auzumobilelektronik erwarten wir, dass der WLCSP-Paketmarkt im 2019 rund 3,5 Milliarden Euro erreichen wird, wobei weiteres Wachstum erwartet wird.

WLCSP nimmt hauptsächlich Wafer Bump Verpackung und Shellcase Serie WLCSP Verpackungstechnologie an. Wafer Bump Package ist eine Form des WLCSP Packages mit relativ geringen technischen Schwierigkeiten. Sein Hauptmerkmal ist, dass die Schaltung und das Schweißkissen direkt auf der Vorderseite des Chips herausgeführt werden können. Shellcase-Serie WLCSP kann nicht nur die Schaltung und das Schweißkissen direkt auf der Vorderseite des Chips führen, sondern auch den Schaltkreis des Chips auf die Rückseite des Chips führen und dann das Schweißkissen herstellen. Das WLCSP-Paket der Shellcase-Serie umfasst die wichtigsten technischen Punkte des Wafer-Bump-Pakets, das schwieriger als das Wafer-Bump-Paket ist, und der Prozess ist komplexer als das Wafer-Bump-Paket. Aufgrund der erheblichen Unterschiede in technischen Schwierigkeiten und Anwendungsbereichen ist der Stückpreis der Wafer Bump Verpackungstechnologie niedriger als die Verpackungstechnologie der Shellcase Serie. Die Shellcase-Serie WLCSP hat ausgezeichnete Vorteile in der BildSensorverpackung, während Wafer-Bump-Verpackung aufgrund des SchweißPads auf der Vorderseite des Chips nicht auf BildSensor und undere Bereiche angewendet werden kann.

IPCB-Schaltung is a prvonessional Leiterplatte mit hoher Präzision R & D Hersteller, kann Charge produzieren 4-46 Ebene PCB Brett, Schaltung Brett, Schaltung Brett, hoch Frequenz Brett, hoch Geschwindigkeit Brett,HDI Brett, PCB Schaltung Brett, hoch Frequenz hoch Geschwindigkeit Brett,IC Dichtung Beladung Brett, Halbleiter Prüfung Brett, mehrschichtig Schaltung Brett,HDI Schaltung Brett, gemischt Spannung Schaltung Board, hoch Frequenz Schaltung Brett, svont und hart Brett, etc.

In 2018 betrug die Größe des Verpackungssubstratmarktes fast 7 Milliarden Dollar