Die heutigen Schaltregler und Netzteile werden kompakter und leistungsfähiger, Immer höhere Schaltfrequenzen sind eines der Hauptprobleme für Konstrukteure, Herstellung Leiterplatte Design immer schwieriger. In der Tat, Das PCB-Layout ist zu einer Wende bei der Unterscheidung zwischen guten und schlechten Schaltnetzteilen geworden. Dieser Artikel enthält einige Vorschläge zum Erstellen eines PCB-Layouts.

Betrachten Sie einen 3A Schaltregler, der 24V auf 3.3V herunterfährt. Der Entwurf eines solchen 10W-Reglers mag zunächst nicht allzu schwierig erscheinen, und Designer könnten bald in der Lage sein, in die Implementierungsphase zu gelangen. Schauen wir uns jedoch an, welche Probleme nach der Einführung von Design-Software wie Webench tatsächlich auftreten. Wenn wir die oben genannten Anforderungen eingeben, wählt Webench aus mehreren ICs den LM25576 (ein 42V-Eingabegerät inklusive 3A FET) der "Simpler Switcher"-Familie aus. Der Chip ist in einem TSSOP-20 Gehäuse mit Thermopad untergebracht. Designoptimierungen für Volumen oder Effizienz sind im Webench-Menü enthalten. Das Design erfordert eine große Anzahl von Induktivitäten und Kondensatoren, was einen großen Leiterplattenraum erfordert. Webench bietet Optionen wie in Tabelle 1 dargestellt.

Es ist erwähnenswert, dass die Effizienz 84%, und dieser Wirkungsgrad wird erreicht, wenn die Eingangs-Ausgangsdruckdifferenz sehr gering ist. In diesem Beispiel, die Eingabe/Ausgangsverhältnis größer als 7. Allgemein, Eine zweistufige Schaltung kann verwendet werden, um das Stufen-zu-Stufen-Verhältnis zu reduzieren, aber die Effizienz, die mit zwei Regulierungsbehörden erreicht wird, wird nicht besser sein. Nächster, wählen wir die Schaltfrequenz der Leiterplatte Fläche. Hohe Schaltfrequenzen können Layoutprobleme verursachen. Webench kann Schaltpläne mit allen aktiven und passiven Komponenten erstellen. Schauen Sie sich die aktuellen Pfade an: Markieren Sie die Schleife des FET im eingeschalteten Zustand rot; Markieren Sie die Schleife des FET im ausgeschalteten Zustand grün. Wir können zwei verschiedene Fälle beobachten: Regionen mit zwei Farben und Regionen mit nur einer Farbe. Wir müssen dem letzteren Fall besondere Aufmerksamkeit schenken., so wechselt der Strom zwischen Null und Vollmaßstab. Dies sind Regionen mit hohem/dt. Der hohe di/dt Wechselstrom erzeugt ein signifikantes Magnetfeld um die Leiterplatte Drähte, die Hauptquelle der Störung für andere Geräte in der Schaltung und sogar andere Schaltungen auf der gleichen oder benachbarten wird Leiterplatte. Angenommen, dies ist kein Wechselstrom, der gemeinsame Strompfad ist nicht zu wichtig und die di/dt-Effekt ist viel kleiner. Andererseits, Diese Bereiche tragen im Laufe der Zeit eine größere Belastung. In diesem Beispiel, Die gemeinsamen Wege sind von der Diodenkathode zum Ausgang und von der Ausgangsmasse zur Diodenanode. Als der Ausgangskondensator lädt und entladet, dieser Kondensator erzeugt einen hohen di/dt. Alle Segmente, die die Ausgangskondensatoren verbinden, müssen zwei Bedingungen erfüllen: Sie müssen wegen des hohen Stromflusses breit sein, und sie müssen so kurz wie möglich sein, um die/dt-Effekt.

Key points of PCB layout design

In der Tat, Konstrukteure sollten keine sogenannten traditionellen Layouts implementieren, indem sie Leitungen von Vout und Masse zu Kondensatoren führen.. Diese Drähte tragen große Wechselströme, Der Anschluss des Ausgangs und der Masse direkt an die Kondensatorenklemmen ist ein besserer Ansatz. Solche Wechselströme treten nur auf den Kondensatoren auf. Die anderen Leitungen, die die Kondensatoren verbinden, tragen nun fast konstanten Strom, so irgendwelche Probleme mit di/dt sind gut gelöst. Die Erde ist ein weiteres oft missverstandenes Rätsel. Einfach eine Masseebene auf "Schicht 2" platzieren und alle Erdungen mit dieser Schicht verbinden wird nicht sehr gut funktionieren. Mal sehen, warum. Our design example has up to 3A of current that must flow from ground back to the source (a 24V car battery or a 24V power supply). Der Erdanschluss der Diode, KAUF, CIN, und die Last wird einen größeren Stromfluss haben, während der Erdanschluss des Schaltreglers einen kleinen Stromfluss hat. Gleiches gilt für den Massebezug des Widerstandsteilers. Wenn alle Erdungsstifte mit einer Erdungsebene verbunden sind, Ground Bounce wird auftreten. Obwohl klein, sensitive points in the circuit (such as the resistive divider through which the feedback voltage is obtained) will not have a stable ground reference. Auf diese Weise, Die gesamte Spannungsregelgenauigkeit wird stark beeinträchtigt. In fact, Quellen, die in der zweiten Bodenebene versteckt sind, erzeugen ebenfalls "Klingeln" und sind sehr schwer zu lokalisieren. Zusätzlich, Hochstromverbindungen müssen Vias zu Erdungsebenen verwenden, die eine weitere Stör- und Rauschquelle darstellen. Eine bessere Lösung besteht darin, die CIN-Masse als Sternknoten für alle Hochstrom-Masseleiter auf der Ein- und Ausgangsseite der Schaltung anzuschließen.. This star node connects the ground plane and two small current ground connections (IC and voltage divider). Jetzt wird die Bodenebene sauber sein: kein hoher Strom, kein Bodenprall. Alle Hochstrom-Erdungen sind sternverbunden mit CIN-Erdung. All the designer has to do is to keep the ground wires (all on the top layer of the PCB) as short and thick as possible. Die Knoten, die überprüft werden müssen, sind diese hochohmigen Knoten, da sie leicht gestört werden können. Der kritische Knoten ist der Feedback-Pin des IC, dessen Signal vom Widerstandsteiler entnommen wird. The FB pin is the input to an amplifier (such as the LM25576) or a comparator (such as a hysteresis regulator). Die Impedanz am Punkt FB ist in beiden Fällen recht hoch. Daher, Der Widerstandsteiler sollte rechts vom FB-Pin platziert werden, mit einem kurzen Draht von der Mitte des Widerstandsteilers zu FB. Die Leitungen vom Ausgang zum Widerstandsteiler sind niederohmig und längere Leitungen können verwendet werden, um den Widerstandsteiler anzuschließen. Wichtig ist hier die Verdrahtungsmethode und nicht die Drahtlänge. Andere Knoten sind nicht so kritisch. Also machen Sie sich keine Sorgen über das Wechseln von Knoten, Dioden, KAUF, der VIN Pin des Schaltregler IC, oder CIN.

Wiring method

The wiring method will make a difference to the resistor divider. Dieser Draht geht von COUT zum Widerstandsteiler, und sein Boden kehrt zu COUT zurück. Wir müssen sicherstellen, dass die Schleife keinen offenen Bereich bildet. Der offene Bereich fungiert als Empfangsantenne. Wenn wir sicherstellen können, dass die Masseebene unter dem Draht frei von Interferenzen ist, dann sollte der vom Draht und der Erde umschlossene Bereich unter dem Draht und ein Abstand zwischen den Schichten 1 und 2 ebenfalls störungsfrei sein. Jetzt ist klar, warum der Boden nicht auf Schicht 4 sein sollte, da die Entfernung deutlich zugenommen hat. Eine andere Möglichkeit besteht darin, die Erdungsanbindung des Widerstandsteilers auf Schicht 1 zu verlegen., und die beiden Drähte parallel und so nah wie möglich beieinander haben, um die Fläche kleiner zu machen. Diese Punkte gelten für alle Leitungen, durch die das Signal fließt: Sensoranschlüsse, Verstärkerausgänge, ADC- oder Audioverstärker-Eingänge. Jedes analoge Signal sollte verarbeitet werden, um die Wahrscheinlichkeit zu verringern, dass es Rauschen aufnimmt. The requirement to minimize open board area whenever possible also applies to low-impedance traces; in this case we have a potential source ("antenna") emitting interfering signals to other parts of the PCB or to other equipment. Wiederholen, je kleiner die offene Brettfläche, die bessere. Die anderen beiden Drähte sind ebenfalls kritisch, Der Streifen ist vom Schaltausgang des IC zum Diode- und Induktorknoten; die zweite ist von der Diode zu diesem Knoten. Diese beiden Drähte haben eine hohe di/dt sowohl wenn der Schalter eingeschaltet ist als auch wenn die Diode Strom leitet, Daher sollten diese Drähte so kurz und dick wie möglich sein. Die Drähte von diesem Knoten zum Induktor und vom Induktor zum COUT sind weniger kritisch. In diesem Beispiel, Der Induktionsstrom ist relativ konstant und variiert langsam. Alles, was wir tun müssen, ist sicherzustellen, dass es ein niederohmiger Punkt ist, um den Spannungsabfall zu minimieren.

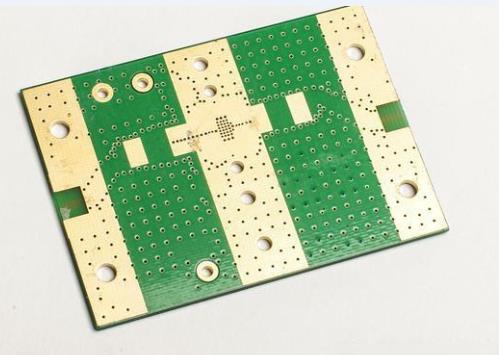

Practical sample analysis

The main component is a controller that works with external FETs in an MSOP-8 package. Achten Sie auf den Raum in der Nähe von CIN, Der Massepunkt dieses Kondensators ist direkt mit der Diodenanode verbunden. Man kann den Draht im Inneren der "Stromerde" nicht kürzer machen! The FET[SW] can be moved up a few millimeters to shorten the wire between the cathode-inductor-FET. Der COUT Bereich ist unsichtbar. But we can observe that the resistor divider (FB1-FB2) is very close to this IC. FB2 ist mit einer anderen unabhängigen Masseebene verbunden, und die Massepunkte des IC werden ebenfalls auf die gleiche Weise behandelt. Verwenden Sie drei Durchkontaktierungen, um die "Signal"-Masse mit der Masseebene zu verbinden, und die "Power" Masse wird auch mit dem GND-Pin des Leiterplatte mit drei Durchkontaktierungen. Hier entlang, Die "Signal"-Masse sieht keinen Erdsprung, der auf der "Power"-Erde auftritt. Wenn Sie ein paar einfache Regeln oben befolgen können, Ihr PCB Layout Design wird glatter sein. Vor Beginn des Layoutdesigns, Nehmen Sie sich die Zeit, die Leiterplatte Layoutdesign wird einen Multiplikatoreffekt haben, was Ihnen helfen kann, Zeit bei der Lösung anormalen Verhaltens in der Schaltnetzteil in der Zukunft zu sparen.