Mit der breiten Anwendung vonPCBA elektronische Produkte, Die Zuverlässigkeit elektronischer Produkte ist zu einem prominenten Problem geworden. Die meisten Anwendungen erfordern einen stabilen Betrieb elektronischer Produkte, zuverlässig und sicher. In der Luftfahrt, Luft- und Raumfahrt, Militär, Kommunikation, Finanzierung, Überwachung und andere Bereiche, Der Ausfall und Ausfall elektronischer Systeme kann große Verluste verursachen.

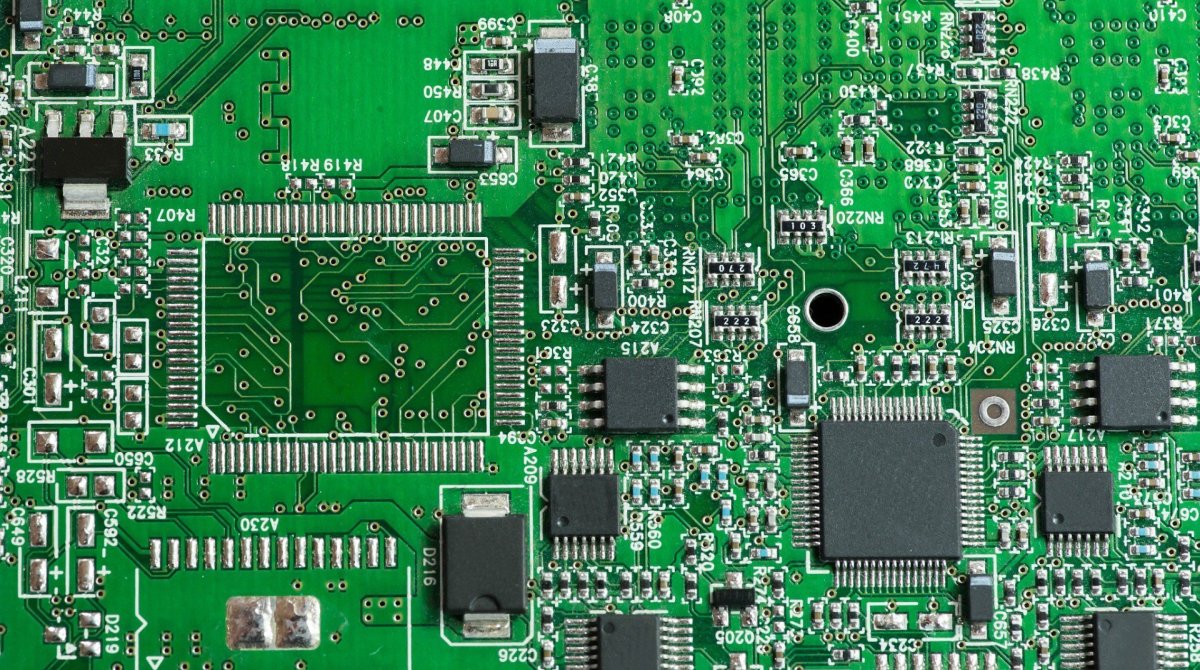

Die Zuverlässigkeit elektronischer Produkte und Systeme ist besonders komplex, da elektronische Produkte aus elektronischen Komponenten bestehen, Leiterplatten, Löte, Zubehör und Software mit komplexen Typen und unterschiedlichen Materialien. Aus der Perspektive der Elektronikproduktherstellung, Die elektronische Fertigung kann in vier Ebenen unterteilt werden, nämlich, level 0 (semiconductor manufacturing), level 1 (PCB design and manufacturing, IC-Verpackung, Herstellung von passiven Bauteilen, manufacturing of process materials and other electromechanical components), level 2 (board level assembly of electronic products), and level 3 (overall assembly of electronic products). Entsprechend vier Klassifizierungsebenen, Die Zuverlässigkeit elektronischer Produkte kann auch in vier Aspekte unterteilt werden. Die Zuverlässigkeit elektronischer Produkte auf Systemebene entspricht der Montage der gesamten Maschine, Die Prozesssicherheit auf Platinenebene entspricht der Prozesssicherheit auf Platinenebene, das ist, die Zuverlässigkeit des Oberflächenmontageprozesses, die Zuverlässigkeit der Komponenten entspricht der Verpackung, Komponenten und Prozessmaterialien, und die Zuverlässigkeit der Halbleiterherstellung entspricht der Zuverlässigkeit des Halbleiterprozesses.

Das Zuverlässigkeitsdesign des elektronischen Montageprozesses umfasst drei Aspekte: Simulationsdesign, Fehleranalyse und Zuverlässigkeitstest. Die Geschäftsentwicklung und Personalbesetzung der Abteilung Prozesssicherheit der branchenführenden Elektronikunternehmen basieren grundsätzlich auf diesem Rahmen. Diese drei Aspekte können die Anforderungen der Montageprozesssicherheit von der qualitativen Analyse bis zur quantitativen Auslegung erfüllen. Aber für die meisten kleinen und mittleren Elektronikunternehmen ist es schwierig, ein solches riesiges System zu etablieren und eine komplette Zuverlässigkeitsabteilung und einen Designprozess zu organisieren. Für sie besteht eine effektivere Methode darin, ihre eigenen Spezifikationen oder Richtlinien für die Zuverlässigkeit des elektronischen Montageprozesses festzulegen, um Maßnahmen zu ergreifen, um Zuverlässigkeitsanforderungen in der PCB-Designphase,PCBA-Montageprozess, Prozessfehleranalyse und Prozesszuverlässigkeitsprüfung sicherzustellen und wenn neue Prozesse auftreten.

Hole (Via) is an important part of Mehrschichtige Leiterplatte, und die Bohrkosten erklären normalerweise 30%~40% der PCB-Produktionskosten. Daher, Durch Design ist ein wichtiger Teil des PCB-Designs geworden. Kurz gesagt, Jedes Loch auf einer Leiterplatte kann ein. Aus der Perspektive der Funktion, Durchkontaktierungen können in zwei Kategorien unterteilt werden: eine wird als elektrische Verbindung zwischen Schichten verwendet; Zweiter, es dient zur Befestigung oder Positionierung von Vorrichtungen. Prozessbezogen, Diese Vias sind im Allgemeinen in drei Kategorien unterteilt, nämlich totes Loch, vergrabenes Loch und Durchgangsloch.

Das tote Loch befindet sich auf der oberen und unteren Oberfläche der Leiterplatte und hat eine bestimmte Tiefe. Es wird verwendet, um die Oberflächenlinie und die untere innere Linie zu verbinden. Die Tiefe der Bohrung überschreitet in der Regel nicht ein bestimmtes Verhältnis (Blende). Eingebettetes Loch bezieht sich auf das Verbindungsloch in der inneren Schicht der Leiterplatten, das sich nicht bis zur Oberfläche der Leiterplatte erstreckt. Das eingebettete Loch befindet sich in der inneren Schicht der Leiterplatte und wird durch den Durchgangslochformungsprozess vor der Laminierung abgeschlossen,

Bei der Lochbildung können sich mehrere innere Schichten überlappen. Die dritte Art von Loch wird Durchgangsloch genannt, das durch die gesamte Leiterplatte verläuft und für interne Verschaltung oder Positionierungsloch der Komponenteninstallation verwendet werden kann. Da das Durchgangsloch in der Technologie einfacher zu realisieren und kostengünstiger ist, verwenden die meisten Leiterplatten es anstelle der anderen beiden Arten von Durchgangsloch. Vom Design-Standpunkt aus besteht ein Durchgangsloch hauptsächlich aus zwei Teilen: Einer ist das Bohrloch in, und der andere ist der Pad-Bereich um das Bohrloch. Die Größe dieser beiden Teile bestimmt die Größe der Vias.

Offensichtlich, bei der Gestaltung Hochgeschwindigkeits-PCB und Leiterplatte mit hoher Dichte, Leiterplattendesigner hoffen immer, dass je kleiner das Loch ist, die bessere, so dass mehr Verdrahtungsraum auf der Leiterplatte gelassen werden kann; Darüber hinaus, je kleiner die Vias sind, je kleiner ihre parasitäre Kapazität ist, die besser für Hochgeschwindigkeitsschaltungen geeignet ist. Allerdings, die Verringerung der Lochgröße führt auch zu einer Erhöhung der Kosten, und die Größe der Durchkontaktierungen kann nicht unendlich reduziert werden, die durch Bohr- und Galvaniktechnik begrenzt ist. Je kleiner das Loch, Je länger das Bohren dauert und desto einfacher ist es, vom Zentrum abzuweichen. Was die aktuelle Leiterplattenherstellungstechnologie betrifft, when the ratio of PCB substrate thickness to aperture (i.e. thickness diameter ratio) exceeds 10, Es ist unmöglich, eine gleichmäßige Kupferbeschichtung an der Lochwand zu gewährleisten, während die Kupferschichtdicke ungleichmäßig ist, besonders in der Mitte der Beschichtung, die Ermüdungslebensdauer der Leiterplatte Loch.