Wenn Sie veruchen, die verschiedenen Signale auf der Platine zu stabilisieren, Probleme mit der Signalintegrität können zu Problemen führen. Das IBIS-Modell ist ein einfacher Weg, diese Probleme zu lösen. Sie können das IBIS-Modell verwenden, um einige wichtige Variablen für die Berechnung der Signalintegrität zu extrahieren und Lösungen fürPCB-Design. Die verschiedenen Werte, die Sie aus dem IBIS-Modell extrahieren, sind integraler Bestandteil der Signalintegritätsberechnungen.

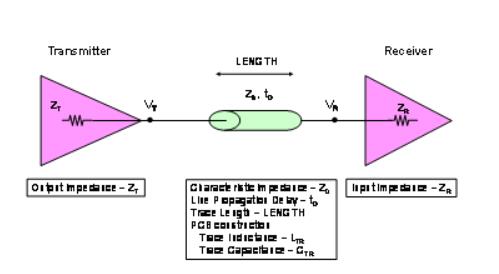

Wenn Sie mit Übertragungsleitungsproblemen in Ihrem System zu tun haben, Sie müssen die elektrische Impedanz und Eigenschaften von integrierten Schaltungen verstehen und PCB Linien. Abbildung 1 zeigt den Aufbau einer einseitigen Übertragungsleitung.

Abbildung 1 Einseitige Übertragungsleitung, die Sender-, Übertragungsleitung- und Empfängerkomponenten verbindet

Was die Übertragungsleitung betrifft, können wir die Sender-Ausgangsimpedanz (ZT, Ω) und Empfänger-Eingangsimpedanz (ZR, Ω) des IC-IBIS-Modells extrahieren. Oft beschreiben die Produktspezifikationen des IC-Herstellers diese Spezifikationen nicht, aber Sie können alle diese Werte über das IBIS-Modell erhalten.

Sie können die Übertragungsleitung mit den folgenden vier Parametern definieren: charakteristische Impedanz (Z0, Ω), Board-Ausbreitungsverzögerung (D, ps/in), Line-Ausbreitungsverzögerung (tD, Sekunden) und Spurlänge (LENGTH, Zoll). Im Allgemeinen beträgt die Z0-Reihe des FR-4 Boards 50Ω bis 75Ω, und die D-Reihe ist 140 ps/in bis 180 ps/in. Die Istwerte von Z0 und D hängen von den materiellen und physikalischen Abmessungen der tatsächlichen Übertragungsleitung ab ("Referenz 1"). Die Leitungsverzögerung (tD) auf einer bestimmten Leiterplatte ist gleich der Ausbreitungsverzögerung (D) multipliziert mit der Länge der verwendeten Leiterbahn (LENGTH). Die Berechnungsmethoden für alle Platten sind:

D1012 Ö (CTR-LTR) oder

D85 ps/in Ö (er)

Z0 Ö (LTR/CTR)

tD bis D

Bei Verwendung des FR-4 Boards beträgt die angemessene Streifenausbreitungsverzögerung 178 ps/inch und die charakteristische Impedanz 50Ω.

Die Senderspezifikation, die für die Bewertung der Signalintegrität verwendet wird, ist die Ausgangsimpedanz (ZT). Bei der Bestimmung der Ausgangsimpedanz liefert der [Pin]-Bereich im IBIS-Modell den parasitären Wert des Widerstands, der Induktivität und der Kapazität jedes Pins. Danach können Sie die Paketkapazität und den Kapazitätswert (C_comp) jedes Puffers für ein klareres Verständnis zusammenfügen.

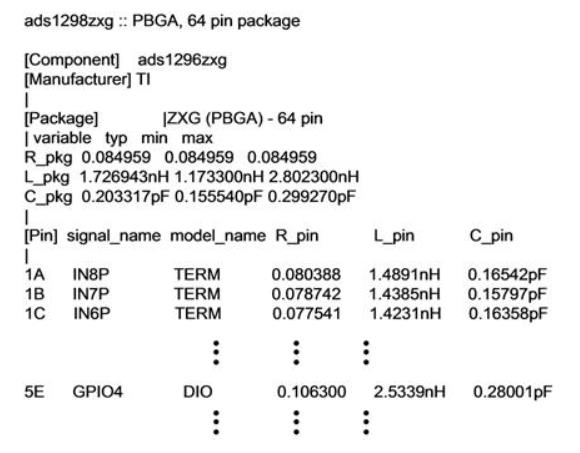

Wie in [Komponente], [Hersteller] und [Paket] oberhalb des Schlüsselworts [Pin] beschrieben, bezieht sich das Schlüsselwort [Pin] auf das spezifische Paket. In der Schlüsselworttabelle [Pin] finden Sie Paketkapazität und Induktivität, da sie mit dem Pin zusammenhängen. Zum Beispiel in der ad129x. ibs Modell ("Referenz 2"), Abbildung 2 zeigt, wo der L_pin Wert und der C_pin Wert des Pin 5E (PBGA, 64-pin Paket) Signal GPIO4 zu finden sind.

Abbildung 2 Package list of ads1296zxg package including C_pin value

Das Signal und das Paket L_pin (Pin Induktivität) und C_pin (Pin Kapazität) sind jeweils 1.489 Nh und 0.28001 pF.

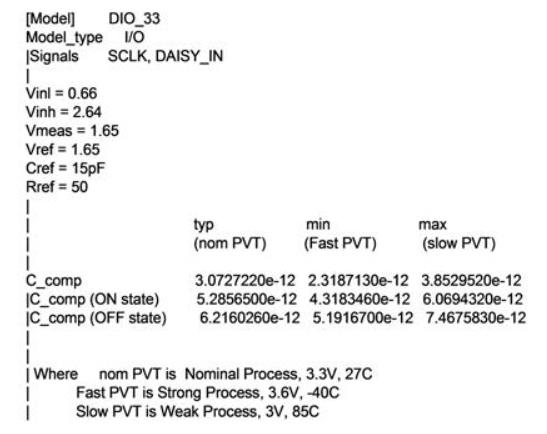

Der zweite wichtige Kapazitätswert ist der C_comp-Wert unter dem Schlüsselwort [Model]. So wie Sie das richtige Modell im IBIS-Modell finden, finden Sie auch eine Liste der C_comp-Werte. Abbildung 3 zeigt ein Beispiel von C_comp im DIO_33 Modell ("Referenz 2").

Abbildung 3 In ad129x. ibs, es ist eine Liste des Modells DIO_33 und der zugehörigen C_comp Werte.

In der Deklaration in Abbildung 3 zeigt das Symbol "➤" einen Kommentar an. Die Liste der gültigen C_comp ("Referenz 3") in dieser Anweisung lautet:

| Typ min max

➤ (nom PVT) (Fast PVT) (langsam PVT)

C_comp 3.0727220e-12 2.3187130e-12 3.8529520e-12

Durch diese Liste, PCB-Designer can choose among three values. In der PCB Entwurfsphase der Übertragungsleitung, der typische Wert von 3.072722 Pf ist die richtige Wahl.

Das IBIS-Modell liefert einige Hinweise für PCB designers, Ermöglicht es ihnen, die Platine zu simulieren, bevor sie mit dem Prototypendesign fortfahren. Wenn Sie die Suchmethode kennen, Das IBIS-Modell kann Ihnen die charakteristische Impedanz und Kapazität aller Pins liefern. Der nächste Schritt in der Auswertung ist die Ermittlung des Inputs/Ausgangswiderstand jedes Puffers, die wir nächstes Mal vorstellen werden.