Gibt es einen Weg für SMT Patch um einige Ausfallprobleme zu reduzieren?

SMT Patch bezieht sich auf die Abkürzung einer Reihe von technologischen Prozessen, die auf der Basis von PCB verarbeitet werden. PCB (Printed Circuit Board) ist eine Leiterplatte. Gibt es also eine Möglichkeit für SMT Patch, einige Fehlerprobleme zu reduzieren?

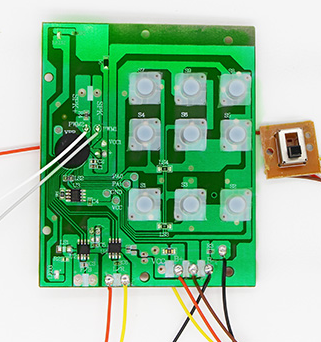

SMT Patch

Der Herstellungsprozess, Hundhabung, and Prüfung der Leiterplattenmontage (PKA) alle unterziehen das Paket einer hohen mechanischen Belastung, die zu einem Ausfall führen können. Wenn das Grid Array Paket größer und größer wird, Das Einstellen der Sicherheitsstufe für diese Schritte wird immer schwieriger.

Seit vielen Jahren ist das monotone Biegepunkt-Prüfverfahren ein typisches Merkmal der Verpackung. Der Test ist in IPC/JEDEC-9702 "Monotonic Bending Characteristics of Board Level Interconnects" beschrieben. Diese Prüfmethode beschreibt die Bruchfestigkeit der horizontalen Verschaltung von Leiterplatten unter Biegebelastung.

Allerdings, Diese Prüfmethode kann die maximal zulässige Spannung nicht bestimmen.

Für den Fertigungs- und Montageprozess, insbesondere für bleifreie PKA, ist eine der Herausforderungen die Unfähigkeit, die Belastung der Lötstellen direkt zu messen. Die am häufigsten verwendete Metrik zur Beschreibung des Risikos von miteinander verbundenen Komponenten ist die Spannung der Leiterplatte neben dem Bauteil, die in IPC/JEDEC-9704 "Printed Wireing Board Strain Test Guidelines" beschrieben ist.

Vor einigen Jahren erkannte Intel dieses Problem und begann, eine andere Teststrategie zu entwickeln, um die schlimmste Biegesituation in der Praxis zu reproduzieren. Andere Unternehmen wie Hewlett-Packard erkannten auch die Vorteile anderer Testmethoden und begannen, ähnliche Ideen wie Intel in Betracht zu ziehen. Da immer mehr Chiphersteller und Kunden erkennen, dass die Bestimmung der Spannungsgrenze zur Minimierung mechanischer Ausfälle während der Herstellung, Handhabung und Prüfung von großem Wert ist, hat diese Methode mehr und mehr Aufmerksamkeit verursacht. Zinsen.

Da die Verwendung bleifreier Geräte zunimmt, sind die Benutzer mehr und mehr interessiert; weil viele Anwender mit Qualitätsproblemen konfrontiert sind.

Angesichts des wachsenden Interesses aller Beteiligten hält IPC es für notwendig, andere Unternehmen bei der Entwicklung verschiedener Testmethoden zu unterstützen, die sicherstellen können, dass BGAs während der Herstellung und Prüfung nicht beschädigt werden. Diese Arbeiten werden gemeinsam von der IPC 6-10d SMT Attachment Reliability Test Method Working Group und dem JEDEC JC-14.1 Packaged Equipment Reliability Test Method Unterausschuss durchgeführt, und die Arbeiten sind abgeschlossen.

Das Prüfverfahren legt acht Kontaktpunkte fest, die in einem kreisförmigen Array angeordnet sind. Die PKA mit einem in der Mitte der Leiterplatte installierten BGA wird auf diese Weise platziert: Das Bauteil wird mit der Vorderseite nach unten auf den Stützstiften montiert, und die Last wird auf die Rückseite des BGA aufgebracht. Platzieren Sie den Dehnungsmessstreifen neben dem Teil gemäß der empfohlenen Spuranordnung von IPC/JEDEC-9704.

Die PKA wird auf das entsprechende Spannungsniveau gebogen, und die Fehleranalyse kann den Grad des Schadens bestimmen, der durch die Ablenkung auf diese Spannungsniveaus verursacht wird. Die iterative Methode kann verwendet werden, um die Spannung zu bestimmen, die keinen Schaden verursacht. Dies ist die Spannungsgrenze.