三次元集積回路のパッケージ化原理及び応用

2.5 D誘電体層は、誘電体層を貫通するシリコンスルーホール(TSV)を用いてシリコン、ガラス、または有機誘電体層上にダイを並べて取り付ける配置である。(中間層の基板としてガラスまたは有機積層板を用いた場合、これらはそれぞれガラス貫通孔(TGV)および基板貫通孔(TSV)と呼ばれる。)コア間の通信は、中間層上に作製された回路によって実現される。

CMOSイメージセンサー(CIS)はTSVを背面穴として相互接続を形成し、リードキーのマージを解消し、サイズを小さくし、密度を高めた。すべてのタイプの3 Dパッケージでは、パッケージ内のチップは通常の回路基板上の個別パッケージに実装されているかのように、チップ外信号を使用して通信します。

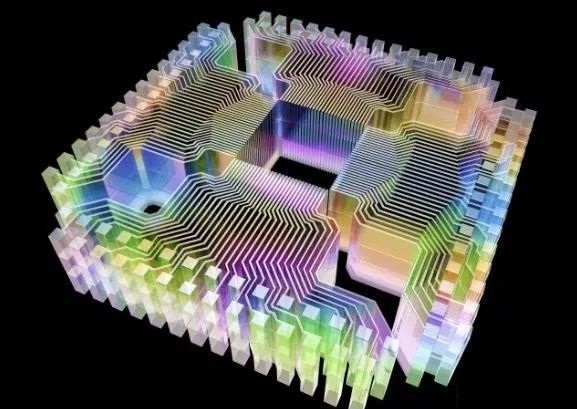

3 D ICは3 DスタックIC(3 D−sic)に分けることができ、これはICチップとTSVがスタックされ相互接続されていることを意味し、真の3 D ICは、FABプロセスを用いて単一チップ上に複数のデバイス層を積層し、非常に微細な間隔のTSVSを用いずに相互接続を形成することができる。

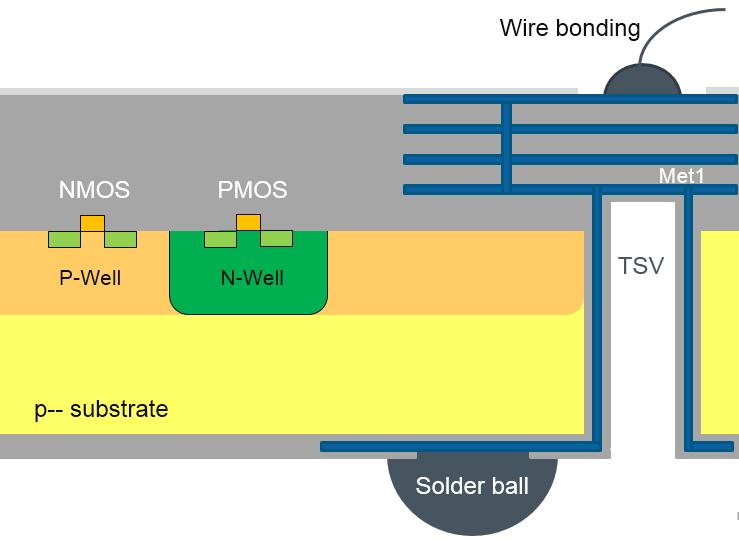

シリコン貫通孔(TSV)は、エッチングプロセスを用いてシリコンウエハ上に形成された孔である。相互接続は、TSVを銅、タングステン、または多結晶シリコンなどの導電材料で充填することにより形成される(図2)。TSV相互接続の主な利点は、1つのチップから次のチップへの信号伝播、または1つの層の回路から別の層の回路への信号伝播経路を短縮することである。これにより、電力を低減し、相互接続密度を高めることができ、機能と性能を向上させることができます。TSV自体は3 D ICではありません。逆に、これらは3次元集積回路を有効にする基礎である。背面貫通孔は、画像センサ、マイクロ電気機械システム(MEMS)、化合物半導体などの他のデバイスにも使用される。

モノリシック3 D ICの意味は何ですか。

モノリシック3 D ICは、ウェハまたはモジュールを積層して3 D ICを作成するのではなく、ベースウェハから始まり、ベースウェハ上に従来のFABデバイスを使用して結晶シリコン、金属層、能動回路、受動回路などの追加の層を追加します(図2)。マイクロメートルの範囲ではなくナノメートルの貫通孔を使用して、チップ間ではなく層間に垂直相互接続を形成する、TSVと同じです。現在、主にメモリアプリケーション用にいくつかの異なる方法が開発されています。Integral 3 Dは、sequential 3 Dと呼ばれることがあります。

3 Dメモリとは?

2つの不揮発性(NANDフラッシュメモリ)と揮発性メモリ(DRAM)デバイススタックメモリに垂直な方法が多数開発されている。DRAM方法は、高帯域幅メモリ(HBM)、Micronのハイブリッドメモリキューブ、Tezzaronの統合RAM(DiRAM)を含む。これらはすべてTSVを用いた3 D IC(図3)に基づいている。サムスン、東芝、多くの他社は、全体的な3 D手法に基づく3 D NANDフラッシュメモリを開発している。

2.5 Dインサータ技術の利点は何ですか。

2.5 D技術は最初は3 D集積回路のブリッジ技術として開発されたが、現在では3 D集積回路との共存が期待されるパッケージプラットフォームに発展している。3 D-ICとは異なり、アクティブコアをパッケージ基板に接続するためにTSVが必要なのは、コア自体ではなく中間層だけです。これにより、既存の金型設計を使用することができます。

3 D統合の主な技術的駆動要因は何ですか。

次世代チップのノードでは、このリソグラフィ工程とウェハ処理のコストが増加し、この業界に代替品を探すよう促し、私たちの電子機器の性能と機能を高め、コストを削減します。また、小型集積のための各種技術(論理、メモリ、RF、センサなど)のニーズは、業界が3 D集積をソリューションとして推進している。

3 D統合の市場駆動要因は何ですか。

3 D統合(3 D統合)の市場駆動力は、ハイエンドコンピューティング、サーバ、データセンター、軍事、航空宇宙、医療機器から始まった。これらの需要量は最大で、現在の3 D統合技術のコストに耐えることができるからだ。タブレット、スマートフォン、ゲーム機器もこの技術を推進している。

3 D集積回路はどのような課題に直面していますか。

多くの人は残りの技術的課題がなく、残りの問題を容易に解決できると主張しているが、2.5 Dおよび3 D集積回路、ウェハ処理、熱管理、テストを計画、実装、検証するための設計ツールなど、より良いソリューションが必要なプロセスステップもある。主な課題は、現在の単位コスト、低数量、および生態系の成熟による実施リスクである。プロセスコストの削減と業界全体のコラボレーションのシンプル化に取り組んでいます。生産量を増やすことはコスト削減に役立ちます。しかし、多くの3 D専門家は、3 D集積回路を実現することはシステムコストを大幅に削減するが、残りの課題は、教育システムレベルのエンジニアがそのシステムに3 D集積回路を設計するメリットであると考えている。

CMOSイメージセンサ(CIS)は、大量のビアバックビアを実現する最初のデバイスの1つです。背面照明付きCIS(BSI)は現在製造中であり、CISはIC上部に積層されているため、3 D ICデバイスである(図2)。Xilinxは2011年にVirtex-7シリーズのすべてのプログラマブルFPGas用に2.5 Dプラグイン設計を発表した。この数年間、Tezzaronは少量のDiRAMを納品してきた。

2014年末には、論理デバイスの上にある3 D DRAMスタックであるハイブリッドストレージキューブ(HMCS)の生産を開始する。SKハイニックスはHMCと高帯域幅メモリ(HBM)を同時に提供する。これらの3 D統合ストレージデバイスは2014/15年に大規模に生産され、その後数年にわたって論理スタックと異機種混在デバイスを使用し続けています。

iPCBはすべての情報を共有します!