先進的なプロセスに加えて、先進的なパッケージはムーアの法則を継続するための重要な技術となっている。近年、2.5 D、3 D、チップなどの技術が半導体業界で話題になっている。高級パッケージはどのようにしてムーアの法則を継続する上で重要な役割を果たしているのだろうか。2.5 D、3 D、Chipletsなどのパッケージ技術の特徴は何ですか。

人工知能、車のインターネット、5 Gなどの応用はすでに現れて、それらはすべて高速計算、高速伝送、低遅延、低エネルギー消費の先進的な機能チップを使用する必要があります。しかし、計算に対する需要が倍増するにつれて、ムーアの法則をどのように継続するかは半導体業界にとって挑戦である。

チップのマイクロ化が難しくなるにつれて、異種集積が生まれてきた。

言い換えれば、半導体先進プロセスは7 nm、5 nm、それから3 nmと2 nmに発展している。そのため、トランジスタのサイズは原子の物理体積限界に近づいている。電子的および物理的な制限により、高度なプロセスの削減とアップグレードを継続することがますます困難になっています。

そのため、先進的なプロセスの開発を続けるほか、半導体業界でもチップの小型化と効率化を維持するための他の方法を探している。チップのレイアウト設計はムーア法則を継続する新しいソリューションとなり、異種集積設計アーキテクチャシステム(HIDAS)の概念が生まれ、集積回路チップの革新的な動力となった。

異種集積とは、広義には、パッケージ、3 Dスタックなどの技術を通じて、メモリ+論理チップ、光電+電子部品などの2種類の異なるチップを集積することである。言い換えれば、2つのプロセスが異なり、性能が異なるチップの集積は異種集積と呼ぶことができる。

アプリケーション市場がより多様化し、製品ごとにコスト、パフォーマンス、ターゲット層が異なるため、必要な異機種混在技術も異なり、市場の焦点が徐々に現れている。そのため、IC OEM、製造、半導体デバイス業界はすべて異性体集積開発を投入し、2.5 D、3 Dパッケージ、Chipletsなどの流行しているパッケージ技術は、春の芽のような異性体集積の理念に基づいている。

2.5 Dパッケージはチップ生産コストを効果的に削減する

従来、チップを統合するには、PiP(パッケージ中)パッケージ、PoP(パッケージ上)パッケージなどのパッケージ中のシステム(SiP)技術が使用されていた。しかし、スマートフォンやAIoTなどの応用としては、より高い性能が必要なだけでなく、小型で低消費電力を維持するためには、より多くのチップを積み重ねて体積を減らす方法を見つけなければならない。そのため、現在のパッケージ技術は従来のSiPに加えて、3次元パッケージ技術にも発展している。

簡単に言えば、3次元パッケージは、従来のプラスチック「ワイヤキャリア」を使用するのではなく、シリコンウェハから直接作られたシリコン中間層(シリコン中間層)を使用し、いくつかの異なる機能を持つチップをより効率的なチップに直接パッケージすることを意味する。言い換えれば、シリコンにシリコンウェハを添加することは、コストとプロセスの物理的制約を増加させ、モル法則を有効に維持することができる。

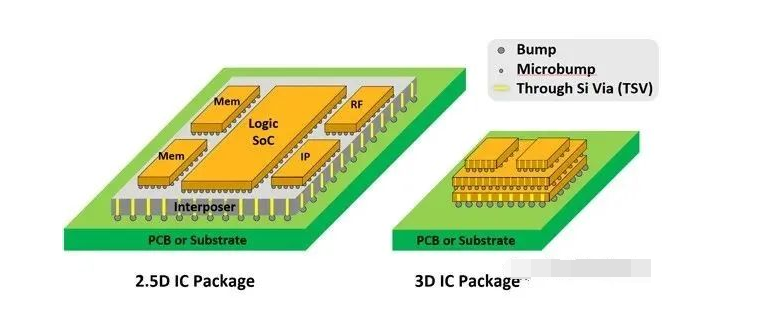

立体パッケージでよりよく知られているのは2.5 Dと3 Dパッケージですが、ここでは2.5 Dパッケージから始めます。2.5 Dパッケージとは、主な概念はシリコン補間器(Silicon Interposer)上にプロセッサ、メモリまたはその他のチップを配置し、シリコン補間機はマイクロバンプ接続を通じて、シリコン補間内の金属線に異なるチップの電子信号を接続できるようにすることである。その後、TSVは下部金属バンプを接続するために使用され、リード支持板は外部金属ボールを接続するために使用され、チップ、チップとパッケージ基板の間のより緊密な相互接続を実現する。

2.5 Dと3 Dパッケージは現在流行している立体パッケージ技術である。(出所:ANSYS)

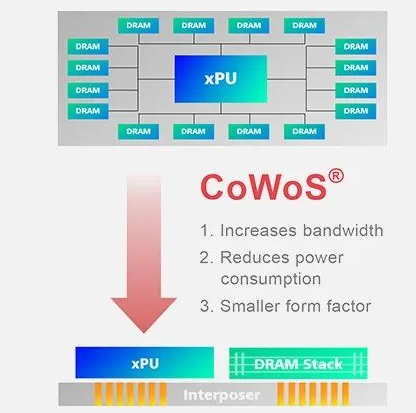

現在よく知られている2.5 Dパッケージ技術は、台積電のCoWoSにほかならない。CoWoS技術の概念は、半導体チップ(例えば、プロセッサ、メモリなど)をシリコン中間層上に置き、その後、ウェハ上チップ(CoW)のパッケージプロセスによってベース基板に接続することである。言い換えれば、まずウェハ上のチップ(CoW)のカプセル化プロセスによってチップをシリコンウェハに接続し、その後CoWチップを基板に接続してCoWoSに集積する。このパッケージモードを使用すると、複数のチップをパッケージ化し、シリコン補間器を介して相互接続することができ、パッケージの体積が小さく、消費電力が低く、ピンが少ないという効果が得られます。

台積電のパッケージ技術理念。(出所:台積電)

CoWosに加えて、扇動ウェハレベルパッケージも2.5 Dパッケージの1つの方法に分類することができる。ファンアウトウエハ段パッケージの原理は、必要な回路をベア半導体の端から再分布層に引き延ばしてパッケージを形成することである。したがって、ロードプレート、ワイヤ、バンプを封止する必要がなくなり、生産コストを30%削減でき、チップを薄くすることもできます。同時に、チップ面積を大幅に減らすことができる。また、よりコストの高いシリコン穿孔の代わりに、パッケージ技術によって異なるコンポーネントの統合を実現することもできます。

もちろん、立体パッケージ技術は2.5 Dだけでなく、3 Dパッケージもあります。では、両者の違いは何ですか。半導体業界では3 Dパッケージが採用されていますか。

2.5 Dパッケージと比較して、3 Dパッケージの動作原理はチップ上にトランジスタ(CMOS)構造を作成し、シリコン穿孔を使用して上下の異なるチップの電子信号を接続することで、メモリや他のチップを直接垂直に積層することができる

3 Dパッケージはチップの直接スタックである。(出典:インテル)

台積電とインテル、3 Dパッケージ技術の積極的な開発

インテル(INTC)と台湾半導体(TSMC)は独自の3 Dパッケージ技術を持っている。インテルは異種スタック論理を使用してオペレーションを処理し、各論理チップをスタックすることができる「Foveros」3 Dパッケージ技術を使用しています。これは、従来の受動シリコン媒体やスタックメモリからcpu、グラフィックス、AIプロセッサなどの効率的な論理製品にチップスタックを初めて拡張することを意味しています。従来、スタックはメモリにのみ使用されていたが、メモリとコンピューティングチップの異なる組み合わせのスタックを実現するために異種スタックが使用されている。

また、インテルはco-EMIB、ODI、MDIOの3つの新技術を開発しています。Co-emibは、より高いコンピューティング性能と能力を接続し、2つ以上のFoverosコンポーネントを相互接続することができます。設計者はまた、シミュレータ、メモリ、その他のモジュールを非常に高い帯域幅と非常に低い消費電力で接続することができます。MODI技術は中小型チップ間の全方位相互接続通信により大きな柔軟性を提供する。トップチップは、Foveros技術などの下のボトムベアチップと垂直にシリコン貫通孔(TSV)を介して通信できるEMIB技術などの他の小型チップと通信することができます。

インテルFoverosテクノロジの概念。(出典:インテル)

この技術はまた、大型垂直貫通孔を用いて、パッケージ基板からトップベアパネルに直接電力を供給する。これらの大きな貫通孔は従来のシリコン貫通孔よりもはるかに大きく、より低い抵抗でより安定した電力伝送を提供する。そして、スタックによってより高い帯域幅とより低い遅延を実現します。この方法はベースチップに必要なシリコン貫通孔の数を減らし、能動素子のためにより多くの面積を空け、裸片のサイズを最適化した。

一方、台積電は「3 Dマルチチップとシステム統合チップ」(SoIC)統合ソリューションを提案している。システム統合されたオンチップソリューションは、異なるサイズ、プロセス技術、材料の既知の良好な裸結晶を直接重ね合わせます。

台積電によると、マイクロバンプを使用した従来の3 D集積回路ソリューションに比べて、このシステムの集積チップは数倍の高いバンプ密度と速度を持ち、同時に消費電力を大幅に低減している。また、システム集積チップは、カプセル化前に2つ以上の裸結晶を接続する前処理集積ソリューションである、そのため、システム統合チップセットは同社のInFOまたはCoWoSバックエンドの先進的なパッケージ技術を利用してさらに他のチップを統合することができ、強力な「3 D*3 D」システムレベルのソリューションを構築することができる。

さらに、卓上電気は、急速に成長する3 DICシステム統合ソリューションを統合し、より柔軟性を提供し、強力なチップ相互接続を持つ強力なシステムを構築する3 DFabricを発売しました。3 DFabricには、複数の論理チップを接続したり、直列高周波幅メモリ(HBM)やアナログ、INPUT/出力、無線周波数モジュールなどの異種の小型チップを接続したりするための異なるフロントチップスタックとバックチップパッケージオプションがあります。3 DFabricは背面と表面の3 Dソリューションを結合し、トランジスタのマイクロモデルを補充し、システムの性能と機能を絶えず向上させ、サイズと外観を縮小し、製品の発売時間を速める。

2.5 Dと3 Dを発売した後、Chipletsは半導体業界に衝撃を与えた最新のパッケージ技術の1つである。最後に、Chipletsの特徴と利点を簡単に紹介します。

Chipletsを使うには3つのメリットがあります。先進的なプロセスのコストは非常に高いため、特にアナログ回路とI/Oはプロセス技術の発展に伴って収縮しにくくなっている。チップは回路を独立した小さなチップに分割し、機能、プロセス技術、サイズを強化し、最終的にはプロセスの小型化の課題を克服するために集積する。また、Chipletsは既存の成熟したチップを使用して開発と検証コストを削減することもできます。

現在、多くの半導体メーカーがチップ方式で高性能製品を発売している。例えば、インテルのIntel Stratix 10 GX 10 m FPGAはチップ設計を採用しており、より高いコンポーネント密度と容量を実現することができます。この製品は既存のIntel Stratix 10 FPGAアーキテクチャとIntelの先進的な組み込みマルチチップ相互接続ブリッジ(emib)技術に基づいて、emib技術を用いて2つの高密度Intel Stratix 10 GX FPGAコア論理チップと対応するI/Oユニットを集積した。AMDの第2世代epycシリーズプロセッサもそうだ。第1世代がメモリとI/Oを結合して14 nm CPUを形成するチップ方法とは異なり、第2世代はI/Oとメモリを1つのチップに分離し、7 nm CPUを8つのチップに切断して組み合わせる。

要するに、従来は半導体プロセスの改良によりチップ効率が向上していたが、素子サイズが物理的限界に近づくにつれてチップの小型化が難しくなってきた。小型で高効率なチップ設計を維持するために、半導体業界は先進的なプロセスを開発し続けるだけでなく、チップアーキテクチャを改善し、チップを元の単層から多層スタックに転向させた。そのため、先進的なパッケージもムーア法則を改善する重要な駆動要素の一つとなり、半導体業界の潮流をリードしている。

未来の知能実験室の主な仕事は:人工知能システムのIQ評価システムを構築し、世界の人工知能IQ評価を展開する、インターネット(都市)クラウド脳研究計画を展開し、インターネット(都市)クラウド脳技術と企業地図を構築し、サービスは企業、業界、都市の知能化レベルを向上させる。