多晶片封裝(MCP)長期以來一直滿足在越來越小的空間(PCB)中封裝更多效能和功能的需求。 期望記憶體的MCP被擴展以包括諸如基帶或多媒體處理器之類的ASIC是很自然的。 但這也有困難,即高昂的開發成本和所有權/减少成本。 如何解决這些問題? 級聯IC封裝(POP)的概念正在業界獲得廣泛接受。

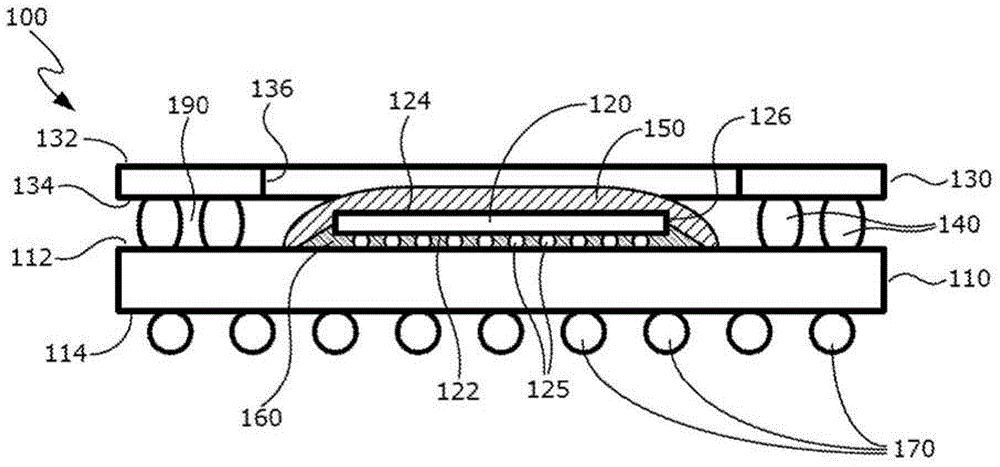

POP(Packaging on Packaging),也稱為堆疊組件,也稱為包裝層。 POP是由兩個或多個bga(球栅陣列封裝)堆疊在一起組成的封裝。 通常,POP的堆疊封裝結構採用BGA焊球結構,在POP封裝底部集成了高密度數位或混合訊號邏輯器件,以滿足多引脚邏輯器件的特點。 POP作為一種新型的高度集成的包裝形式,主要應用於現代智能手機、數位相機等可擕式電子產品中,發揮著非常廣泛的作用。

MCP是一種混合科技,將不同尺寸的各種類型的記憶體或非記憶體晶片垂直堆疊在塑膠封裝的外殼中。 這樣可以節省小型印刷電路板PCB的空間。

從架構的角度來看,SIP是將多個功能晶片,包括處理器、記憶體和其他功能晶片集成到一個封裝中,從而實現基本的完整功能。 從終端電子產品的角度來看,SIP不僅關注晶片本身的效能/功耗,還實現了整個終端電子產品短、薄、多功能、低功耗。 隨著移動設備和穿戴設備等輕量化產品的興起,SIP的需求越來越明顯。

SoC的基本概念是在同一塊裸金屬晶片上集成更多的設備,以實現縮小尺寸、提高效能和降低成本的目標。 然而,在項目生命週期很短、成本要求很高的手機市場中,SOC解決方案存在很大的局限性。 從記憶體配寘的角度來看,不同類型的記憶體需要大量的邏輯,掌握不同的設計規則和科技可能非常具有挑戰性,會影響開發時間和應用程序所需的靈活性。

SOC和SIP

SOC與SIP非常相似,因為兩者都將包含邏輯組件、記憶體組件甚至無源組件的系統合併為一個單元。 從設計的角度來看,SOC是系統所需組件在晶片上的高度集成。 從封裝的角度來看,SIP是一種用於不同晶片的並排或疊加封裝方法。 它是一個單一的標準封裝,集成了具有不同功能的多個有源電子元件、可選的無源器件和其他器件,如MEMS或光學器件,以實現某些功能。

在集成方面,通常SoC只集成AP等邏輯系統,而SIP集成AP+MobileDR。 在某種程度上,SIP=SoC+DDR。 隨著未來集成度越來越高,EMMC很可能會集成到SIP中。 從封裝發展的角度來看,由於電子產品在體積、加工速度或電力特性方面的要求,SOC已被確立為未來電子產品設計的重點和發展方向。 然而,隨著近年來SOC生產成本的不斷提高和科技障礙的頻繁出現,SOC的發展面臨瓶頸,從而使SIP的發展越來越受到業界的關注。

MCP到POP的發展路徑

將多個Flash NOR、NAND和RAM集成在一個封裝中的組合(Flash+RAM)記憶體產品廣泛應用於手機應用中。 這些單封裝解決方案包括多晶片封裝(MCP)、系統級封裝(SIP)和多晶片模塊(MCM)。

在越來越小的手機中提供更多功能的需求是MCP增長的主要驅動力,然而,開發在保持小尺寸的同時提高效能的解決方案是一項艱巨的挑戰。 不僅尺寸是個問題,效能也是個問題,例如在手機中使用基帶晶片組或多媒體輔助處理器時,使用帶有SDRAM和DDR介面的MCP記憶體。

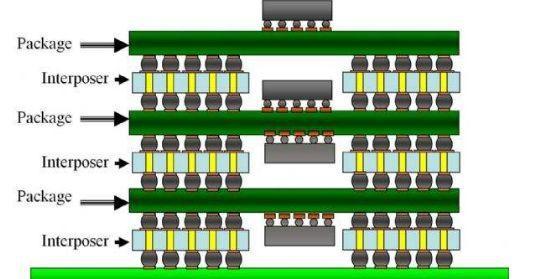

POP堆疊封裝是實現高度集成的小型化的好方法。 在堆疊封裝中,封裝外(POP)由於能够高密度堆疊邏輯單元,在封裝行業,特別是在移動應用中變得越來越重要。

POP封裝的優點

1.儲存設備和邏輯設備可以單獨測試或更換,以確保產量;

2.雙層POP封裝節省了基板面積,更大的縱向空間允許更多的封裝層;

3.沿縱向PCB混合DRAM、DDRAMSRAM、FLASH和微處理器;

4.針對不同廠商的晶片,提供設計靈活性,可以簡單混合在一起滿足客戶需求,降低設計的複雜性和成本;

5.現時,該科技可以用於在垂直方向上覆蓋和組裝層晶片;

6.頂部和底部器件堆疊在一起的電連接實現了更快的資料傳輸速率,可以應對邏輯器件和存儲器件之間的高速互連