三維集成電路封裝原理及應用

2.5D介電層是使用穿過介電層的矽通孔(TSV)將管芯並排安裝在矽、玻璃或有機介電層上的配寘。 (當使用玻璃或有機層壓板作為中間層的基底時,它們分別被稱為穿透玻璃通孔(TGV)和基底通孔(TSV)。) 覈心之間的通信是通過在中間層上製造的電路來實現的。

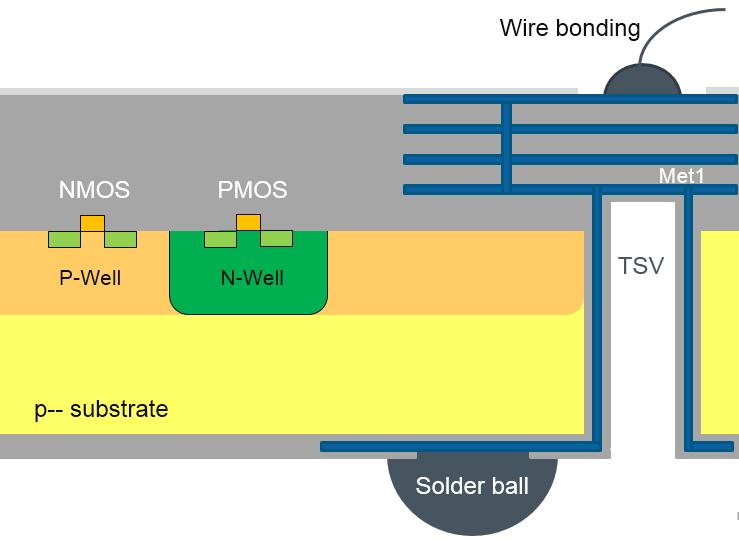

CMOS圖像感測器(CIS)具有TSV作為背面孔以形成互連,消除了引線鍵合併,從而减小了尺寸並提高了密度。 在所有類型的3D封裝中,封裝中的晶片使用晶片外訊號進行通信,就好像它們安裝在普通電路板上的單獨封裝中一樣。

3D IC可以分為3D堆疊IC(3D-sic),這意味著IC晶片與TSV堆疊並互連; 真正的3D IC使用FAB工藝在單個晶片上堆疊多個器件層,可以使用也可以不使用非常精細間隔的TSVS來形成互連。

矽通孔(TSV)是使用蝕刻工藝在矽片上形成的孔。 互連是通過用銅、鎢或多晶矽等導電資料填充TSV而形成的(圖2)。 TSV互連的主要優點是,它們縮短了訊號從一個晶片傳播到下一個晶片或從一層電路傳播到另一層電路的路徑。 這允許降低功率和新增互連密度的能力,從而提高功能和效能。 TSV本身不是3D IC。 相反,它們是啟用三維集成電路的基礎。 背面通孔也用於其他器件,如圖像感測器、微機電系統(MEMS)和化合物電晶體。

單片3D IC的含義是什麼?

單片3D IC不是堆疊晶片或模塊來創建3D IC,而是從基底晶片開始,在基底晶片上使用傳統的FAB器件添加額外的層,如晶體矽、金屬層以及有源和無源電路(圖2)。 使用納米而非微米範圍的通孔在層之間而不是晶片之間形成垂直互連; 與TSV相同。 目前正在開發幾種不同的方法,主要用於記憶體應用程序。 Integral 3D有時被稱為sequential 3D。

什麼是3D記憶體?

已經開發了許多方法來垂直於兩個非易失性(NAND閃存)和易失性記憶體(DRAM)器件堆疊記憶體。 DRAM方法包括高頻寬記憶體(HBM)、Micron的混合記憶體立方體和Tezzaron的集成RAM(DiRAM)。 所有這些都是基於使用TSV的3D IC(圖3)。 三星、東芝和許多其他公司正在開發基於整體3D方法的3D NAND閃存。

2.5D插入器科技的優點是什麼?

2.5D科技最初是作為3D集成電路的橋接技術開發的,現在已經發展成為一個有望與3D集成電路共存的封裝平臺。 與3D-IC不同,只有中間層(而不是覈心本身)需要TSV來將有源覈心連接到封裝襯底。 這允許使用現有的模具設計。

3D集成的主要科技驅動因素是什麼?

在下一代晶片的節點上,這種光刻步驟和晶片處理的成本新增,促使該行業尋找替代品,以提高我們電子設備的效能和功能,降低成本。 此外,對小型集成各種科技(邏輯、記憶體、RF、感測器等)的需求正在推動行業將3D集成作為一種解決方案。

3D集成的市場驅動因素是什麼?

3D集成(3D集成)的市場驅動力始於高端計算、服務器和資料中心、軍事和航空航太以及醫療設備,因為它們的需求量最大,能够承受當前3D集成科技的成本。 平板電腦、智能手機和遊戲裝置也在推動這項科技的發展。

三維集成電路面臨哪些挑戰?

儘管許多人聲稱沒有剩餘的科技挑戰,剩餘的問題可以很容易地解决,但一些工藝步驟仍然需要更好的解決方案,例如用於規劃、實施和驗證2.5D和3D集成電路、晶片處理、熱管理和測試的設計工具。 主要挑戰是現時的組織成本、低數量以及由於生態系統的成熟而帶來的實施風險。 正在努力降低流程成本並簡化整個行業的合作。 新增產量將有助於降低成本。 然而,許多3D專家認為,實現3D集成電路將大大降低系統成本,而剩下的挑戰是教育系統級工程師在其系統中設計3D集成電路的好處。

CMOS圖像感測器(CIS)是最早實現大批量通孔背通孔的器件之一。 帶背面照明的CIS(BSI)目前正在生產中,由於CIS堆疊在IC頂部,囙此它是一個3D IC器件(圖2)。 Xilinx於2011年為其Virtex-7系列的所有可程式設計FPgas推出了2.5D挿件設計。 在過去的幾年裏,Tezzaron已經交付了少量的DiRAM。

2014年底,美光和三星將開始生產混合存儲立方體(HMCS),這是一種位於邏輯設備之上的3D DRAM堆棧。 SK海力士將同時提供HMC和高頻寬記憶體(HBM)。 這些3D集成儲存設備於2014/15年大規模生產,此後幾年繼續使用邏輯堆棧和異構設備。

iPCB將與您分享所有資訊!