除了先進的工藝外,先進的封裝已成為延續摩爾定律的關鍵技術。 近年來,2.5D、3D和晶片等科技已成為半導體行業的熱門話題。 高級封裝究竟是如何在延續摩爾定律中發揮關鍵作用的? 2.5D、3D和Chiplets等封裝技術的特點是什麼?

人工智慧、車聯網、5G等應用已經出現,它們都需要使用高速計算、高速傳輸、低延遲、低能耗的先進功能晶片。 然而,隨著對計算的需求成倍增長,如何延續摩爾定律對半導體行業來說是一個挑戰。

隨著晶片微型化的難度越來越大,異構集成應運而生。

換言之,電晶體先進工藝正在向7nm、5nm,然後是3nm和2nm發展。 囙此,電晶體的尺寸正在接近原子的物理體積極限。 電子和物理限制也使高級流程越來越難以繼續縮減和陞級。

囙此,除了繼續開發先進的工藝外,半導體行業也在尋找其他方法來保持晶片的小型化和高效化。 晶片的佈局設計成為延續摩爾定律的新解決方案,異構集成設計體系結構系統(HIDAS)的概念應運而生,成為集成電路晶片的創新動力。

所謂異構集成,廣義上講,就是通過封裝、3D堆疊等科技,將記憶體+邏輯晶片、光電+電子元器件等兩種不同的晶片集成在一起。 換言之,兩個工藝不同、效能不同的晶片的集成可以稱為異構集成。

由於應用市場更加多樣化,每種產品的成本、效能和目標人群都不同,囙此所需的異構集成科技也不同,市場聚焦趨勢逐漸顯現。 囙此,IC代工、製造和電晶體設備行業都投入了異構集成開發,2.5D、3D封裝、Chiplets等流行的封裝技術,都是基於異構集成的理念,如春意盎然後的春芽。

2.5D封裝有效降低晶片生產成本

過去,要將晶片集成在一起,大多使用封裝中系統(SiP)科技,如PiP(封裝中封裝)封裝、PoP(封裝上封裝)封裝。 然而,作為智能手機、AIoT等應用,不僅需要更高的效能,而且要保持小尺寸、低功耗,在這種情況下,我們必須找到一種方法來堆疊更多的晶片來减少體積,囙此,現時的封裝技術除了原有的SiP外,還朝著三維封裝技術發展。

簡而言之,三維封裝意味著使用直接由矽片製成的矽仲介層(矽仲介層),而不是使用以前的塑膠“導線載體”,並將幾個具有不同功能的晶片直接封裝到一個更高效的晶片中。 換言之,在矽上添加矽片會新增成本和工藝的物理限制,從而使摩爾定律保持有效。

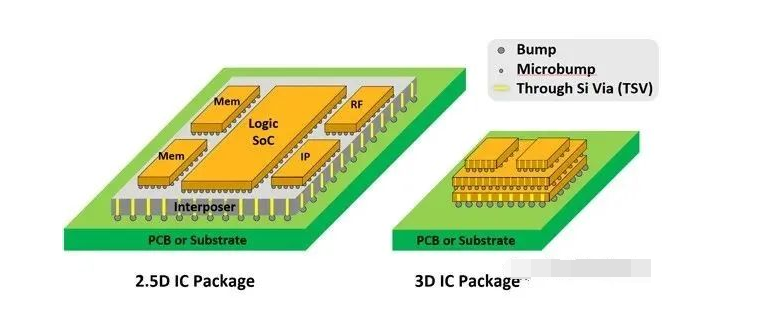

立體封裝更熟悉的是2.5D和3D封裝,這裡我們從2.5D封裝開始。 所謂的2.5D封裝,主要概念是在矽內插器(Silicon Interposer)上佈置處理器、記憶體或其他晶片,矽內插機通過微凸塊連接,使矽內插內的金屬線可以連接不同晶片的電子訊號。 然後,TSV用於連接下部金屬凸塊,導線承載板用於連接外部金屬球,以實現晶片、晶片和封裝基板之間更緊密的互連。

2.5D和3D封裝是現時流行的立體封裝技術。 (來源:ANSYS)

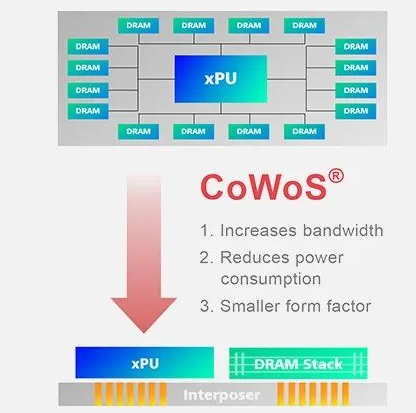

現時眾所周知的2.5D封裝技術無非是台積電的CoWoS。 CoWoS科技的概念是將電晶體晶片(如處理器、記憶體等)放在矽中間層上,然後通過晶片上晶片(CoW)的封裝工藝將它們連接到底部基板上。 換句話說,首先通過晶片上晶片(CoW)的封裝工藝將晶片連接到矽晶片,然後將CoW晶片連接到襯底並集成到CoWoS中。 使用這種封裝模式,可以將多個晶片封裝在一起,並通過矽內插器互連,從而達到封裝體積小、功耗低、引脚少的效果。

台積電的封裝技術理念。 (來源:台積電)

除了CoWos,扇出晶圓級封裝也可以歸類為2.5D封裝的一種方法。 扇出晶圓級封裝的原理是將所需的電路從裸電晶體的末端拉到再分佈層以形成封裝。 囙此,不需要密封加載板、導線、凸塊,這可以將生產成本降低30%,還可以使晶片更薄。 同時,可以大大减少晶片面積。 它還可以取代更高成本的矽穿孔,通過封裝技術實現不同組件的集成。

當然,立體封裝技術不僅僅是2.5D,還有3D封裝。 那麼,兩者之間的區別是什麼,半導體行業正在採用3D封裝?

與2.5D封裝相比,3D封裝的工作原理是在晶片上創建電晶體(CMOS)結構,並使用矽穿孔連接上下不同晶片的電子訊號,這樣記憶體或其他晶片就可以直接垂直堆疊在

3D封裝是晶片的直接堆疊。 (來源:英特爾)

台積電與英特爾積極研發3D封裝技術

英特爾(INTC)和臺灣電晶體(TSMC)擁有自己的3D封裝技術。 英特爾正在使用“Foveros”3D封裝技術,該科技使用異構堆棧邏輯來處理操作,並且可以將每個邏輯晶片堆疊在一起。 這意味著,首次將晶片堆疊從傳統的無源矽介質和堆疊記憶體擴展到cpu、圖形和AI處理器等高效邏輯產品。 過去,堆疊僅用於記憶體,但現在使用異構堆疊來實現記憶體和計算晶片的不同組合的堆疊。

此外,英特爾正在開發三項新技術,即co-EMIB、ODI和MDIO。 Co-emib可以連接更高的計算效能和能力,並允許兩個或多個Foveros組件互連。 設計人員還可以以非常高的頻寬和非常低的功耗連接模擬器、記憶體和其他模塊。 ODI科技為中小型晶片之間的全方位互聯通信提供了更大的靈活性。 頂部晶片可以與其他小型晶片通信,如EMIB科技,它可以通過矽通孔(TSV)與下麵的底部裸晶片垂直通信,如Foveros科技。

英特爾Foveros科技概念。 (來源:英特爾)

該科技還使用大型垂直通孔,直接從封裝基板向頂部裸板供電。 這些大的通孔比傳統的矽通孔大得多,並且以更低的電阻提供更穩定的功率傳輸。 並通過堆棧實現更高的頻寬和更低的延遲。 這種方法减少了基底晶片中所需的矽通孔的數量,為有源元件騰出了更多的面積,並優化了裸片的尺寸。

另一方面,台積電正在提出“3D多晶片和系統集成晶片”(SoIC)集成解決方案。 該系統集成的片上解決方案將不同尺寸、工藝科技和資料的已知良好裸晶體直接疊加在一起。

台積電指出,與使用微凸塊的傳統3D集成電路解決方案相比,該系統的集成晶片具有數倍高的凸塊密度和速度,同時顯著降低了功耗。 此外,系統集成晶片是在封裝之前連接兩個或多個裸晶體的預處理集成解決方案; 囙此,系統集成晶片組可以利用該公司的InFO或CoWoS後端先進封裝技術進一步集成其他晶片,從而創建强大的“3D*3D”系統級解決方案。

此外,台積電推出了3DFabric,它將快速增長的3DIC系統集成解決方案結合在一起,以提供更大的靈活性,並創建具有强大晶片互連的强大系統。 3DFabric具有不同的前晶片堆疊和後晶片封裝選項,可幫助客戶將多個邏輯晶片連接在一起,甚至是串聯高頻寬記憶體(HBM)或類比、INPUT/輸出和射頻模塊等異構小型晶片。 3DFabric結合了背面和正面3D解決方案,並補充了電晶體微縮模型,以不斷提高系統性能和功能,縮小尺寸和外觀,加快產品上市時間。

在推出2.5D和3D之後,Chiplets是衝擊半導體行業的最新先進封裝技術之一。 最後,簡要介紹Chiplets的特點和優點。

使用Chiplets有三個好處。 由於先進工藝的成本非常高,尤其是類比電路和I/O越來越難以隨著工藝科技的發展而收縮。 晶片將電路劃分為獨立的小晶片,增强它們的功能、工藝科技和尺寸,最終將它們集成在一起,以克服工藝小型化的挑戰。 此外,Chiplets還可以使用現有的成熟晶片來降低開發和驗證成本。

現時,許多電晶體製造商已經以晶片的管道推出了高性能產品。 例如,英特爾的Intel Stratix 10 GX 10米FPGA採用晶片設計,可實現更高的組件密度和容量。 該產品基於現有的Intel Stratix 10 FPGA架構和Intel先進的嵌入式多晶片互連橋接(emib)科技,使用emib科技集成了兩個高密度Intel Stratix 10 GX FPGA覈心邏輯晶片和相應的I/O單元。 AMD的第二代epyc系列處理器也是如此。 與第一代將記憶體和I/O結合形成14nm CPU的晶片方法不同,第二代是將I/O和記憶體分離成一個晶片,並將7nm CPU切割成8個晶片進行組合。

總之,過去,晶片效率是通過電晶體工藝的改進來提高的,但隨著元件尺寸接近物理極限,晶片小型化變得越來越困難。 為了保持小尺寸和高效率的晶片設計,半導體行業不僅繼續開發先進的工藝,還改進了晶片架構,使晶片從原來的單層,轉向多層堆疊。 囙此,先進封裝也成為改進摩爾定律的關鍵驅動因素之一,引領了半導體行業的潮流。

未來智慧實驗室的主要工作包括:建立人工智慧系統智商評估體系,開展世界人工智慧智商評估; 開展互聯網(都市)雲大腦研究計畫,構建互聯網(都市”雲大腦科技和企業地圖,服務提升企業、行業和都市的智能化水准。