The main restriction factor of the PCB online function test system is that the reverse driver's ability to absorb/discharge current is too strong, thus covering the failure phenomenon of the input pin of the chip under test. For example, the input pin impedance of most chips is very high (greater than 1 megaohm). If the internal function of the input pin is damaged, the pin impedance may be reduced to about 20 ohms, which will cause fan-out problems in the chip driving the input pin, Circuit failure occurs because most chips can only drive output current of about 10 mA. However, a general reverse drive test instrument can drive an input pin with an impedance of 20 ohms, which enables a chip with a faulty input pin to pass the functional test. QT200 can drive nodes above 8 ohms (less than 8 ohms are regarded as short circuits), which is the main problem of this system.

Reasons for PCB test failure:

Damaged chip function

Speed/timing issues

Chip pin status (floating, high impedance,

Clock, illegal connection)

OC door line or status

Fan-out problem

Classification of ICFT test results

Test passed

Test failed

The device is not fully tested

The devices are the same

Device comparison is not the same

(2) How to deal with different PCB test results

When the "test failed" result appears

Check whether the test fixture is connected to the wrong chip and whether it is well connected to the tested chip. Check whether there is an open pin (display HIZ) from the pin status window, and whether the power pin is detected. Re-test after correcting these problems.

If the result is still "test failed", move the mouse to the pin status window and click the left button to display the pin impedance. Compare the impedance of the pin with the error with the impedance of another pin with the same function. If a test error occurs on a certain output pin of the chip, check whether the impedance of this pin is consistent with other output pins (note that the impedance at this time is the impedance to ground measured when the chip is powered).

If the impedances compared are roughly equal, lower the test time base or threshold value, and then test again. If the test passes this time, it means that the test error of the chip is a timing issue. This may be that the output pin is connected to a capacitive device. Due to the discharge process of the capacitor, the state of the output pin becomes slower. If the test after adjusting the time base or threshold value can pass, you can be 90% sure that the device is not damaged, and you can go to test the next chip at this time.

If the test still fails after adjusting the time base or threshold, check whether isolation is required. If isolation is not required, go directly to step 5.

If it can be seen from the fixture status that the reason for the test failure is that the output pin cannot reach the normal logic level, then lower the test threshold and test again. If the test with a loose threshold value can pass at this time, it means that the load connected to the chip is too heavy, or the output drive capability of the chip itself has deteriorated, and it cannot absorb or discharge the current required by the normal load. When this happens, the user must pay special attention. The solution is to re-test the impedance of the output pin to the ground when the board under test is powered on or not. You can also use the QSM/VI method on the board under test. Test the VI curve of each output pin of the chip under the two states of power-on and power-off.

Compare the measured impedance of each output pin to ground. If the impedance measured without power is approximately the same, and the impedance of the output pin with a test error is higher than the impedance of the other output pins when the power is turned on, it means that the chip function is damaged (high impedance The state cannot absorb or discharge the required current), the chip should be replaced.

Comparing the VI curves of each output pin, if the impedance of a certain output pin is significantly lower than the impedance of other output pins, it means that the problem lies in the fan-out load connected to that pin. Detect the impedance of all chip input pins connected to this pin, and find out the real short-circuit point.

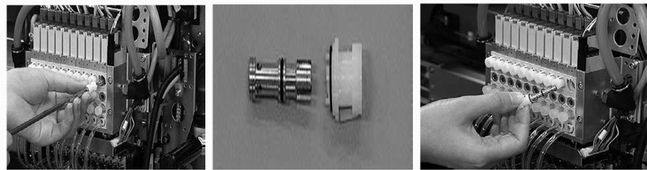

In order to further find out the root cause of the problem, flat-nose pliers can be used to clamp the output pins on the tested chip that have a test error, and then retest. If the test passes at this time, it indicates that it is indeed a problem with the load connected to the chip.

2 When the result of "device not fully tested" appears

When the output pin of the tested chip does not flip during the test (that is, keep a fixed high or low potential in the test window), the system will prompt "the device is not fully tested" (the waveform window on the screen does not appear when the prompt appears) Mark any test errors). For example, an input pin of a 7400 NAND gate is shorted to ground, the corresponding output pin will always be high, and the above prompt will appear when testing the chip.

If the user has the PCB schematic diagram of the board under test, he can easily determine whether the pin connection status of the chip is normal.

If the user has learned a good board, the normal connection status of the learned chip will also be recorded. When testing a bad board, the system automatically compares the learning result with a good board. If the comparison result is different, it means that the bad board has an illegal connection; if the comparison result is the same, you can ignore the "device not fully tested" prompt and go to test the next chip. .

If the chip under test is an OC device and is designed as a "wire-OR" state on the PCB circuit, the output of the chip may be affected by other chips that have a wire-OR relationship with it. For example, if the input logic of a certain chip makes its output fixed at low level, the output of the tested chip will also be fixed at low level. At this time, testing the chip system will also prompt "the device is not fully tested". Users of such devices should pay special attention to it. It is recommended to use the QSM/VI method to judge the PCB fault point by comparing the VI curves of all the same function pins on the test chip.