This article explains how changes in the process cause the actual impedance to change, and how to use accurate field solvers to predict this phenomenon. Even if there is no process change, other factors will cause the actual impedance to be very different. When designinghigh-speed circuit boards, automated design tools sometimes fail to find this unobvious but very important problem. However, as long as some measures are taken in the early steps of the design, this problem can be avoided. This technique is called "defensive design".

The number of stacks

A good laminated structure is the best preventive measure for most signal integrity problems and EMC problems, and it is also the most misunderstood by people. There are several factors at play here, and a good way to solve one problem may worsen other problems. Many system design vendors will suggest that there should be at least one continuous plane in the circuit board to control the characteristic impedance and signal quality. As long as the cost can be affordable, this is a good suggestion. EMC consultants often recommend placing a ground fill or ground layer on the outer layer to control electromagnetic radiation and sensitivity to electromagnetic interference. This is also a good suggestion under certain conditions.

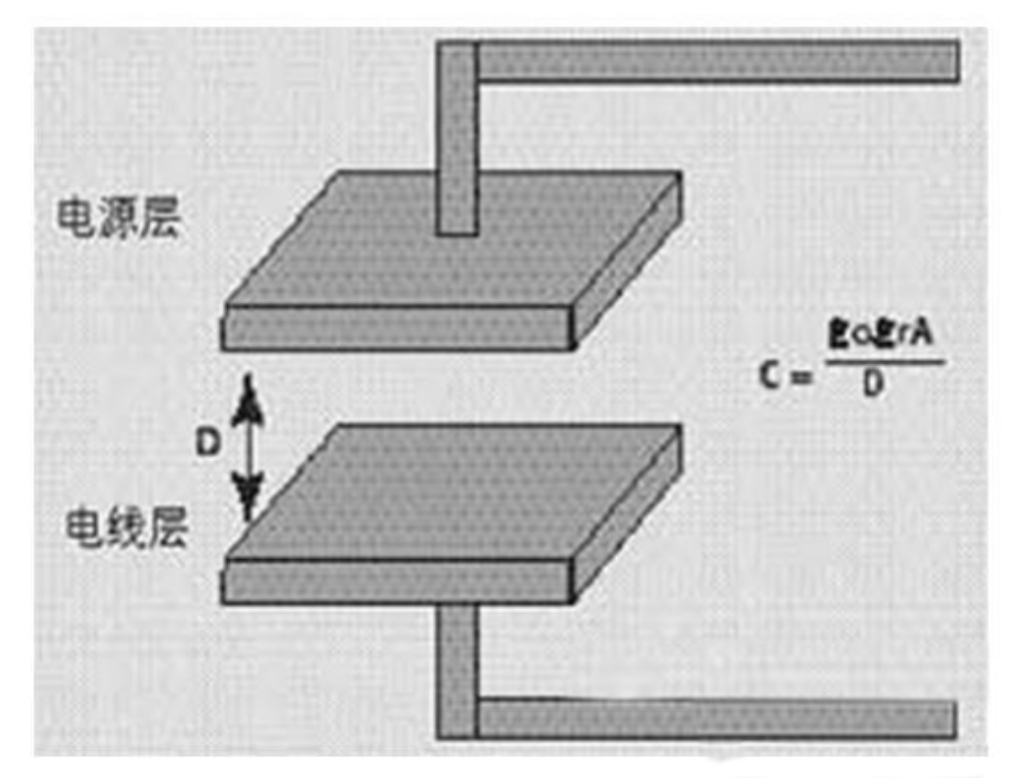

Figure 1: Analyze the signal problem in the laminated structure with the capacitance model

However, due to transient currents, this method may be troublesome in some common designs. First, let's look at the simple case of a pair of power plane/ground plane: it can be seen as a capacitor. It can be considered that the power layer and the ground layer are the two plates of the capacitor. To get a larger capacitance value, it is necessary to move the two plates closer (distance D) and increase the dielectric constant (ε▼r▼). The larger the capacitance, the lower the impedance, which is what we want because it can suppress noise. No matter how the other layers are arranged, the main power layer and the ground layer should be adjacent and in the middle of the stack. If the distance between the power layer and the ground layer is large, it will cause a large current loop and bring a lot of noise. For an 8-layer board, placing the power layer on one side and the ground layer on the other side will cause the following problems:

1. Maximum crosstalk. Due to the increase in the mutual capacitance, the crosstalk between the signal layers is greater than the crosstalk of the layers themselves.

2. The largest circulation. Current flows around each power plane and parallel to the signal, a large amount of current enters the main power plane and returns through the ground plane. The EMC characteristics will deteriorate due to the increase of the circulating current.

3. Loss of control over impedance. The farther the signal is from the control layer, the lower the accuracy of impedance control due to other conductors around it.

4. Because it is easy to cause solder short circuit, it may increase the cost of the product.

We have to make a trade-off choice between performance and cost, so how to arrange the digital circuit board to get the best SI and EMC characteristics?

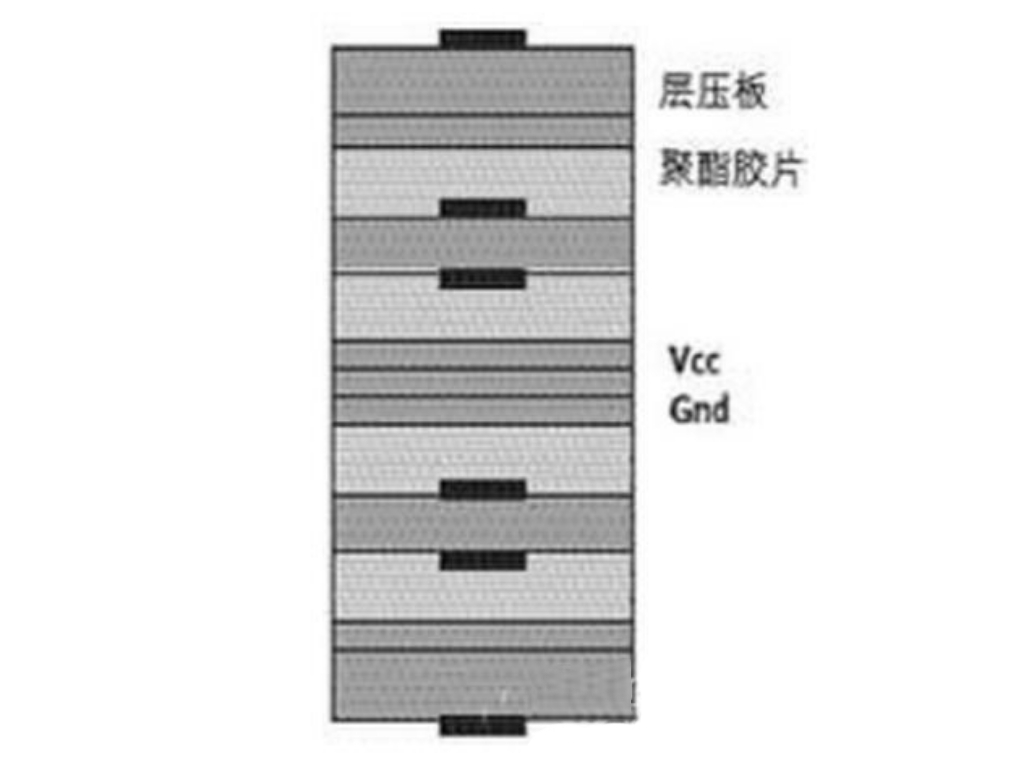

The distribution of each layer of the PCB is generally symmetrical. More than two signal layers should not be placed next to each other; otherwise, the control over SI will be largely lost. It is best to place the internal signal layers symmetrically in pairs. Unless some signals need to be wired to SMT devices, we should minimize the signal wiring on the outer layer.

Figure 2: The first step of a good design solution is to correctly design the laminated structure

For circuit boards with more layers, we can repeat this placement method many times. It is also possible to add additional power layers and ground layers; as long as it is ensured that there is no pair of signal layers between the two power layers.

The wiring of high-speed signals should be arranged in the same pair of signal layers; unless this principle has to be violated due to the connection of SMT devices. All traces of a signal should have a common return path (that is, the ground plane). There are two ideas and methods to judge what two layers can be regarded as a pair:

1. Ensure that the return signals at equal distances are exactly the same. This means that the signals should be routed symmetrically on both sides of the internal ground plane. The advantage of this is that it is easy to control the impedance and circulating current; the disadvantage is that there are many vias on the ground layer, and there are some useless layers.

2. Two signal layers of adjacent wiring. The advantage is that the vias in the ground layer can be controlled to a minimum (using buried vias); the disadvantage is that the effectiveness of this method is reduced for some key signals.

In the second method, the ground connection for driving and receiving the signal should preferably be directly connected to the layer adjacent to the signal wiring layer. As a simple wiring principle, the surface wiring width in inches should be less than one-third of the drive rise time in nanoseconds (for example, the wiring width of high-speed TTL is 1 inch).

If it is powered by multiple power supplies, a ground layer must be laid between the power supply wires to separate them. Capacitors cannot be formed to avoid AC coupling between power supplies.

The above-mentioned measures are all in order to reduce the circulation and crosstalk, and strengthen the impedance control ability. The ground plane will also form an effective EMC "shielding box". Under the premise of considering the influence on the characteristic impedance, the unused surface area can be made into a ground layer.

Characteristic impedance

A good laminated structure can effectively control the impedance, and its wiring can form an easy-to-understand and predictable transmission line structure. On-site solution tools can handle such problems well, as long as the number of variables is controlled to a minimum, quite accurate results can be obtained.

However, when three or more signals are stacked together, this is not necessarily the case, and the reason is subtle. The target impedance value depends on the process technology of the device. High-speed CMOS technology can generally reach about 70Ω; high-speed TTL devices generally can reach about 80Ω to 100Ω. Because the impedance value usually has a great influence on noise tolerance and signal switching, it is necessary to be very careful when choosing impedance; the product manual should give guidance on this.

The initial results of the on-site resolution tool may encounter two kinds of problems. The first is the problem of restricted view. The field solution tool only analyzes the influence of nearby traces, and does not consider non-parallel traces on other layers that affect impedance. The on-site solution tool cannot know the details before wiring, that is, when assigning the trace width, but the above-mentioned pair arrangement method can minimize this problem.

It is worth mentioning the influence of partial power planes. The outer circuit board is often crowded with grounded copper wires after wiring, which is beneficial to suppress EMI and balance plating. If only such measures are taken for the outer layer, the laminated structure recommended in this article will have a very small effect on the characteristic impedance.

The effect of using a large number of adjacent signal layers is very significant. Some on-site solution tools cannot find the presence of copper foil, because it can only check the printed lines and the entire layer, so the impedance analysis result is incorrect. When there is metal on the adjacent layer, it acts like a less reliable ground layer. If the impedance is too low, the instantaneous current will be large, which is a practical and sensitive EMI problem.

Another reason for the failure of impedance analysis tools is distributed capacitors. These analysis tools generally cannot reflect the influence of pins and vias (this influence is usually analyzed with a simulator). This effect can be significant, especially on the backplane. The reason is very simple: the characteristic impedance can usually be calculated by the following formula: √L/C

Among them, L and C are the inductance and capacitance per unit length respectively.

If the pins are arranged evenly, the additional capacitance will greatly affect the calculation result. The formula will become: √L/(C+C')

C'is the pin capacitance per unit length.

If the connectors are connected in a straight line as on the backplane, the total line capacitance and the total pin capacitance except the first and last pins can be used. In this way, the effective impedance will be reduced, and may even drop from 80Ω to 8Ω. In order to find the effective value, the original impedance value needs to be divided by: √(1+C'/C)

This calculation is very important for component selection.

delay

When simulating, the capacitance of the component and package (and sometimes inductance should also be included) should be considered. Two issues should be paid attention to. First of all, the simulator may not be able to correctly simulate distributed capacitors; secondly, it is necessary to pay attention to the impact of different production conditions on incomplete layers and non-parallel traces. Many on-site solution tools cannot analyze stack distribution without full power or ground planes. However, if there is a ground layer adjacent to the signal layer, then the calculated delay will be quite bad, such as a capacitor, there will be the largest delay; if a double-sided board has a lot of ground wires and VCC copper foil on both layers, This situation is even more serious. If the process is not automated, setting up these things in a CAD system will be very messy.

EMC

There are many factors affecting EMC, many of which are usually not analyzed. Even if they are analyzed, it is often too late after the design is completed. The following are some factors that affect EMC:

1. The slots in the power plane constitute a quarter-wavelength antenna. For occasions where installation grooves are required on metal containers, drilling methods should be used instead.

2. Inductive components. I once met a designer who followed all the design rules and made simulations, but his circuit board still has a lot of radiation signals. The reason is that there are two inductors placed parallel to each other on the top layer to form a transformer.

3. Due to the influence of the incomplete ground plane, the low impedance of the inner layer causes a large transient current in the outer layer.

Most of these problems can be avoided by adopting a defensive design. First of all, the correct stack structure and wiring strategy should be made, so that a good start can be made.

Some basic issues are not covered here, such as network topology, signal distortion causes and crosstalk calculation methods; only some sensitive issues are analyzed to help readers apply the results obtained from the EDA system. Any analysis depends on the model used, and unanalyzed factors will also affect the results. Being too complicated is like being too inaccurate. Avoiding too many parameter changes (such as printed line width, etc.) will help a neat and consistent design.