Zusammenfassung der Zeichnung der Leiterplatte Technologie:

(1): Beim Zeichnen des Schaltplans muss die Pin-Beschriftung das Netzwerk verwenden. NET verwenden Sie nicht den Text TEXT, sonst wird es Probleme beim Führen des PCB-Designs geben

(2): Beim Zeichnen des Schaltplans müssen alle Komponenten verpackt sein, sonst werden die Komponenten nicht gefunden, wenn die Leiterplatte geführt wird

Einige Leiterplattenkomponenten Kann nicht in der Bibliothek gefunden werden und ich muss sie selbst zeichnen. In der Tat, Ich zeichne sie immer noch selbst.. Endlich, es gibt eine eigene Bibliothek, was bequem ist. Der Zeichnungsprozess ist, um FILE zu starten/NEU-"SCH LIB auswählen-"Dies wird in die Bauteilbearbeitungsbibliothek gelangen-"Nach Zeichnung, Klicken Sie auf TOOLS-RENAME COMPONENT, um die Komponente umzubenennen.

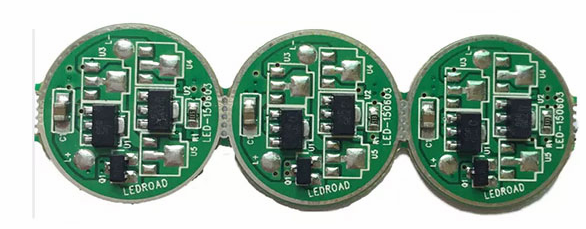

Das Bild des Komponentenpakets ist dasselbe wie dieses, aber die PCB LIB ist ausgewählt, und der Rand der Komponente befindet sich auf der TOPOverlay-Schicht, die gelb ist.

(3): Benennen Sie nach dem Zeichnen die Komponenten in der Reihenfolge um, wählen Sie Werkzeug ---- - "ANNOTATE Anmerkung und wählen Sie dann die Reihenfolge

(4): Vor der Umwandlung in PCB sollte ein Bericht generiert werden, hauptsächlich Netzliste. Wählen Sie DESIGN design----ãNetlist erstellen, um Netzliste zu erstellen

(5): Eine andere Sache ist, die elektrischen Regeln zu überprüfen: wählen Sie TOOLS. > ERC

(6): Dann kann die Leiterplatte erzeugt werden. Wenn es einen Fehler im Generierungsprozess gibt, muss der Schaltplan korrigiert werden und dann wird die Leiterplatte generiert.

(7): Die Leiterplatte muss zuerst ein gutes Spiel machen. Die Linie sollte so kurz wie möglich sein und die Anzahl der Durchgänge sollte so gering wie möglich sein.

(8): Entwurfsregeln vor dem Zeichnen der Linie: TOOLS-Design Rules, GAP-Design von Clearance Constrain in Routing, 10 oder 12 kann ausgewählt werden, Durchgänge werden in ROUTING VIA STYLE gesetzt, der maximale Außendurchmesser des Hanpan ist der kleinste Die Größe des Außendurchmessers, der größte Innendurchmesser und der kleinste Innendurchmesser. WIDTh Constraint legt die Breite der Linie, Maximum und Minimum fest

(9): Die Breite der gezeichneten Linie ist im Allgemeinen 12MIL, die Peripherieleistung und Erdungslinie ist 120 oder 100, die Leistung und Masse des Chips sind 50 oder 40 oder 30, und die Kristalllinie sollte dick sein und neben dem Mikrocontroller platziert werden. Die öffentliche Linie sollte dick sein, die Langstreckenlinie sollte dick sein, die Linie kann nicht im rechten Winkel gedreht werden, und die Linie sollte 45 Grad sein. Die Stromversorgungs-, Erdungs- und andere Schilder müssen im TOPLAY markiert sein, um das Debuggen der Verbindung zu erleichtern.

Wenn Sie feststellen, dass das Diagramm falsch ist, müssen Sie zuerst das Schaltplandiagramm ändern und dann das Schaltplandiagramm verwenden, um die Leiterplatte zu ändern.

(10): Die untere Option in der VIEW-Option kann Zoll oder Millimeter wählen.

(11): In order to improve the anti-interference of the board, Es ist am besten, Kupfer zuletzt aufzutragen, Wählen Sie das verkupferte Symbol, und ein Dialogfeld erscheint. In der Abbildung, Netzoption wählt das angeschlossene Netzwerk aus, und die beiden unten stehenden Optionen sollten ausgewählt werden, HATZSTIL, Wählen Sie die Form der Kupferbeschichtung, das ist willkürlich. GRID SIZE ist der Abstand von Kupfergitterpunkten. Die eingestellte Linienbreite TRACK WIDTH sollte mit der Leiterplattenleitenbreite wir zogen auf. LOCKCrimitives vergleichen und wählen, und die anderen beiden können wie im Bild gezeigt gemacht werden.

Das obige ist eine Zusammenfassung der Leiterplattenzeichnetechnologie