Neben fortschrittlichen Prozessen ist fortschrittliche Verpackung zu einer Schlüsseltechnologie geworden, um Moores Gesetz fortzusetzen. Technologien wie 2,5D, 3D und Chiplets sind in den letzten Jahren zu heißen Themen in der Halbleiterindustrie geworden. Wie genau spielen fortschrittliche Verpackungen eine Schlüsselrolle bei der Fortsetzung des Moore-Gesetzes? Was sind die Eigenschaften von Verpackungstechnologien wie 2,5D, 3D und Chiplets?

Künstliche Intelligenz (KI), Internet der Fahrzeuge, 5G und andere Anwendungen sind entstanden, und sie alle müssen fortschrittliche funktionale Chips mit High-Speed-Computing, Hochgeschwindigkeitsübertragung, niedriger Latenz und niedrigem Energieverbrauch verwenden. Da die Nachfrage nach Computern jedoch mehrfach wächst, stellt die Weiterführung des Moore-Gesetzes eine Herausforderung für die Halbleiterindustrie dar.

Da die Chip-Mikroskala schwieriger wird, entsteht heterogene Integration.

Mit anderen Worten, fortgeschrittene Halbleiterprozesse bewegen sich in 7 nm, 5 nm und dann 3 nm und 2 nm. Transistorgrößen nähern sich daher den physikalischen Volumengrenzen von Atomen. Elektronische und physikalische Einschränkungen machen es auch für fortgeschrittene Prozesse immer schwieriger, weiter zu schrumpfen und zu aktualisieren.

Daher sucht die Halbleiterindustrie neben der Weiterentwicklung fortschrittlicher Verfahren auch nach anderen Möglichkeiten, Chips klein und effizient zu halten. Das Layout Design von Chips wird dann zu einer neuen Lösung, um Moores Gesetz fortzusetzen, und das Konzept des heterogenen Integration Design Architecture System (HIDAS) entsteht im historischen Moment und wird zum Innovationsimpuls von ICchips.

Die sogenannte heterogene Integration, im Großen und Ganzen, ist die Integration von zwei verschiedenen Chips, wie Speicher-Logik-Chip, photoelektrische und elektronische Komponenten, etc., durch Verpackung, 3D-Stack und andere Technologien. Mit anderen Worten, die Integration von zwei Chips mit unterschiedlichen Prozessen und unterschiedlichen Eigenschaften kann heterogene Integration genannt werden.

Da der Anwendungsmarkt diversifizierter ist, sind die Kosten, die Leistung und die Zielpopulation jedes Produkts unterschiedlich, so dass die erforderliche heterogene Integrationstechnologie auch unterschiedlich ist, und der Marktfokustrend tritt allmählich auf. Daher haben IC-Gießerei-, Fertigungs- und Halbleiterausrüstungsindustrie in heterogene Integrationsentwicklung investiert, 2.5D-, 3D-Verpackungen, Chiplets und andere beliebte Verpackungstechnologie basiert auf der Idee der heterogenen Integration, wie Bambussprossen nach einer Frühlingsfeder.

Verpackung 2.5D reduziert effektiv die Kosten der Chipproduktion

In der Vergangenheit, um Chips zusammen zu integrieren, wurde der größte Teil der System in a Package (SiP)-Technologie verwendet, wie PiP (Package in Package) Verpackung, PoP (Package on Package) Verpackung. Da Smartphones, AIoT und andere Anwendungen jedoch nicht nur höhere Leistung benötigen, sondern auch, um eine kleine Größe und einen niedrigen Stromverbrauch beizubehalten, müssen wir in einem solchen Fall einen Weg finden, mehr Chips zu stapeln, um das Volumen zu reduzieren, also die aktuelle Verpackungstechnologie zusätzlich zum ursprünglichen SiP, aber auch in Richtung der dreidimensionalen Verpackungstechnologie Entwicklung.

Kurz gesagt bedeutet dreidimensionales Verpacken den Einsatz von Silicon Interposer (Silicon Interposer), der direkt aus Siliziumwafern hergestellt wird, anstatt den bisherigen Kunststoff "Drahtträger" zu verwenden und mehrere Chips mit unterschiedlichen Funktionen direkt in einen effizienteren Chip zu verpacken. Mit anderen Worten, das Hinzufügen von Siliziumchips auf Silizium, auf eine Weise, die die Kosten und physikalischen Einschränkungen des Prozesses erhöht, hält Moores Gesetz am Leben.

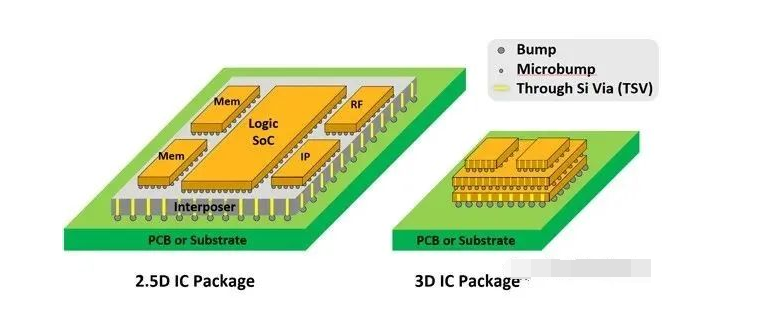

Und das stereoskopische Paket ist mit 2.5D und 3D-Paket vertrauter, hier beginnen wir vom 2.5D-Paket. Das sogenannte 2.5D-Paket, das Hauptkonzept besteht darin, Prozessoren, Speicher oder andere Chips auf dem Silizium-Interposer (Silizium-Interposer) anzuordnen, der durch Micro Bump verbunden ist, so dass die Metalldrähte im Silizium-Interposer die elektronischen Signale verschiedener Chips verbinden können. Dann wird der TSV verwendet, um den unteren Metallstoß zu verbinden, und die Drahtträgerplatte wird verwendet, um die externe Metallkugel zu verbinden, um eine engere Verbindung zwischen Chip, Chip und Verpackungssubstrat zu erreichen.

2.5D und 3D Verpacken sind beliebte Stereoverpackungstechnologie. (Quelle: ANSYS)

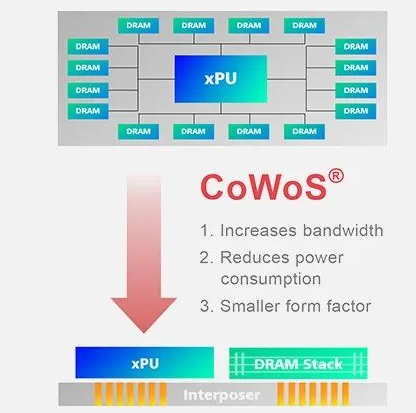

Die derzeit bekannte 2,5D-Verpackungstechnologie ist nichts anderes als CoWoS von TSMC. Das Konzept der CoWoS-Technologie besteht darin, Halbleiterchips (wie Prozessoren, Speicher usw.) auf der Silizium-Zwischenschicht zusammenzulegen und sie dann durch den Verpackungsprozess von Chip on Wafer (CoW) mit dem unteren Substrat zu verbinden. Mit anderen Worten, der Chip wird zuerst durch den Verpackungsprozess von Chip on Wafer (CoW) mit dem Siliziumwafer verbunden, dann wird der CoW-Chip mit dem Substrat verbunden und in CoWoS integriert. Mit diesem Verpackungsmodus können mehrere Chips zusammen verpackt und durch Si Interposer miteinander verbunden werden, um den Effekt von geringem Verpackungsvolumen, niedrigem Stromverbrauch und weniger Pins zu erzielen.

TSMC CoWos Verpackungstechnologie Konzept. (Quelle: TSMC)

Neben CoWos kann die Fan-Out Wafer Level Verpackung auch als Methode der 2,5D Verpackung klassifiziert werden. Das Prinzip der Fan-Out Wafer-Level-Verpackung besteht darin, erforderliche Schaltkreise von den Enden des nackten Halbleiters zur Redistribution Layer zu ziehen, um Verpackungen zu bilden. Daher besteht keine Notwendigkeit, die Ladeplatte, Draht, Bump zu versiegeln, die die Produktionskosten um 30% reduzieren und den Chip auch dünner machen kann. Gleichzeitig kann die Spanfläche stark reduziert werden. Es kann auch die höheren Kosten durch Silizium-Perforation ersetzen, um das Ziel der Integration verschiedener Komponenten durch Verpackungstechnologie zu erreichen.

Natürlich ist Stereoverpackungstechnologie nicht nur 2.5D, es gibt auch 3D-Verpackungen. Was ist also der Unterschied zwischen den beiden, und die SEMICONDUCTOR-Industrie setzt auf 3D-Verpackungen?

Im Gegensatz zum 2.5D-Gehäuse arbeitet das 3D-Gehäuse, indem eine Transistorstruktur (CMOS) auf dem Chip erstellt wird und Siliziumdurchführungen verwendet werden, um die elektronischen Signale verschiedener Chips oben und unten zu verbinden, so dass der Speicher oder andere Chips direkt vertikal gestapelt werden können.

Die 3D-Verpackung ist ein direkter Stapel von Chips. (Quelle: Intel)

TSMC und Intel entwickeln aktiv 3D-Verpackungstechnologie

Intel (INTC) und Taiwan Semiconductor (TSMC) verfügen über eigene Technologien für 3D-Verpackungen. Intel verwendet die 3D-Verpackungstechnologie "Foveros", die heterogene Stack-Logik verwendet, um Operationen zu handhaben und jeden Logic-Chip zusammen stapeln kann. Damit wird das Chip-Stacking erstmals von traditionellen passiven Silizium-Mediatoren und gestapeltem Speicher auf hocheffiziente Logikprodukte wie CPU-, Grafik- und KI-Prozessoren erweitert. Früher wurde Stacking nur für den Speicher verwendet, heute wird heterogenes Stacking verwendet, um verschiedene Kombinationen von Speicher und Rechenchips zu gestapelt.

Darüber hinaus entwickelt Intel drei neue Technologien, nämlich co-EMIB, ODI und MDIO. Co-emib kann sich mit höherer Rechenleistung und -fähigkeit verbinden und zwei oder mehr Foveros-Komponenten miteinander verbinden. Designer können auch Simulatoren, Speicher und andere Module mit sehr hoher Bandbreite und sehr niedrigem Stromverbrauch verbinden. Die ODI-Technologie bietet mehr Flexibilität für die omnidirektionale Verbindungskommunikation zwischen kleinen und mittleren Chips. Der obere Chip kann mit anderen kleinen Chips wie der EMIB-Technologie kommunizieren, und er kann vertikal mit dem unteren nackten Chip unten durch ein Silizium-Durchgangsloch (TSV) wie die Foveros-Technologie kommunizieren.

Intel Foveros Technologie Konzept. (Quelle: Intel)

Die Technologie verwendet auch große vertikale Durchgangslöcher, die Strom direkt vom Verpackungssubstrat zur oberen blanken Platte liefern. Diese großen Durchgangslöcher sind viel größer als herkömmliche Silizium-Durchgangslöcher und bieten eine stabilere Kraftübertragung mit niedrigerem Widerstand. Und durch den Stack, um höhere Bandbreite und niedrigere Latenz zu erreichen. Dieser Ansatz reduziert die Anzahl der Silizium-Durchgangslöcher, die im Basischip benötigt werden, wodurch mehr Fläche für das aktive Element frei wird und die blanke Blattgröße optimiert wird.

TSMC hingegen schlägt eine Integrationslösung für "3D Multi-Chip und System Integrated Chip" (SoIC) vor. Die systemintegrierte On-Chip-Lösung kombiniert bekannte gute blanke Kristalle unterschiedlicher Größen, Verfahrenstechnologien und Materialien direkt übereinander.

TSMC stellt fest, dass die integrierten Chips des Systems eine mehrfach höhere Stoßdichte und Geschwindigkeit aufweisen und gleichzeitig den Energieverbrauch deutlich senken als herkömmliche 3D-integrierte Schaltungslösungen, die Mikrobumps verwenden. Darüber hinaus sind systemintegrierte Chips vorprozessintegrierte Lösungen, die zwei oder mehr nackte Kristalle vor dem Verpacken verbinden; Infolgedessen kann der System Integration Chipsatz die fortschrittliche Backend-Verpackungstechnologie InFO oder CoWoS des Unternehmens nutzen, um weitere Chips zu integrieren und so eine robuste "3D*3D"-Systemlösung zu schaffen.

Darüber hinaus hat TSMC 3DFabric eingeführt, das die schnell wachsenden 3DIC-Systemintegrationslösungen zusammenführt, um mehr Flexibilität zu bieten und leistungsstarke Systeme mit robuster On-Chip-Verbindung zu schaffen. Mit verschiedenen Optionen für Front-Chip-Stacking und Back-Chip-Verpackung hilft 3DFabric Kunden, mehrere Logic-Chips miteinander zu verbinden, sogar Tandem High Frequency Wide Memory (HBM) oder heterogene kleine Chips wie Analog-, INPUT/Output- und RF-Module. 3DFabric kombiniert 3D-Lösungen von hinten und vorne und ergänzt Transistor-Miniaturen, um Systemleistung und Funktionalität kontinuierlich zu verbessern, Größe und Aussehen zu reduzieren und die Produkteinführungszeit zu verkürzen.

Nach der Einführung von 2,5D und 3D ist Chiplets eine der neuesten fortschrittlichen Verpackungstechnologien, die die Halbleiterindustrie erreicht hat. Abschließend noch eine kurze Beschreibung der Funktionen und Vorteile von Chiplets.

Es gibt drei Vorteile bei der Verwendung von Chiplets. Weil die Kosten des fortgeschrittenen Prozesses sehr hoch sind, werden vor allem die analoge Schaltung und I.O mit der Prozesstechnologie immer schwieriger zu schrumpfen. Chips teilen die Schaltung in unabhängige kleine Chips auf, stärken ihre Funktionen, Verfahrenstechnik und Größe und integrieren sie schließlich zusammen, um die Herausforderung der Prozessminiaturisierung zu meistern. Darüber hinaus können Chiplets auch vorhandene reife Chips nutzen, um Entwicklungs- und Verifizierungskosten zu senken.

Derzeit haben viele Halbleiterhersteller Hochleistungsprodukte in Form von Chips eingeführt. Zum Beispiel ist Intels Intel Stratix 10 GX 10m FPGA mit Chips ausgelegt, um eine höhere Komponentendichte und -kapazität zu erreichen. Basierend auf der bestehenden Intel Stratix 10 FPGA Architektur und Intels fortschrittlicher Embedded Multi Chip Interconnect Bridging (emib) Technologie verwendet das Produkt emib Technologie, um zwei hochdichte Intel Stratix 10 GX FPGA Core Logic Chips und entsprechende I/O Einheiten zu integrieren. Gleiches gilt für AMD Prozessoren der zweiten Generation der epyc Serie. Anders als bei der ersten Generation der Chipmethode, die Speicher und I.O kombiniert, um eine 14-nm-CPU zu bilden, besteht die zweite Generation darin, I.O und Speicher in einen Chip zu trennen und die 7-nm-CPU zur Kombination in 8-Chips zu schneiden.

Mit einem Wort, in der Vergangenheit wurde die Chipeffizienz durch die Verbesserung des Halbleiterprozesses verbessert, aber als sich die Bauteilgröße der physikalischen Grenze näherte, wurde die Chipminiaturisierung immer schwieriger. Um das kleine und hocheffiziente Chipdesign aufrechtzuerhalten, entwickelte die Halbleiterindustrie nicht nur fortschrittliche Prozesse, sondern verbesserte auch die Chiparchitektur, um den Chip aus der ursprünglichen Einzelschicht zu machen. Aus diesem Grund sind fortschrittliche Verpackungen auch zu einem der wichtigsten Treiber für die Verbesserung des Moore-Gesetzes geworden und führen den Trend in der Halbleiterindustrie an.

Die Hauptarbeit des zukünftigen intelligenten Labors umfasst: Einrichtung eines IQ-Bewertungssystems für KI-Intelligenz und Durchführung der weltweiten AI-IQ-Bewertung; Führen Sie den Internet- (Stadt-) Cloud-Hirnforschungsplan durch, bauen Sie die Internet- (Stadt-) Cloud-Hirntechnologie und Unternehmenskarte auf und dienen Sie dazu, das Intelligenzniveau von Unternehmen, Branchen und Städten zu verbessern.