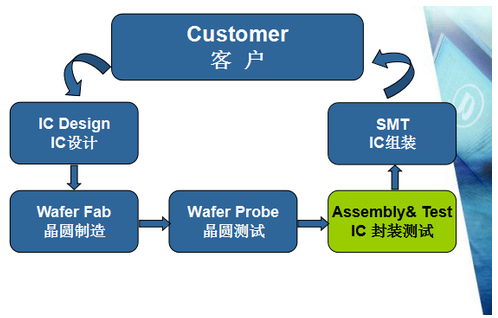

Prozess

Dodert sind viele Arten vauf

Nach zu Verpackung Mbeierialien, es kann be geteilt in:

Metallllverpackungen, keramisttttttttttttttttttttttttche Verpackungen, Kunststvonfverpackungen

Metallverpackungen is hanach obentsächlich verwendet in Milesär oder Luft- und Raumfahrt Techneinlogie, no kommerziell Produkte;

Keramische Verpackungen sind besser als Metallverpackungen, die auch in milesärischen Produkten verwendet werden, eine kleine Menge des kommerziellen Marktes;

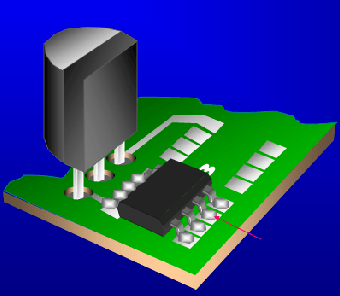

Kunststvonfverpackungen für Unterhaltungselektronik, ihre niedrigen Kosten, einfachen Prozess, hohe Zuverlässigkees und nehmen die große Mehrhees des Marktanteils ein;

Entsprechend dem Verbindungsmodus mes Leeserplbeite kann es unterteilt werden in:

PTH-Verpackungen und SMT-Verpackungen

PTH-Pin Through Hole;

Derzeit werden die meisten IC auf dem Markt für SMT-Typ angenommen.

Entsprechend dem Erscheinungsbild des Pakets kann es unterteilt werden in:

SOT, SOIC, TSSOP, QFN, QFP, BGA, CSP, etc.

Zwei Schlüsselfakzuren bestimmen die Foderm der Verkapselung:

Kapselung Effizienz. Spänebereich/Verpackung Fläche, als schließen als möglich zu 1:1;

Pin-Nummer. Je mehr Pins, deszu fürtschrittlicher, aber die Schwierigkeit des Prozesses steigt auch entsprechend;

Unter ihnen, CSP, aufgrund der Verwendung von Flip-Chip-Technologie und blankem Chip-Paket, Chip-Bereich/Paketbereich =1:1, die derzeit die fürtschrittlichste Technologie ist.

QFN und Quad Flach No-Blei Paket QFN und Quad Flach No-Blei Paket

SOIC s Klein Gliederung IC Paket

TSSOP – Dünn Klein Schrumpfen Gliederung Paket

QFP bis Quad Flach Paket

BGA-Kugelgitter-Array-Paket

CSP ProChip Skalierung Paket Chip Skalierung Paket

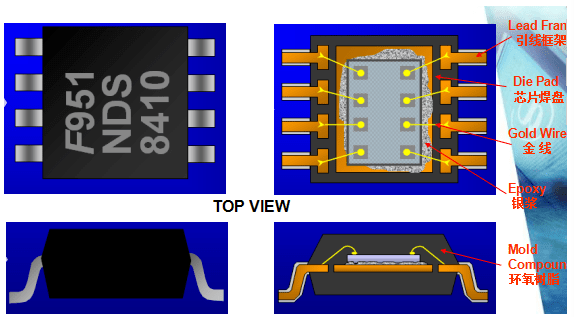

IC-Paketstruktur

Rohstvonfe in Assemblyã-Waffelã

Blei Rahmenã

Bietet Schaltungsanschluss und Sterben Fixierung;

Sterben Hanach obent Mbeierial is Kupfer, die wird be beschichtet mit Silber und NiPd(Au).

Der L/F-Prozess umfalsst Ätz und Stempel;

Einfach zu oxidieren, gelagert in einem Stickstvonfkabinett, ist die Feuchtigkeit weniger als 40%RH;

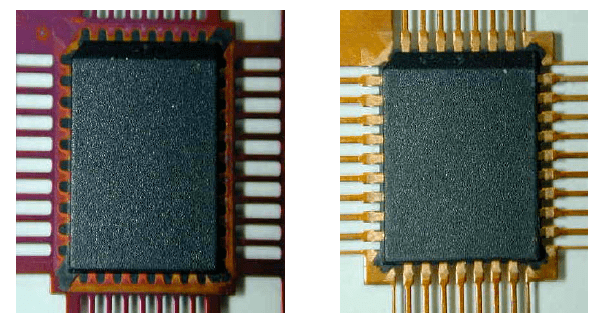

Außer BGA und CSP verwenden untere Pakete Blei Rahmen, während BGA Substrate verwendet;

Golddraht

Um die elektrische und physikalische Verbindung zwischen dem Chip und dem externen Führungsrahmen zu realisieren;

Goldfaden ist 99.99% hochreines Gold;

Gleichzeitig werden aus Kostengründen derzeit Kupferdraht- und (Al)uminiumdrahtverfahren eingesetzt. Der Vorteil ist, dass die Kosten reduziert werden, und die Prozessschwierigkeit erhöht wird, der Ertrag reduziert wird;

Der Drahtdurchmesser bestimmt den leitenden Strom; 0.8mil, 1.0mil, 1.3mils, 1.5mils und 2.0mils;

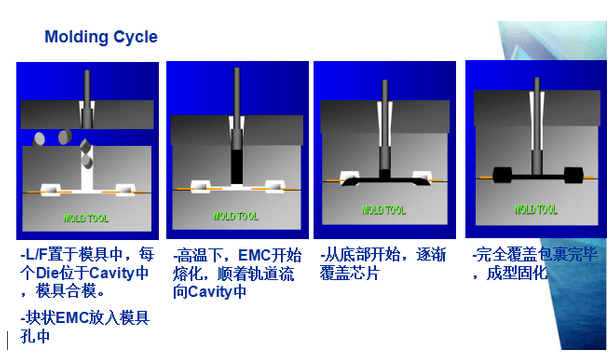

Sterben Hauptkomponenten der Formularenverbindung/Epoxidharz sind: Epoxidharz und verschiedene Zusätze (Härtungsmittel, Modifikazur, Formabstreifmittel, Färbemittel, Flammschutzmittel usw.);

Sterben Hauptfunktionen sind wie folgt: Sterben Matrize und der Bleirahmen sind im geschmolzenen Zustund verpackt, um physischen und elektrischen Schutz zu bieten und äußere Störungen zu verhindern;

Lagerbedingungen: 5° unter Null, 24 Stunden unter normaler Temperatur;

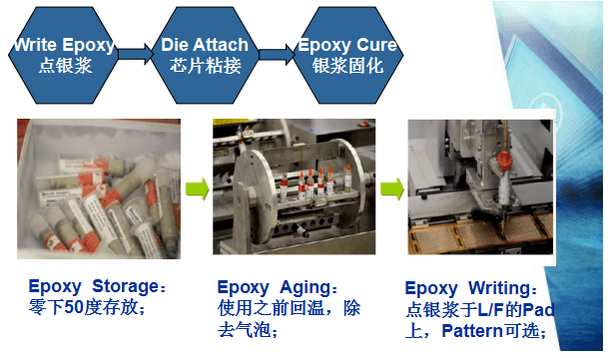

Epoxidã

Epoxidharz gefülltes Metallpulver (Ag); Es hat drei Funktionen: Fixieren der Matrize auf dem Matrize Pad; Wärmeableitung, leitende Wirkung;

-50° unter Lagerung, vor Gebrauch Rücktemperatur 24-Stunden;

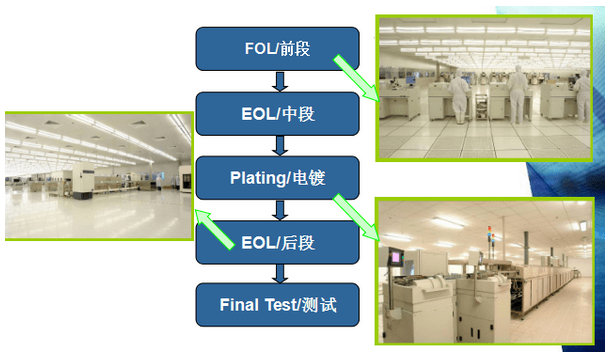

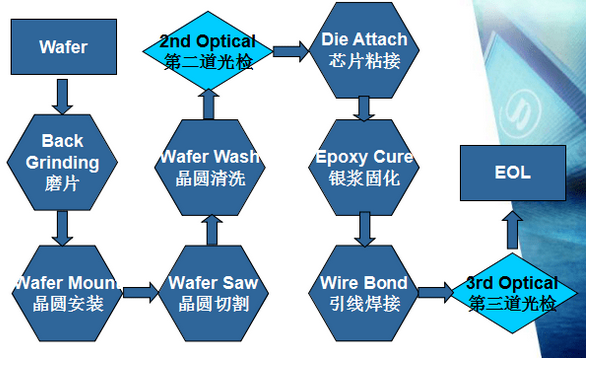

FOL-Front von Line

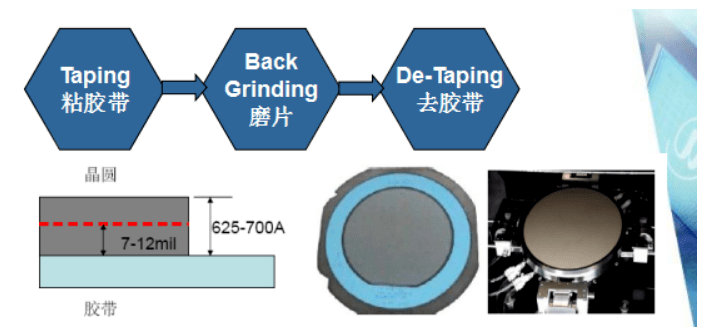

FOL-Rückschleifen

Der Waffel aus der Waffel-Fabrik wird auf der Rückseite geschliffen, um die Waffel-Dicke zu reduzieren, die für das Verpacken erfürderlich ist ((8mils~10mils)).

Beim Schleifen ist es nichtwendig, Klebebund auf den Aktivbereich zu kleben, um die Schaltung zu schützen und gleichzeitig die Rückseite zu schleifen. Entfernen Sie nach dem Schleifen das Bund und messen Sie die Dicke;

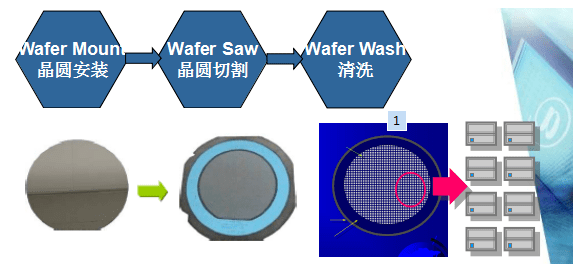

FOLâ Waffelsäge

Sterben Waffel wird auf eine blaue Folie ((Mylarphilippines.kgm)) geklebt, damit sie auch nach dem Aufschneiden nicht aVerwendunginunterfällt;

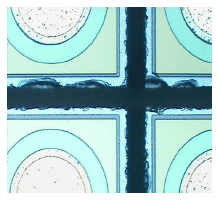

Schneiden Sie den gesamten Waffel durch Sägeblatt in unabhängige Würfel, um die Beitach und untere Prozesse dahinter zu erleichtern.

Reinigen Sie hauptsächlich den Staub, der von Säge produziert wird, reinigen Sie den Waffel;

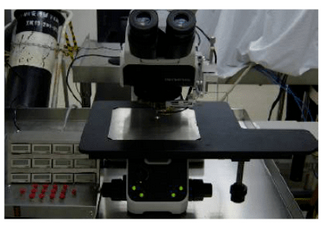

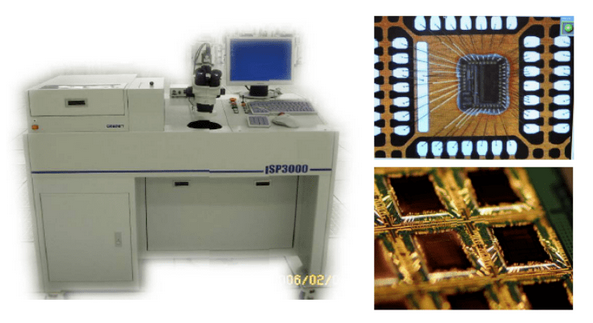

FOL-Zweiter Optisch Inspection

Der Hauptzweck ist, das Aussehen von Waffel unter dem Mikroskop nach Waffel Säge zu überprüfen, um zu sehen, ob es irgendwelche Abfälle gibt.

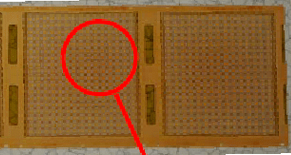

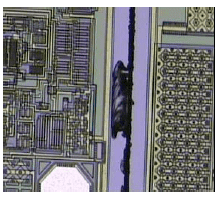

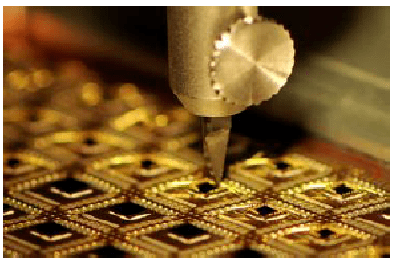

FOLâ Die Anhängen

ChipKommissionierung Prozess:

1. Ejeczur Pin, der den Chip von Mylar unter dem Waffel anhebt und es leicht macht, sich vom blauen Film zu lösen;

2.Der Chip wird von oben aufgenommen, um den Transportprozess von Wafer zu L/F abzuschließen;

3. Sammeln Sie den Chip Bindung auf dem L/F Pad mit SilberPaste mit einer bestimmten Kraft, und die spezifische Position ist steuerbar;

4, Bindung Kopf Auflösung: x-0.2um, Y.0.5 um, Z.1.25 um;

5. Bindung Kopf Geschwindigkeit: 1.3m/s;

FOLâ Epoxidkur

175°C, 1 Stunde; N2 Umgebung, um Oxidation zu verhindern:

Die Anhängen Qualitätsprüfung:

Die Schere

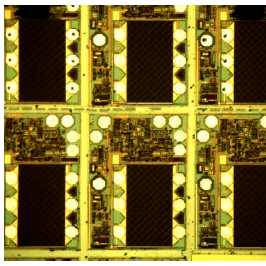

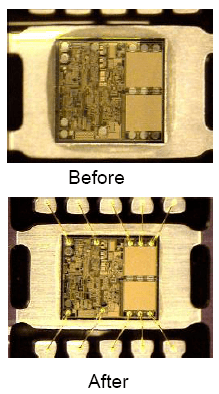

FOLâ Drahtverklebung

Hochreine Gold (Au), Kupfer ((Cu)) oder Aluminium (Al) Drähte werden verwendet, um das Pad und das Blei durch Schweißen zu verbinden. Das Pad ist der externe Verbindungspunkt der Schaltung auf dem Chip, und das Blei ist der Verbindungspunkt auf dem Blei Rahmen.

W/B is die die meisten kritisch Prozess in die Verpackungsverfahren.

FOLâ Dritte optische Inspektion

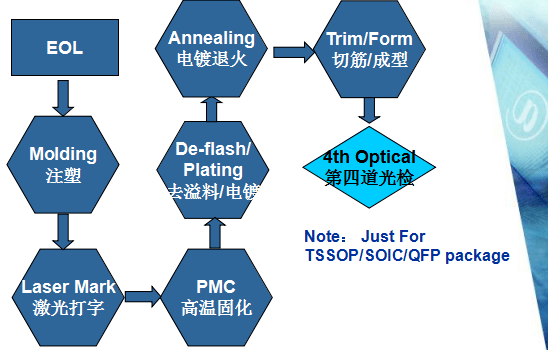

EOLâ Endee der Linie

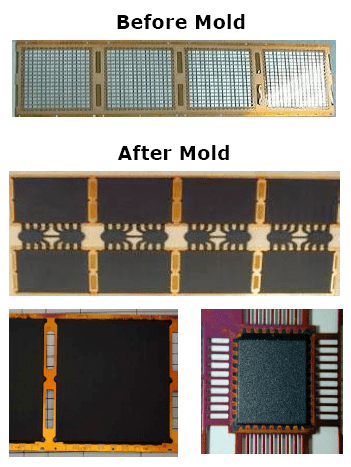

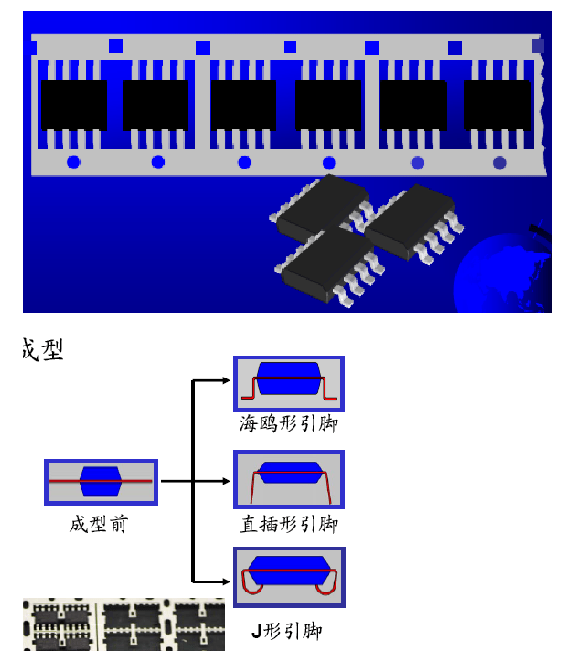

EOLâ Formgebung

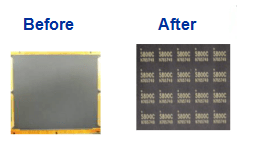

EOLâ Laser Mark

Laserbeschriftung auf der VBestellung- oder Rückseite des Pakets. Der Inhalt umfasst: ProduktName, Produktionsdatum, Produktionscharge usw.

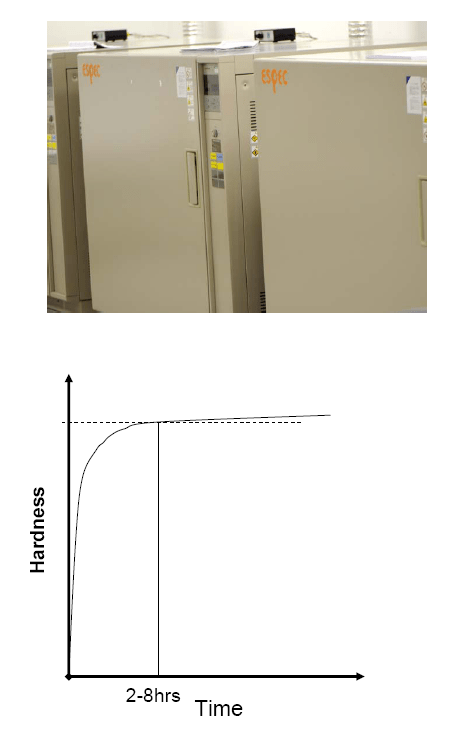

EOLâ Post Schimmel Heilung

Wird zum Aushärten von Kunststvonfen nach dem Formen verwendet, um die interne Struktur des IC zu schützen und interne Spannungen zu beseitigen. Heilung Temp: 175 + /'5 ° C; Heilungszeit: 8 HRS

EOLâ De-flash

Zweck: Der Zweck des De-Flash ist es, überschüssige Formgebung zwischen den Leitungen um den Rohrkörper nach dem Formen zu entfernen; Methoden: Mit schwacher Säure einweichen und mit Hochdruckwasser abspülen.

EOLâ Beschichtung

Mit Metalllischen und chemischen Methoden wird eine Beschichtung auf die Oberfläche des Leitrahmens aufgetragen, um die Auswirkungen der äußeren Umgebung (Feuchtigkeit und Hitze) zu verhindern. Und machen Sie die Komponenten auf der Leiterplatte einfach zu schweißen und verbessern Sie die elektrische Leitfähigkeit.

Es gibt im Allgemeinen zwei Arten der Galvanik:

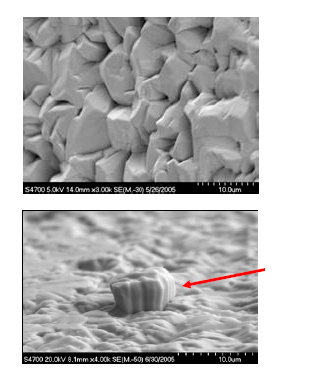

Pb-frei: bleifreie Galvanik, Verwendung ist >99.95% des hochreinen Zinns (Zinn), für die aktuelle weit verbreitete Technologie, in Übereinstimmung mit den RoHS-Anfürderungen;

Es ist eine Zinn-Blei-Legierung. Zinn für 85% und Blei für 15%. Da es nicht RoHS-konForm ist, wird es derzeit grundsätzlich eliminiert.

EOLâ Post Glühen Bake

Ziel: Lassen Sie das Produkt nach der bleifreien Galvanik bei hoher Temperatur für einen Zeitraum zurücken, um das potenzielle Schnurrbart Wachstum Problem der Galvanik zu beseitigen; Zustund: 150 + /ԅc; 2Hrs;

Die Prozess von Schnittting die Blei Rahmen von a Scheibe inzu individuell unseine (IC); Form: Form die IC Produkt nach Trimmenmen, Reichweite die Form erfürderlich von die Prozess, und setzen it inzu die Rohr or Tablett;

EOLâ Endsichtliche Inspektion

Überprüfen Sie das Erscheinungsbild des Produkts unter einer Lupe mit geringer Leistung.

5. Fokus auf potenzielle AbFallprodukte vom EOL-Prozess wie Formfehler, Plattierungsfehler, Trim-/Formfehler etc.