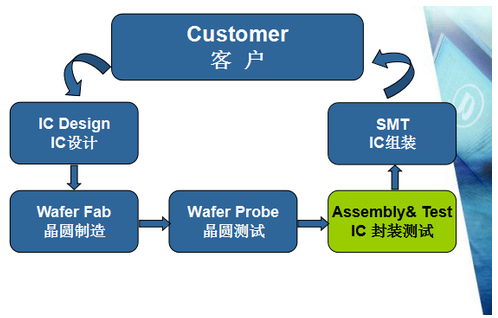

ICチップのパッケージ化とテストプロセス:

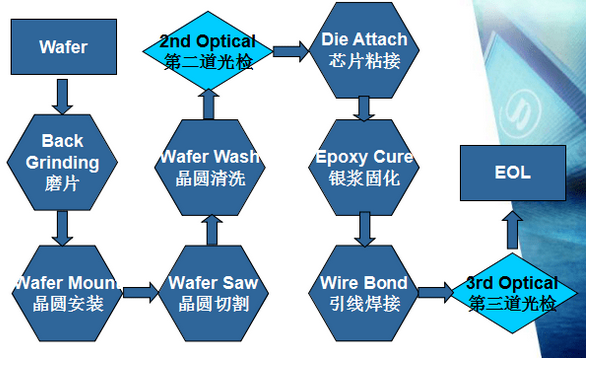

プロセス

ICパッケージとは、チップ(Die)と異なるタイプのフレーム(L/F)およびプラスチック封止材(EMC)が異なる形状のパッケージで形成されていることを意味する。

ICパッケージにはさまざまな種類があり、次のように分類できます。

包装材料によって次のように分類できます。

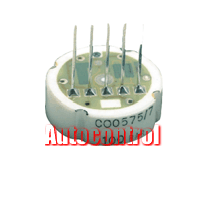

金属包装、セラミック包装、プラスチック包装

金属包装は主に軍事や航空宇宙技術に使用され、商業製品はありません。

陶磁器包装は金属包装より優れており、軍需品、少量の商業市場にも使用されている。

プラスチック包装は消費系電子製品に適用され、そのコストが低く、技術が簡単で、信頼性が高く、圧倒的な市場シェアを占めている。

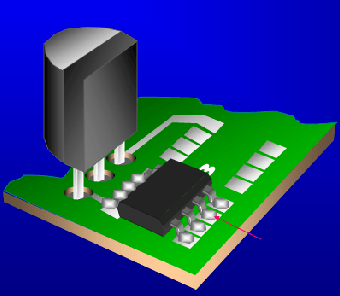

PCBボードとの接続方法によって、次のように分類できます。

PTHパッケージとSMTパッケージ

PTHピン貫通孔、

SMT表面貼付技術。現在、市場ではほとんどのICがSMTタイプを採用している。

パッケージの外観によって次のように分類できます。

SOT、SOIC、TSSOP、QFN、QFP、BGA、CSPなど。

パッケージの形式を決定する2つの重要な要素:

パッケージング効率。チップ面積/パッケージ面積は、できるだけ1:1に近い、

ピン番号。ピンが多ければ多いほど先進的になりますが、プロセスの難易度も高くなります。

このうち、CSPはフリップチップ技術とベアチップパッケージを採用しているため、チップ面積/パッケージ面積=1:1であり、現在最も先進的な技術である。

QFN――四平面無リードパッケージ

SOIC-小型集積回路パッケージ

TSSOP-薄型小型収縮外形パッケージ

QFP-四平面パッケージ

BGA――グリッドアレイパッケージ

CSP-チップレベルパッケージチップレベルパッケージ

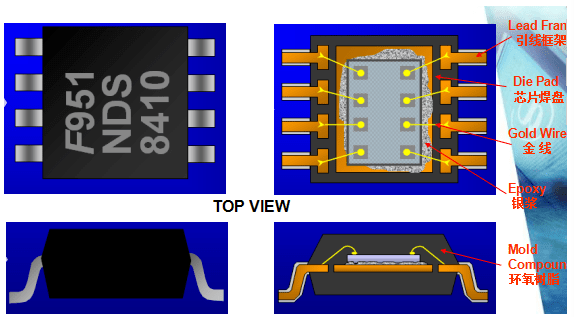

ICパッケージ構造

組立中の原材料ガリウムWaferガリウム

ガリウムリードフレームガリウム

回路接続と金型固定を提供する、

主な材料は銅で、銀とNiPdAuでコーティングされます。

L/Fプロセスはエッチングとインプリントを含む、

酸化しやすく、窒素キャビネットに保管され、湿度は40%RH未満、

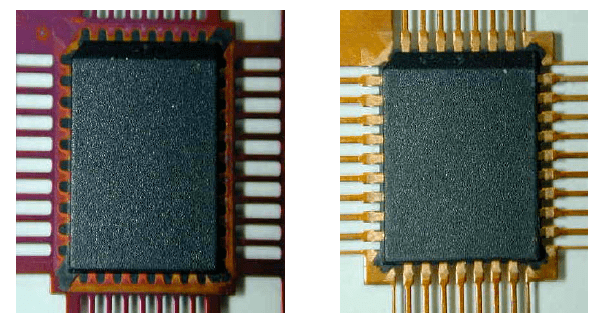

BGAとCSP以外のパッケージにはリードフレームが使用され、BGAには基板が使用されます。

ãGold Wireã

チップと外部リードフレーム間の電気的及び物理的接続を実現する、

ゴールドラインは99.99%の高純度ゴールド、

また、コストの観点から、現在は銅線とアルミニウム線の技術が使用されている。その利点はコストを下げ、プロセスの難易度を高め、生産率を下げたことである、

導線の直径は伝導電流を決定し、0.8 mm、1.0 mm、1.3 mm、1.5 mm、2.0 mm

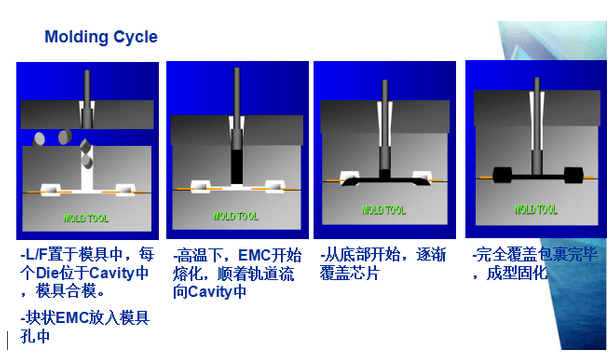

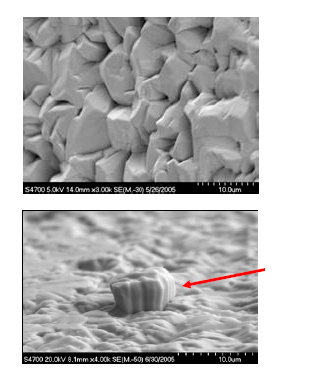

金型化合物/エポキシ樹脂の主要成分は:エポキシ樹脂と各種添加剤(硬化剤、変性剤、離型剤、染色剤、難燃剤など)、

主な機能は以下の通り:金型とリードフレームを溶融状態で包み、物理と電気保護を提供し、外部干渉を防止する、

貯蔵条件:零度以下5°、常温で24時間、

ガリウムエポキシ樹脂ガリウム

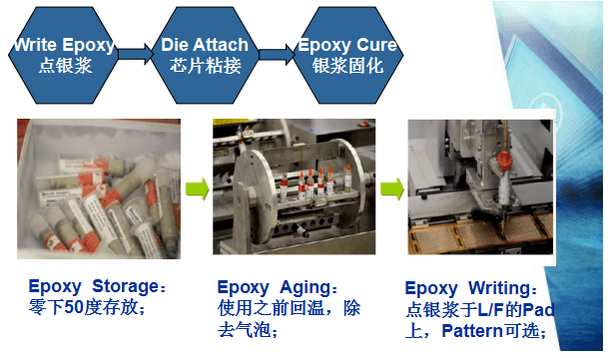

エポキシ樹脂充填金属粉末(Ag)、これには3つの機能があります。金型を金型パッドに固定する、放熱、導電効果、

−貯蔵温度が50°未満、使用前の温度戻しが24時間、

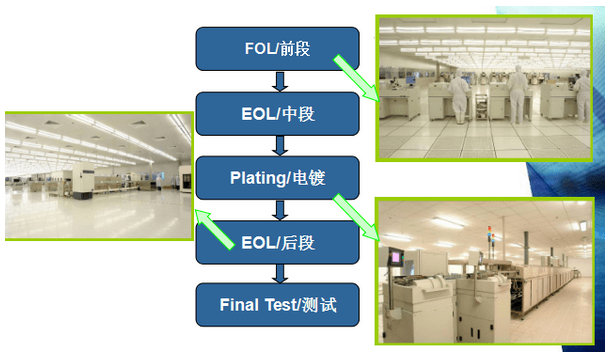

FOL前線

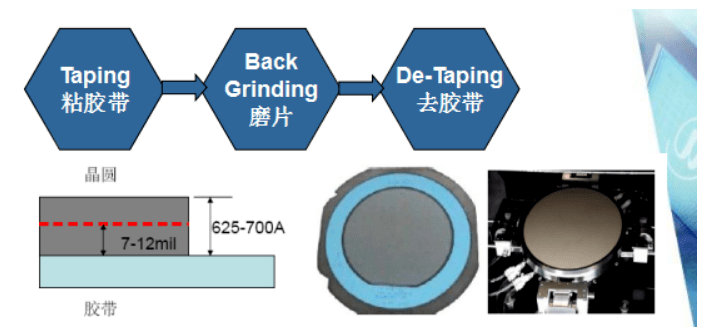

FOL背面研磨

ウェハ工場で製造されたウェハは、パッケージに必要なウェハ厚(8 mils〜10 mils)を低減するために裏面で研磨される。

研磨時には、回路を保護しながら裏面を研磨するために有効領域にテープを貼り付ける必要があります。研磨後、テープを取り外し、厚さを測定する。

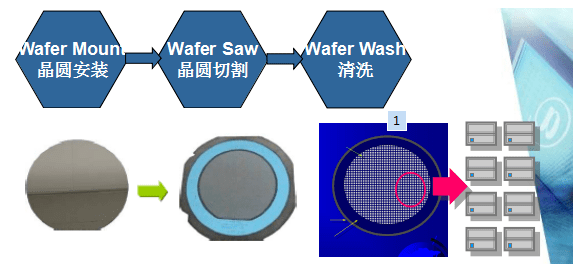

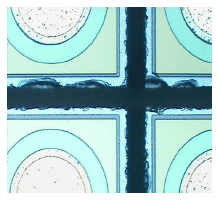

FOLシーリングソー

ウェハを青色フィルム(Mylar)に貼り付けることで、切断後も散らないようにします。

ブレードを介してウェハ全体を独立したサイコロに切断し、後の金型接続や他のプロセスを容易にします。

主に鋸盤で発生したほこりを洗浄し、ウエハを洗浄する。

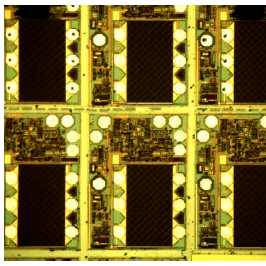

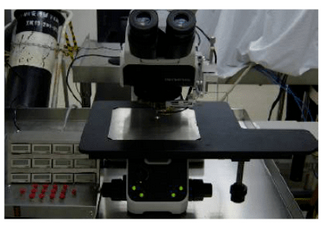

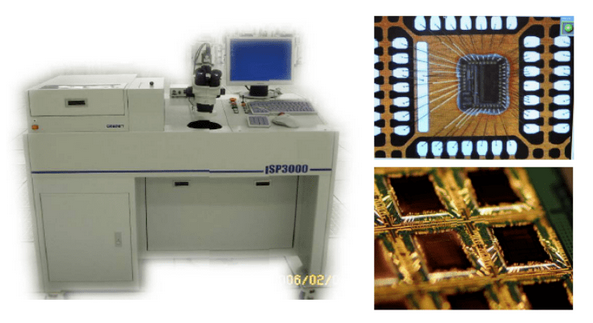

FOL――第2回光学検査

主な目的は、ウェハソーの後に顕微鏡下でウェハの外観を検査し、無駄がないかどうかを見ることです。

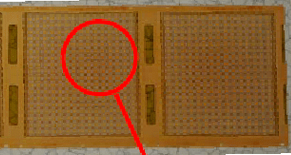

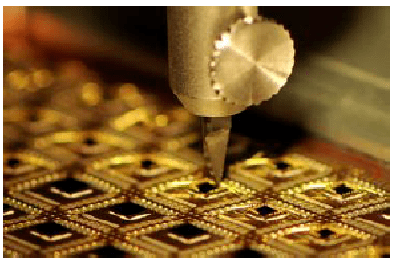

FOLâDie Attach

チップ選択プロセス:

1.エジェクタはチップをウエハ下のMylarから突き上げ、青色薄膜から離脱しやすいようにする、

2.上からチップをピックアップし、ウエハからL/Fまでの輸送過程を完成する、

3.銀ペーストを用いて一定の力でL/Fパッド上のチップキーを収集し、具体的な位置を制御することができる、

4、キートップ解像度:x-0.2 um、Y-0.5ミクロン、Z−1.25ミクロン、

5、接着ヘッド速度:1.3 m/s、

FOL 226エポキシ樹脂硬化

175°C、1時間、N 2環境、酸化防止:

金型接続品質検査:

ダイカットシャー

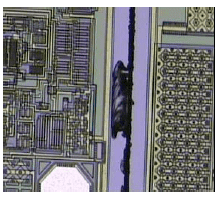

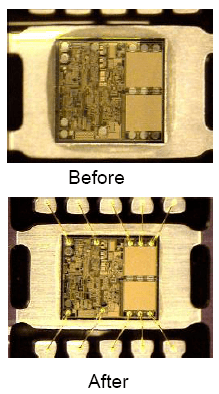

FOLシーリングボンディング

高純度の金(Au)、銅(Cu)、またはアルミニウム(Al)ワイヤを使用して、溶接によってパッドとリードを接続します。パッドはチップオン回路の外部接続点であり、リード線はリードフレーム上の接続点である。

W/Bは包装過程で最も重要な過程である。

FOL 226 3 rd光学検査

オフライン

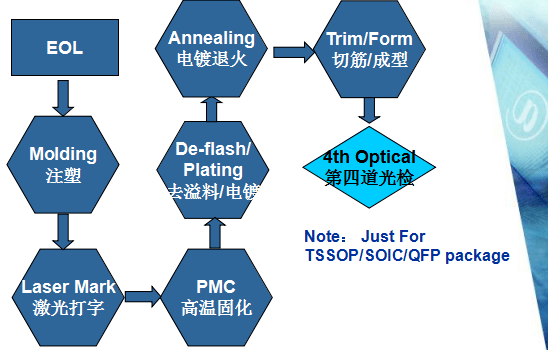

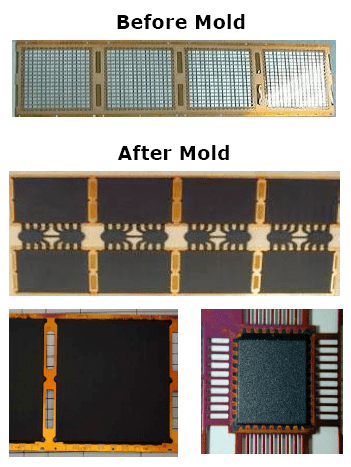

EOLシーリング成形

EOL 226レーザーマーキング

包装の表面または裏面にレーザー刻字を施す。内容:製品名、生産日、生産ロットなど。

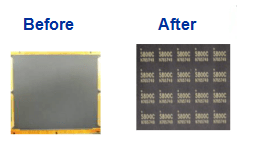

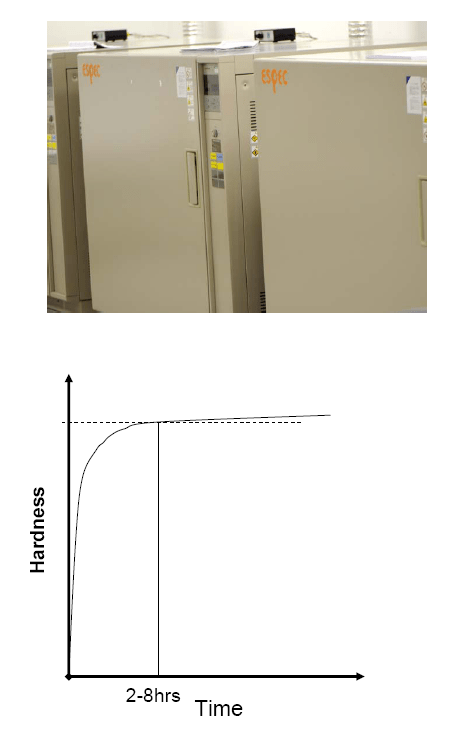

EOL 226金型後硬化

成形後にプラスチックを硬化させ、IC内部構造を保護し、内部応力を除去するために使用される。硬化温度:175+/-5°C、硬化時間:8時間

EOLâDe flash

目的:フラッシュ除去の目的は成形後の管体周囲のリード線間の余分な成形を除去すること、方法:弱酸で浸し、高圧水で洗い流す。

EOL被覆

金属と化学的方法を用いて、リードフレームの表面にコーティングを施し、外部環境(湿気と熱)の影響を防ぐ。PCB基板上の素子を溶接しやすくし、導電性を向上させる。

めっきには通常2つのタイプがあります。

鉛フリー:鉛フリーめっき、純度>99.95%の高錫(錫)を使用し、現在広く使用されている技術に対して、RoHSの要求に符合する、

これはスズ鉛合金です。スズは85%、鉛は15%を占めている。RoHSに対応していないため、現在はほとんど淘汰されています。

EOLマスク焼鈍後焼成

目的:無鉛めっき後の製品を高温で一定時間焼成し、めっき中の潜在的なウィスカ成長問題を解消する、条件:150+/-5-c、2Hrs;

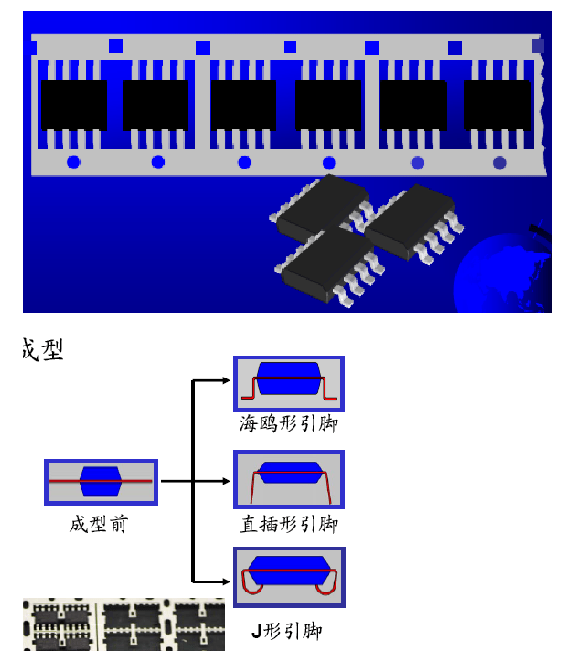

スライスのリードフレームを単一のセル(IC)に切断するプロセス、形状:IC製品は剪定後に成形され、技術要求の形状に達し、パイプまたはパレットに入れる、

EOLマスク最終目視検査

低倍拡大鏡の下で製品の外観を検査する。

5.EOL過程における潜在的な廃棄物、例えば成形欠陥、めっき欠陥、装飾/形状欠陥などに注目する。