La technique consistant à découper des cellules individuelles sur une plaquette, puis à les encapsuler, est la norme depuis des décennies pour l'encapsulation de circuits intégrés semi - conducteurs. Cependant, cette approche n'est pas encore adoptée par les principaux fabricants de semi - conducteurs en raison des coûts de fabrication élevés et de l'augmentation constante des composants RF des modules actuels. Ainsi, l'émergence de l'encapsulation au niveau de la plaquette (WLP) a conduit à un changement de paradigme dans le développement de l'encapsulation à faible coût. WLP est une technologie d'encapsulation au niveau de la plaquette avant la découpe du dispositif d'encapsulation de la plaquette.

Utilisant des outils et des processus standard, WLP agit comme une extension du processus de fabrication de plaquettes. Finalement, le WLP die fabriqué aura des plots métallisés à la surface de la puce et des plots seront déposés sur chaque Plot avant la découpe de la plaquette. Ceci, à son tour, rend le WLP compatible avec les processus traditionnels d'assemblage de PCB et permet des tests de dispositifs sur la plaquette elle - même. Il s'agit donc d'un procédé relativement peu coûteux et efficace, en particulier lorsque la taille de la plaquette augmente et que la puce die se contracte. La taille des plaquettes a augmenté au cours des dernières décennies, passant de 4, 6 et 8 pouces de diamètre à 12 pouces. Il en résulte une augmentation du nombre de Die par plaquette, ce qui réduit les coûts de fabrication. En termes de Performances électriques, le WLP est supérieur aux autres technologies d'encapsulation, car une fois le dispositif WLP intégré dans un module RF dense, il réduit considérablement le couplage parasite EM, car l'interconnexion entre le dispositif et le PCB est relativement courte, contrairement aux interconnexions par liaison filaire utilisées dans certains types de technologies CSP.

Technologie de puce inversée WLP Chip

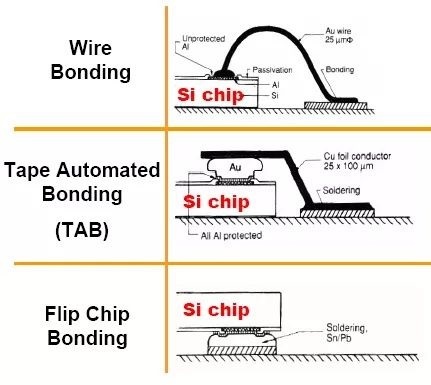

La technologie Flip - chip, également connue sous le nom de Controlled folding Chip Connection (C4), est l'une des nombreuses technologies d'assemblage de puces développées par IBM dans les années 1960. Bien que la technologie d'encapsulation basée sur le câblage soit plus souple en termes de capacité d'induction libre pour la mise en service en laboratoire après construction matérielle et offre également une bonne conductivité thermique, l'utilisation de bourrelets de soudure dans la technologie d'encapsulation Flip - chip permet une réduction relative des dimensions, une réduction du retard des connexions électriques entre le substrat d'encapsulation et la puce, Et une meilleure isolation en termes de broches d'entrée et de sortie. La figure 1 montre la structure de base de la puce die sur un substrat avec une bille de soudure au Sommet d'une colonne de cu qui croît à la surface de la puce. Les points de soudure sont généralement encapsulés avec un composé de moule de remplissage qui fournit un support mécanique aux points de soudure.

Paquet de niveau de puce WLP

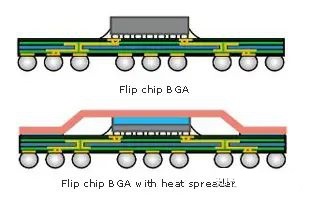

L'Encapsulation au niveau de la puce (CSP) est l'une des méthodes d'encapsulation les plus couramment utilisées dans les industries de la microélectronique et des semi - conducteurs. Alors que plusieurs types de technologies CSP sont déjà disponibles pour les fabricants de micropuces, de nouveaux types de CSP continuent d'émerger pour répondre à la demande de produits qui prennent en charge de nouvelles fonctionnalités et de nouveaux produits spécifiques à l'application. Ces exigences d'encapsulation peuvent varier en fonction de la fiabilité requise, du coût, des fonctionnalités supplémentaires et de la taille globale. Comme son nom l'indique, le CSP a à peu près la même taille de boîtier que la puce die, ce qui est l'un de ses principaux avantages. En adoptant le processus de fabrication WLP, CSP est en constante évolution pour atteindre le plus petit rapport dimensionnel possible des noyaux encapsulés. Comme le montre la figure 2, un CSP de type BGA (Ball Grid Array) dans un boîtier permet de multiples interconnexions tout en simplifiant le câblage du PCB, en augmentant le débit d'assemblage du PCB et en réduisant les coûts de fabrication.

Autres techniques d'encapsulation

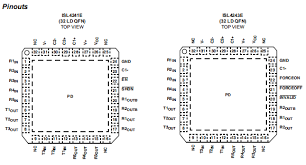

Il existe plusieurs autres formes de Packaging IC intégré qui permettent une intégration transparente dans des packages de modules personnalisés pour les applications. Le Quad plane Packaging (qfp) est l'une des premières technologies d'encapsulation IC à montage en surface, dans laquelle la structure de l'encapsulation se compose de quatre côtés avec des cordons d'interconnexion étendus, comme le montre la figure 3 (A). Les fils surélevés sont connectés au cadre d'encapsulation pour former entre les fils et le métal die de la puce un condensateur de type métal - isolant - métal (MIM) utilisable comme élément d'adaptation. Cette technologie est adaptée aux IC de taille millimétrique, où le nombre de broches périphériques dans le boîtier peut atteindre plus de 100. Selon le matériau utilisé, il existe plusieurs dérivés de ce type d'encapsulation, tels que l'encapsulation quadruple en céramique, l'encapsulation quadruple mince, l'encapsulation quadruple en plastique (Plastic quadruple flat pack) et l'encapsulation quadruple métallique (mqfp). Qfn, Quad flat no Lead, illustré sur la photo. 3 (b) est l'une des nombreuses technologies d'encapsulation à montage en surface, formée d'un cadre plat en cuivre et d'un boîtier en plastique utilisé comme tapis de transfert de chaleur pour radiateur. Les jonctions de fils peuvent également être utilisées pour l'interconnexion, et comme les lignes de jonction ne sont pas seulement des conducteurs, mais aussi des inductances, elles affectent généralement les performances des dispositifs dans cette technologie d'encapsulation, à moins qu'elles ne soient considérées comme faisant partie de la conception globale. Bien qu'un qfn soit une interconnexion composée de quatre côtés, un fil double plan sans plomb (DFN) est également apparu et forme les deux côtés d'un fil plat d'interconnexion.