En plus des processus avancés, l'encapsulation avancée est devenue une technologie clé dans la poursuite de la loi de Moore. Ces dernières années, des technologies telles que la 2.5D, la 3D et les puces sont devenues un sujet brûlant dans l'industrie des semi - conducteurs. Comment l'encapsulation avancée joue - t - elle exactement un rôle clé dans la continuation de la loi de Moore? 2. Quelles sont les caractéristiques des technologies d'encapsulation telles que 5d, 3D et chiplets?

Des applications telles que l'intelligence artificielle, l'Internet des véhicules, la 5G et d'autres ont émergé et nécessitent toutes l'utilisation de puces fonctionnelles avancées pour l'informatique à grande vitesse, la transmission à grande vitesse, la faible latence et la faible consommation d'énergie. Cependant, à mesure que la demande en informatique se multiplie, comment perpétuer la loi de Moore est un défi pour l'industrie des semi - conducteurs.

Avec la difficulté croissante de miniaturiser les puces, des intégrations hétérogènes sont apparues.

En d'autres termes, les processus avancés de semi - conducteurs évoluent vers 7nm, 5NM, puis 3nm et 2nm. La taille du transistor se rapproche donc de la limite de volume physique de l'atome. Les contraintes électroniques et physiques rendent également de plus en plus difficile la poursuite de la réduction et de la mise à niveau des processus avancés.

Ainsi, en plus de continuer à développer des processus avancés, l'industrie des semi - conducteurs cherche également d'autres moyens de garder les puces miniaturisées et efficaces. La conception de la disposition de la puce est devenue une nouvelle solution pour perpétuer la loi de Moore, et le concept de système d'architecture de conception intégrée hétérogène (Hidas) est né, devenant le moteur de l'innovation pour les puces de circuits intégrés.

L'intégration dite hétérogène, au sens large, est l'intégration de deux puces différentes, telles que la mémoire + puce logique, optoélectronique + composants électroniques, par l'encapsulation, l'empilement 3D et d'autres technologies. En d'autres termes, l'intégration de deux puces de processus différents et de performances différentes peut être qualifiée d'intégration hétérogène.

Parce que le marché des applications est plus diversifié, chaque produit est différent en termes de coût, de performance et de population cible, de sorte que les technologies d'intégration hétérogènes requises sont également différentes et que la tendance à la focalisation sur le marché se manifeste progressivement. Par conséquent, le générateur IC, la fabrication et l'industrie des équipements semi - conducteurs ont tous investi dans le développement de l'intégration hétérogène, 2.5D, l'encapsulation 3D, chiplets et d'autres technologies d'encapsulation populaires, toutes basées sur la philosophie de l'intégration hétérogène, telles que Chun yihong puis Spring Bud.

L'emballage 2.5D réduit efficacement les coûts de production de puces

Dans le passé, pour intégrer des puces ensemble, la plupart du temps, les technologies SIP (système en boîtier) étaient utilisées, telles que Pip (encapsulation dans un boîtier), POP (encapsulation sur un boîtier). Cependant, en tant que smartphone, aiot et autres applications, non seulement des performances plus élevées sont nécessaires, mais aussi pour maintenir une petite taille, une faible consommation d'énergie, dans ce cas, nous devons trouver un moyen d'empiler plus de puces pour réduire le volume, de sorte que la technologie d'encapsulation actuelle, en plus du SIP original, évolue également vers la technologie d'encapsulation 3D.

En bref, l'encapsulation tridimensionnelle implique l'utilisation d'un intermédiaire en silicium (Silicon Intermediate) directement à partir d'une tranche de silicium, plutôt que d'utiliser l'ancien « porte - fil» en plastique et d'encapsuler plusieurs puces avec des fonctions différentes directement dans une puce plus efficace. En d'autres termes, l'ajout d'une tranche de silicium sur le silicium augmente les coûts et les contraintes physiques du procédé, ce qui permet à la loi de Moore de rester efficace.

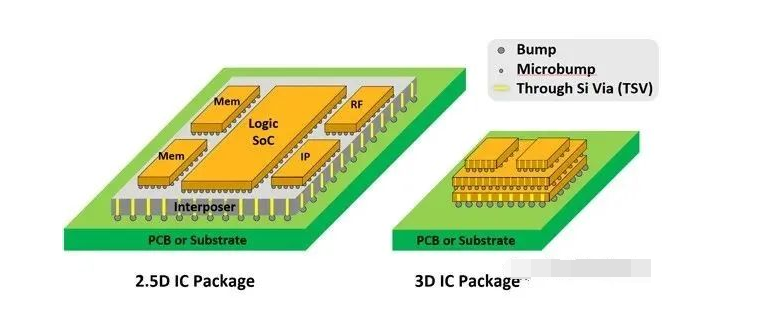

L'Encapsulation stéréoscopique est plus familière avec l'encapsulation 2.5D et 3D, ici nous commençons par l'encapsulation 2.5D. Le concept principal, appelé boîtier 2.5D, consiste à disposer un processeur, une mémoire ou d'autres puces sur un interpolateur en silicium (Silicon interposer), connecté par des micro - bosses, permettant aux fils métalliques interpolés en silicium de connecter les signaux électroniques de différentes puces. Le TSV est alors utilisé pour connecter les Plots métalliques inférieurs et la plaque porte - fil est utilisée pour connecter les billes métalliques externes afin de réaliser une interconnexion plus étroite entre la puce, la puce et le substrat d'encapsulation.

L'Encapsulation 2.5D et 3D est la technologie d'encapsulation stéréoscopique populaire de nos jours. (Source: ANSYS)

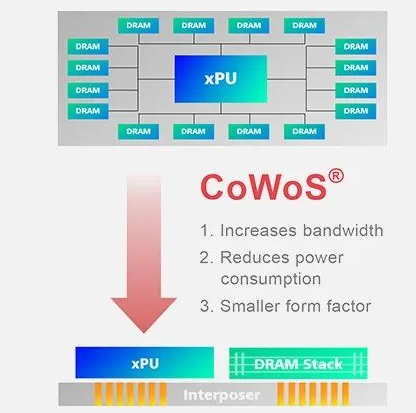

La technologie d'encapsulation 2.5D actuellement bien connue n'est autre que le cowos de TSMC. Le concept de la technologie cowos est de placer des puces semi - conductrices telles que des processeurs, des mémoires, etc. sur une couche intermédiaire de silicium, puis de les connecter au substrat inférieur par un processus d'encapsulation de puces sur puce (Cow). En d'autres termes, la puce est d'abord connectée à la plaquette de silicium par un procédé d'encapsulation de la puce sur plaquette (Cow), puis la puce cow est connectée au substrat et intégrée dans cowos. Avec ce mode d'encapsulation, il est possible d'encapsuler plusieurs puces ensemble et de les interconnecter via un interpolateur en silicium, ce qui permet d'obtenir un faible volume d'encapsulation, une faible consommation d'énergie et moins de broches.

Concept de technologie d'encapsulation de TSMC. (Source: TSMC)

En plus de cowos, l'encapsulation au niveau de la tranche de sortie peut également être classée comme une méthode d'encapsulation 2.5D. Le principe de l'encapsulation au niveau de la tranche de sortie est de tirer les circuits nécessaires de l'extrémité du semi - conducteur nu vers la couche de redistribution pour former l'encapsulation. Ainsi, il n'est pas nécessaire de sceller les plaques de chargement, les fils, les Plots, ce qui peut réduire les coûts de production de 30% et également rendre la puce plus mince. Dans le même temps, la zone de la puce peut être considérablement réduite. Il peut également remplacer les perforations de silicium plus coûteuses, permettant l'intégration de différents composants par des techniques d'encapsulation.

Bien sûr, la technologie d'encapsulation stéréoscopique n'est pas seulement 2.5D, mais aussi l'encapsulation 3D. Alors, quelle est la différence entre les deux, et l'industrie des semi - conducteurs adopte l'encapsulation 3D?

Par rapport au boîtier 2.5D, le boîtier 3D fonctionne en créant une structure de Transistor (CMOS) sur la puce et en utilisant des perforations de silicium pour connecter les signaux électroniques des différentes puces supérieures et inférieures, de sorte que la mémoire ou d'autres puces peuvent être empilées verticalement directement sur

L'Encapsulation 3D est un empilement direct de puces. (Source: Intel)

TSMC et Intel développent activement la technologie d'encapsulation 3D

Intel (intc) et Taiwan Semiconductor (TSMC) ont leurs propres technologies d'encapsulation 3D. Intel utilise la technologie d'encapsulation 3D "foveros", qui utilise une logique de pile hétérogène pour gérer les opérations et peut empiler chaque puce logique ensemble. Cela signifie que, pour la première fois, l'empilement de puces s'étend des supports de silicium passifs traditionnels et des mémoires empilées à des produits logiques efficaces tels que les processeurs CPU, graphiques et d'IA. Dans le passé, les empilements n'étaient utilisés que pour la mémoire, mais on utilise maintenant des empilements hétérogènes pour réaliser des empilements de différentes combinaisons de mémoires et de puces de calcul.

En outre, Intel développe trois nouvelles technologies: co - emib, ODI et mdio. Co - emib peut connecter des performances et des capacités de calcul supérieures et permettre l'interconnexion de deux ou plusieurs composants foveros. Les concepteurs peuvent également connecter des simulateurs, des mémoires et d'autres modules avec une bande passante très élevée et une très faible consommation d'énergie. La technologie ODI offre une plus grande flexibilité pour une communication interconnectée complète entre les puces de petite et moyenne taille. La puce supérieure peut communiquer avec d'autres puces plus petites, telles que la technologie emib, et elle peut communiquer verticalement avec la puce inférieure nue, telle que la technologie foveros, via un via en silicium (TSV).

Concept technologique Intel foveros. (Source: Intel)

La technologie utilise également de grands trous traversants verticaux pour alimenter la plaque nue supérieure directement à partir du substrat d'encapsulation. Ces grands Vias sont beaucoup plus grands que les Vias traditionnels en silicium et offrent une transmission de puissance plus stable avec une résistance inférieure. Et permet une bande passante plus élevée et une latence plus faible avec la pile. Cette approche réduit le nombre de Vias de silicium nécessaires dans la puce de base, libère plus de surface pour les éléments actifs et optimise les dimensions de la feuille nue.

D’autre part, TSMC propose des solutions d’intégration « 3D Multi - Chip and System Integration Chip » (SOIC). La solution sur puce intégrée au système superpose directement des cristaux nus bien connus de différentes tailles, techniques de traitement et matériaux.

TSMC souligne que les puces intégrées du système ont une densité et une vitesse de billes plusieurs fois plus élevées, tout en réduisant considérablement la consommation d'énergie par rapport aux solutions de circuits intégrés 3D traditionnelles utilisant des microbilles. Par ailleurs, la puce d'intégration de système est une solution intégrée de prétraitement reliant deux ou plusieurs cristaux nus avant Encapsulation; Ainsi, le chipset intégré au système peut intégrer davantage d'autres puces en utilisant les technologies d'encapsulation avancées du back - end info ou cowos de la société, créant ainsi une solution puissante au niveau du système "3D * 3D".

En outre, TSMC a lancé 3dfabric, qui rassemble les solutions d'intégration de systèmes 3dic en pleine croissance pour offrir une plus grande flexibilité et créer des systèmes puissants avec de puissantes interconnexions de puces. Avec différentes options d'empilement de puces avant et arrière, 3dfabric aide les clients à connecter plusieurs puces logiques ensemble, même des petites puces hétérogènes telles que des mémoires haute fréquence (hbM) en série ou des modules analogiques, input / out et RF. 3dfabric combine des solutions 3D à l'arrière et à l'avant et complète les miniatures de transistors pour améliorer continuellement les performances et les fonctionnalités du système, réduire la taille et l'apparence et accélérer le délai de mise sur le marché des produits.

Après le lancement de 2.5D et 3D, chiplets est l'une des dernières technologies d'encapsulation avancées dans l'industrie des semi - conducteurs à impact. Enfin, un bref aperçu des caractéristiques et des avantages des chiplets.

Il y a trois avantages à utiliser chiplets. En raison du coût très élevé des processus avancés, il est de plus en plus difficile de contracter les circuits analogiques et les E / s en particulier avec le développement des technologies de processus. Les puces divisent les circuits en petites puces indépendantes, améliorant leur fonctionnalité, leur technologie de processus et leur taille, les intégrant finalement pour surmonter les défis de la miniaturisation des processus. En outre, chiplets peut également utiliser des puces matures existantes pour réduire les coûts de développement et de validation.

Actuellement, de nombreux fabricants de semi - conducteurs ont lancé des produits haute performance à la manière d'une puce. Par exemple, le FPGA Intel stratix 10 GX 10 mètres d'Intel est conçu avec une puce qui permet une densité et une capacité de composants plus élevées. Le produit est basé sur l'architecture FPGA Intel stratix 10 existante et la technologie emib (Embedded Multi - Chip Interconnection Bridge) d'Intel, qui utilise la technologie emib pour intégrer deux puces logiques de base FPGA Intel stratix 10 GX haute densité et les unités d'E / s correspondantes. Il en va de même pour la deuxième génération de processeurs de la famille epyc d'AMD. Contrairement à la première génération qui combine la mémoire et les E / s pour former un CPU de 14 nm, la deuxième génération sépare les E / s et la mémoire en une seule puce et découpe le CPU de 7 nm en 8 puces pour les combiner.

En conclusion, dans le passé, l'efficacité des puces a été améliorée par l'amélioration des processus de semi - conducteurs, mais la miniaturisation des puces est devenue de plus en plus difficile à mesure que la taille des composants approchait des limites physiques. Afin de maintenir la conception de la puce de petite taille et de haute efficacité, l'industrie des semi - conducteurs continue non seulement à développer des processus avancés, mais a également amélioré l'architecture de la puce pour que la puce passe de la couche unique d'origine à l'empilement multicouche. Par conséquent, l'emballage avancé est également devenu l'un des principaux moteurs de l'amélioration de la loi de Moore, ouvrant la voie à l'industrie des semi - conducteurs.

Les principaux travaux du future intelligence Lab comprennent: la mise en place d’un système d’évaluation du Qi des systèmes d’ia, la réalisation d’une évaluation mondiale du Qi en IA; Mener des programmes de recherche sur le cerveau en nuage Internet (urbain) pour construire des cartes de la technologie du cerveau en nuage Internet (urbain) et des entreprises avec des services qui améliorent le niveau d'intelligence dans les entreprises, les industries et les villes.