Before designing a multi-layer PCB, the PCB designer needs to first determine the circuit board structure used according to the circuit scale, circuit board size and electromagnetic compatibility (EMC) requirements, that is, to decide whether to use 4 layers, 6 layers, or more Multi-layer circuit board. After determining the number of layers, determine where to place the internal electrical layers and how to distribute different signals on these layers. This is the choice of multilayer PCB stack structure. The laminated structure is an important factor that affects the EMC performance of the PCB board, and it is also an important means to suppress electromagnetic interference. This section will introduce the relevant content of the multilayer PCB stack structure. After determining the number of power, ground and signal layers, the relative arrangement of them is a topic that every PCB engineer cannot avoid.

1. General principles for the arrangement of circuit board layers:

1. To determine the laminated structure of the multilayer PCB board, many factors need to be considered. From the perspective of wiring, the more layers, the better the wiring, but the cost and difficulty of board manufacturing will also increase. For manufacturers, whether the laminated structure is symmetrical or not is the focus that needs to be paid attention to when PCB boards are manufactured, so the choice of the number of layers needs to consider the needs of all aspects to achieve the best balance.

2. The bottom of the component surface (the second layer) is the ground plane, which provides the device shielding layer and the reference plane for the top wiring; the sensitive signal layer should be adjacent to an internal electrical layer (internal power/ground layer), using the large internal electrical layer Copper film to provide shielding for the signal layer. The high-speed signal transmission layer in the circuit should be a signal intermediate layer and sandwiched between two inner electrical layers. In this way, the copper film of the two inner electric layers can provide electromagnetic shielding for high-speed signal transmission, and at the same time, it can effectively limit the radiation of the high-speed signal between the two inner electric layers without causing external interference.

3. All signal layers are as close as possible to the ground plane.

4. Try to avoid two signal layers directly adjacent to each other; it is easy to introduce crosstalk between adjacent signal layers, resulting in circuit function failure. Adding a ground plane between the two signal layers can effectively avoid crosstalk.

5. The main power supply is as close as possible to it.

6. Take into account the symmetry of the laminated structure.

2. Stacking structure commonly used in PCB design:

4-layer board

The following uses an example of a 4-layer board to illustrate how to optimize the arrangement and combination of various laminated structures.

For commonly used 4-layer boards, there are several stacking methods (from top to bottom):

(1) Siganl_1 (Top), GND (Inner_1), POWER (Inner_2), Siganl_2 (Bottom).

(2) Siganl_1 (Top), POWER (Inner_1), GND (Inner_2), Siganl_2 (Bottom).

(3) POWER (Top), Siganl_1 (Inner_1), GND (Inner_2), Siganl_2 (Bottom).

Obviously, Scheme 3 lacks effective coupling between the power layer and the ground layer and should not be adopted.

So how should option 1 and option 2 be selected? Under normal circumstances, designers will choose option 1 as the structure of the 4-layer board. The reason for the choice is not that Option 2 cannot be adopted, but that the general PCB board only places components on the top layer, so it is more appropriate to adopt Option 1. However, when components need to be placed on both the top and bottom layers, and the dielectric thickness between the internal power layer and the ground layer is large and the coupling is poor, it is necessary to consider which layer has fewer signal lines. For Option 1, there are fewer signal lines on the bottom layer, and a large-area copper film can be used to couple with the POWER layer; on the contrary, if the components are mainly arranged on the bottom layer, Option 2 should be used to make the board.

6-layer board

After completing the analysis of the stacked structure of the 4-layer board, the following uses an example of the combination of the 6-layer board to illustrate the arrangement and combination of the 6-layer board and the preferred method. (1) Siganl_1 (Top), GND (Inner_1), Siganl_2 (Inner_2), Siganl_3 (Inner_3), POWER (Inner_4), Siganl_4 (Bottom). Solution 1 uses 4 signal layers and 2 internal power/ground layers. It has more signal layers, which is conducive to the wiring work between components. However, the defects of this solution are also more obvious, which are manifested in the following two aspects.

1. The power layer and the ground layer are separated far away and not sufficiently coupled.

2. The signal layer Siganl_2 (Inner_2) and Siganl_3 (Inner_3) are directly adjacent, so the signal isolation is not good and crosstalk is easy to occur. (2) Siganl_1 (Top), Siganl_2 (Inner_1), POWER (Inner_2), GND (Inner_3), Siganl_3 (Inner_4), Siganl_4 (Bottom).

Compared with the scheme 1, the power layer and the ground layer are fully coupled in the scheme 2, which has certain advantages compared with scheme 1. However, the signal layer of Siganl_1 (Top) and Siganl_2 (Inner_1) and Siganl_3 (Inner_4) and Siganl_4 (Bottom) are directly connected. Adjacent, the signal isolation is not good, the problem of prone to crosstalk has not been solved.

(3) Siganl_1 (Top), GND (Inner_1), Siganl_2 (Inner_2), POWER (Inner_3), GND (Inner_4), Siganl_3 (Bottom).

Compared with scheme 1 and scheme 2, scheme 3 has one less signal layer and one more internal electrical layer. Although the layer available for wiring is reduced, this scheme solves the common defects of scheme 1 and scheme 2.

1. The power plane and ground plane are tightly coupled.

2. Each signal layer is directly adjacent to the inner electric layer, and is effectively isolated from other signal layers, and crosstalk is not easy to occur.

3. Siganl_2 (Inner_2) is adjacent to the two inner electrical layers GND (Inner_1) and POWER (Inner_3), which can be used to transmit high-speed signals. The two internal electrical layers can effectively shield the interference from the outside world to the Siganl_2 (Inner_2) layer and the interference from Siganl_2 (Inner_2) to the outside world.

Comprehensively speaking, scheme 3 is obviously the most optimized one. At the same time, scheme 3 is also a commonly used laminated structure for 6-layer boards.

10-layer board

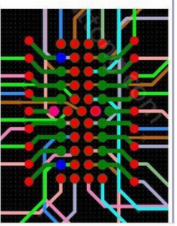

PCB typical 10-layer board design

The general wiring sequence is TOP--GND---signal layer---power layer---GND---signal layer---power layer---signal layer---GND---BOTTOM

The wiring sequence itself is not necessarily fixed, but there are some standards and principles to restrict it: For example, the adjacent layers of the top layer and bottom layer use GND to ensure the EMC characteristics of the single board; for example, each signal layer preferably uses the GND layer as a reference Plane; the power supply used in the entire single board is preferentially laid on a whole piece of copper; the susceptible, high-speed, and preferred to go along the inner layer along the jump, and so on.

Three, PCB design laminated structure improvement case

question

The product has 8 groups of network ports and optical ports. During the test, it was found that the signal debugging between the eighth group of optical ports and the chip failed, which resulted in the failure of optical port 8 to debug and could not work, and the other 7 groups of optical ports communicate normally.

1. Confirm the problem

According to the information provided by the client, it is confirmed that the two differential impedance lines between the L6 layer optical port 8 and the chip 8 cannot be debugged;

According to the information provided by the client, it is confirmed that the two differential impedance lines between the optical port 8 and the chip 8 on the L6 layer cannot be debugged

2. Stacking and design requirements provided by customers

Improve effect

By adjusting the PCB stack structure to increase the distance between the adjacent signal layers of the L56 layer, the system failure problem caused by crosstalk is solved.