The design of LVDS signal on the PCB board is not only a differential signal, but also a high-speed digital signal. Therefore, regardless of whether the LVDS transmission medium uses PCB board wires or cables, measures must be taken to prevent the signal from being reflected at the media terminal, and electromagnetic interference should be reduced to ensure signal integrity. As long as we consider these elements when wiring, designing high-speed differential circuit boards is not very difficult. The following briefly introduces the design points of the LVDS signal on the PCB board: 2.1 Layout into a multilayer board Circuit boards with LVDS signals are generally laid out as a multilayer board. Since the LVDS signal is a high-speed signal, the adjacent layer should be a ground layer to shield the LVDS signal to prevent interference. For boards with a low density, if physical space conditions permit, place LVDS signals and other signals on different layers. For example, in a four-layer board, the layers can usually be laid out as follows: LVDS signal layer, ground layer, power layer, and other signal layers. 2.2 LVDS signal impedance calculation and control. The voltage swing of the LVDS signal is only 350mV, which is suitable for current-driven differential signal operation. In order to ensure that the signal is not affected by the reflected signal when it propagates in the transmission line, the LVDS signal requires the transmission line impedance to be controlled, and the differential impedance is usually 100 +/- 10Ω. The quality of impedance control directly affects signal integrity and delay.

1. How to control its PCB board impedance?

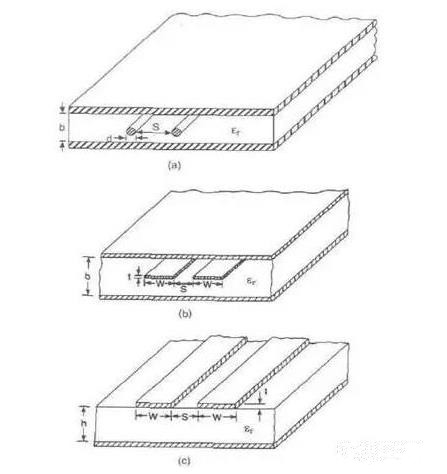

1.1 Determine the wiring mode, parameters and impedance calculation. LVDS is divided into outer layer microstrip line differential mode and inner layer strip line differential mode. Impedance can be calculated by setting the parameters reasonably and using related software. Through calculation, the impedance value is directly proportional to the thickness of the insulating layer, and inversely proportional to the dielectric constant, the thickness and width of the wire.

1.2 Follow the principle of parallel equidistant lines and tight coupling. After determining the line width and spacing, strictly follow the calculated line width and spacing when routing, and the spacing between the two lines must always be kept constant, that is, they must be parallel (you can place the picture). At the same time, the tight coupling principle is observed when calculating the line width and spacing, that is, the line spacing of the differential pair is less than or equal to the line width. When the two differential signal lines are very close, the current transmission direction is opposite, the magnetic fields cancel each other, the electric fields are coupled with each other, and the electromagnetic radiation is much smaller. Also, the two wires must be on the same layer to avoid layered wiring. Because in the actual processing of the PCB board, the degree of lamination between the stacks is much lower than the etching accuracy of the same layer, and the dielectric loss during the lamination process cannot guarantee that the distance between the differential lines is equal to the thickness of the interlayer dielectric, which will cause The differential impedance change of the differential pair between layers.

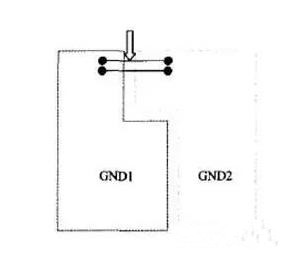

1.3 Go short and straight. In order to ensure the quality of the signal, the LVDS differential pair trace should be as short and straight as possible, reduce the number of vias in the wiring, and avoid too long differential pair wiring and too many turns. Try to use 45° or arcs at the corners. Avoid 90° turns. There is no restriction on the selection of LVDS pair routing methods between different differential line pairs. Microstrip line and strip line can be used, but it must be noted that there is a good reference plane. The spacing between different differential lines should not be too small, and should be at least 3-5 times the spacing between differential lines. If necessary, add ground hole isolation between different differential line pairs to prevent mutual crosstalk. Keep LVDS signals away from other signals as much as possible. LVDS differential signals cannot be divided across planes. Although the two differential signals are return paths for each other, the cross-segmentation will not cut off the return of the signal, but the transmission line across the segmentation will cause discontinuity in impedance due to the lack of a reference plane (as shown in the figure, where GND1 and GND2 are adjacent to LVDS Ground plane). The distance between the matching resistance of the receiving end and the receiving pin should be as close as possible. At the same time, the accuracy of matching resistance must be controlled. For point-to-point topology, the impedance of the trace is usually controlled at 100Ω, but the matching resistance can be adjusted according to the actual situation. The degree of resistance is 1%-2%. Because according to experience, 10% impedance mismatch will produce 5% reflection.

2. Simulation analysis of serial LVDS signal

The above analyzes the matters that must be paid attention to when designing LVDS signals. Although the above rules are generally followed during PCB design, in order to improve the correctness and accuracy of the design, the complete signal simulation of the PCB must be carried out through simulation. Obtain the signal's crosstalk, delay, reflection and eye pattern waveforms, so as to achieve the goal of correct design. The simulation process of signal integrity problem is to first establish the simulation model of the components, and then perform the pre-simulation to determine the parameters and constraints of the wiring process. The physical realization stage is designed according to the constraints, and the post-simulation is performed to verify whether the design meets the design requirements. The nature of the model in the entire process directly affects the results of the simulation, and the simulation analysis methods used in the pre-simulation and post-simulation stages are also critical to the simulation results, and a higher degree of spice model is used in this design. The following is a combination of actual projects to illustrate the implementation process of simulation in this design.

2.1 PCB board stack setting

From the above analysis, it is known that the stacking setting of the PCB board is closely related to the coupling of the signal and the impedance calculation. Therefore, the stacking design must be carried out before the PCB board design, and then the impedance calculation of the signal.

2.2 Set DC voltage value

This step is mainly to specify the DC voltage value for certain specific networks (usually power ground, etc.), determine the DC voltage to be applied to the network, and perform EMI simulation requires determining one or more voltage source pins. These voltage values include The reference voltage information used by the model in the simulation process is described.

2.3 Device settings

During allegro simulation, allegro divides the devices into three categories: IC, connectors and discrete devices (resistance capacitors, etc.), allegro will assign simulation attributes to the pins of the device according to the device type, discrete devices and connector pins The attribute is UPSPEC, and the pin attribute of IC can be IN, OUT, BI, etc.

2.4 Model allocation

The main models used in the board-level high-speed PCB board simulation process are device models and transmission line models. The device model is generally provided by the device manufacturer. In the high-speed serial signal, what we adopt is the SPICE model with higher precision to carry on the simulation analysis. The transmission line model is formed through simulation software modeling. When the signal is being transmitted, the transmission line will make the signal integrity problem prominent, so the ability of the simulation software to model the transmission line directly affects the simulation result.

2.5 SI inspection

The SI Audit function is used to check whether a particular network or a group of networks can be extracted for analysis. Generally, it is to set the high-speed network that we need to pay attention to. This design mainly focuses on LVDS serial signals.

2.6 Extract network topology

Extract the topological structure of the signal of interest from the PCB board, generally including the driving end and the receiving end, as well as the transmission line and related matching resistors and capacitors. It can be seen from the topology that the network passes through those paths, which will cause the signal transmission Influence. This article only takes the network topology diagram of one of the signals as an example: as shown in Figure 4:

2.7 View waveform

After the above related steps are set up, the simulation can be carried out. Allegro can carry out signal reflection simulation and crosstalk simulation, and the differential line also needs to carry out eye diagram analysis. Of course, the simulation is also divided into pre-simulation and post-simulation. When using allegro to design the PCB board, it is necessary to modify the design in real time with the simulation results to meet the requirements. Because the simulation process is complicated and the steps are cumbersome, I will not describe them one by one. There are two points to pay attention to in the wiring of the differential pair. One is that the length of the two lines should be as long as possible, and the equal length is to ensure that the two differential signals are kept opposite at all times. Polarity to reduce common mode components. The other is that the distance between the two lines (this distance is determined by the differential impedance) must always be kept constant, that is, it must be kept parallel. There are two parallel ways, one is that the two wires run on the same side-by-side, and the other is that the two wires run on two adjacent layers above and below (over-under). Generally, the former has more side-by-side implementations. The equidistance is mainly to ensure the same differential impedance between the two and reduce reflection. The wiring method of the differential pair should be close and parallel appropriately. The so-called appropriate proximity is because this distance will affect the value of differential impedance, which is an important parameter for designing differential pairs. The need for parallelism is also to maintain the consistency of the differential impedance. If the two lines are suddenly far and near, the differential impedance will be inconsistent, which will affect the signal integrity and timing delay. From the simulated S-parameter graph, the differential impedance of the differential pair and the signal integrity can be analyzed. The key signal simulation waveforms in this design are given below for explanation. It can be seen from the simulation legend Figure 5 that the degradation index of S11 in the frequency domain of 0-3.0GHz is: below -16.770db, and S22 (pink curve) is not worse than -17db. This shows that the differential impedance of the differential pair is close to the design index, and the signal integrity is guaranteed.

3. Conclusion

Through the above simulation analysis, it can be known that the various requirements for high-speed LVDS signals can be met in the design stage of the PCB board, and the actual PCB board production has also proved the correctness of the design. The product runs stably and fully meets the PCI- Express requires high-speed data transmission and high reliability. From the analysis in this article, it can be seen that in the design of high-speed serial signals, not only the circuit design is considered, the board diagram design and simulation analysis are also equally important, and as the frequency of the signal becomes larger and larger, the delay and crosstalk of the signal are affected. Factors such as signal integrity and signal integrity are becoming more and more complex. At the same time, it is becoming more and more difficult to control the influence of these factors. Engineers must thoroughly analyze the wiring design, the models used, effective simulation and scientific analysis methods, in order to provide the correct guidance for the complex high-speed PCB board design and reduce the correction cycle to ensure The design is successful.