Based on recent PCB design trends, improving efficiency has become a key goal, and the trade-off of using slow switching devices for better EMI is not worthwhile. Super junctions can improve efficiency in applications where planar MOSFETs are difficult to handle. Compared with traditional planar MOSFET technology, super-junction MOSFET can significantly reduce on-resistance and parasitic capacitance. Although the significant reduction of on-resistance and the reduction of parasitic capacitance help to improve efficiency, it also produces rapid switching of voltage (dv/dt) and current (di/dt), resulting in high-frequency noise and radiated EMI.

To drive fast-switching super-junction MOSFETs, it is necessary to understand the impact of package and PCB design layout parasitics on switching performance, as well as the PCB design layout adjustments made to use super-junctions. Super-junction MOSFET with breakdown voltage of 500-600V is mainly used. Among these voltage ratings, the industry standards TO-220, TO-247, TO-3P, and TO-263 are the most widely used packages. The impact of packaging on performance is limited because the internal gate and source bonding wire lengths are fixed. Only the length of the lead can be changed to reduce the source inductance of the package.

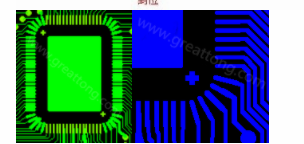

The typical lead inductance of 10nH does not seem large, but the di/dt of these MOSFETs can easily reach 500A/μs! Assuming that di/dt is 500A/μs, the voltage on the 10nH lead inductance is VIND=5V; and the turn-off di/dt of the 10nH lead inductance is 1,000A/μs, which can generate a voltage of VIND=10V. Most applications and designs have not considered that this additional inductance will also generate voltage, but this cannot be ignored. The above simple calculation shows that the total source inductance of the package, that is, the bond wire and pin inductance, must be reduced to an acceptable value. Another source of noise is layout parasitics. There are two visible layout parasitics: parasitic inductance and parasitic capacitance. The inductance of a 1cm trace is 6-10nH. This inductance can be reduced by adding a layer on the top of the PCB and a GND layer on the bottom of the PCB. The other type is parasitic capacitance.

The principle of capacitive parasitics in the layout. Parasitic capacitance is caused by two adjacent traces or between a trace and the ground plane on the other side. Another type of capacitance is the capacitance between the device and the ground plane. The two parallel running wires on both sides of the PCB board can increase capacitance and reduce loop inductance, thereby reducing electromagnetic noise radiation. Please consider these layout tips the next time your design requires super-junction MOSFETs.

Parasitic components in packaging and layout

Because MOSFET is a unipolar device, parasitic capacitance is the only limiting factor for switching transients. The principle of charge balance reduces the on-resistance of a specific area, and compared with standard MOSFET technology, the chip size under the same RDS (ON) is smaller. Figure 1 shows the capacitance of a super junction MOSFET and a standard planar MOSFET. The Coss of the standard MOSFET has a moderately linear relationship, while the Coss curve of the super-junction MOSFET presents a highly non-linear relationship. Because of the higher cell density, the initial value of Coss of the super-junction MOSFET is higher, but in the super-junction MOSFET, the Coss will drop rapidly near the drain-source voltage of about 50V. When super-junction MOSFETs are used in PFC or DC/DC converters, these nonlinear effects may cause voltage and current oscillations. Figure 3 shows a simplified schematic diagram of the PFC circuit, including the internal parasitic elements of the power MOSFET and an external oscillator circuit. The external oscillator circuit includes an external coupling capacitor (Cgd_ext.) brought by the layout.

Comparison of output capacitance between planar MOSFET and super junction MOSFET

Generally speaking, there are multiple oscillator circuits that will affect the switching characteristics of the MOSFET, including internal and external oscillator circuits. In the PFC circuit, L, Co and Dboost are the inductor, output capacitor and boost diode respectively. Cgs, Cgd_int and Cds are the parasitic capacitance of the power MOSFET. Ld1, Ls1, and Lg1 are the drain, source, and gate bonding wires and pin inductance of the power MOSFET. Rg_int and Rg_ext are the internal gate resistance of the power MOSFET and the external gate drive resistance of the circuit. Cgd_ext is the parasitic gate-drain capacitance of the circuit. LD, LS, and LG are the stray inductances of the drain, source, and gate traces of the printed circuit board (PCB). When the MOSFET is turned on or off, the gate parasitic oscillation occurs in the resonant circuit through the gate-drain capacitance Cgd and the gate lead inductance Lg1.

Under the resonance condition (ωL=1/ωC), the oscillating voltage generated in the gate and source voltage is much larger than the driving voltage. The voltage oscillation caused by the resonance change is proportional to the quality factor, Q (=ωL/R=1/ωCR). When the MOSFET is turned off, the drain parasitic inductance (LD+Ld1), the gate-drain capacitance Cgd and the gate lead inductance Lg1 network cause the gate oscillation voltage. If the gate resistance (RG-ext.+Rg_int.) is extremely small, Q becomes large. In addition, the voltage drop across LS and the source stray inductance of Ls1 generate oscillations in the gate-source voltage. Parasitic oscillation may cause gate-source breakdown, poor EMI, large switching losses, gate control failure, and may even cause MOSFET failure.

It is very important to optimize the circuit design to maximize the performance of the super-junction MOSFET without negative effects.