The solder joint spacing of WLP and WLCSP components is quite small. Different solder pad designs will also limit the trace width between solder joints. There are more restrictions when designing the PCB.

With the wafer-level chip size packaging of WLP and WLCSP, the effectiveness of miniaturized chips has become more and more significant, and the use of electronic products has also continued to increase. However, although WLP and WLCSP can reach the size of the chip after packaging Just like the excellent advantages of the same size and size of the die, the functions of the packaged products are becoming more and more complex, the number of pins and the design requirements are becoming more and more stringent, and the PCB design has become a new application challenge...

WLP (Wafer Level Packaging) and WLCSP (Wafer Level Chip Scale Package) are actually a packaging method of integrated circuits, which refers to directly on the wafer after the wafer (Wafer) production is completed. Packaging and testing procedures, when the packaging is completed, then cut into a single integrated circuit packaging manufacturing method.

The package design components made by conventional IC and WLP are very different in size, and WLP only needs the die size to have the same electrical characteristics.

WLP performs component packaging at the wafer stage, so there is no space requirement for conventional IC pins, package body filling, etc., and the component size can achieve the die size, so PCB design challenges are greater.

Nemotek uses WLP to make image sensor modules, with an optical lens design, which can greatly reduce the footprint of the image sensor module. The production can be made quickly with automatic feeding, which saves production costs.

Samsung adopts the image sensor produced in the form of WLP, directly using wafer-level packaging to greatly reduce the size of the component, the component can be extremely thin and the smallest footprint.

WLP and WLCSP are different from the integrated circuit manufacturing method in which the wafer is cut into dies, and then additional pins are wired in the package. Because of the smaller footprint of the package, WLP and WLCSP can achieve the same IC application functions, but As long as the footprint is the same as the size of the die after cutting, and in the process of making a single IC from WLP and WLCSP, there is no need to wire and fill glue like ordinary ICs. When developing miniaturized or ultra-small miniaturized design product solutions, IC applications with WLP and WLCSP packaging design methods can achieve excellent product miniaturization benefits. In addition, WLP and WLCSP components themselves have excellent electrical properties (because of the lack of wiring and pins), which are used for components for high-speed transmission applications. The efficiency is higher, because the components can be processed on the wafer, the cumbersome manufacturing process of IC is also reduced.

But here comes the problem. Although WLP and WLCSP are relatively small in size, with the increasing number of pins of conventional ICs, the ball pitch requirements for WLP and WLCSP packaging have become more stringent, but the electrical properties required for circuit design Basically, it is not different from the electrical support required by general ICs, but the size of WLP and WLCSP has been reduced to the die size. In addition, the contacts and circuits that can be connected to the PCB with WLP and WLCSP are extremely small. In the design of PCB The solution is not as easy as the general IC application solution.

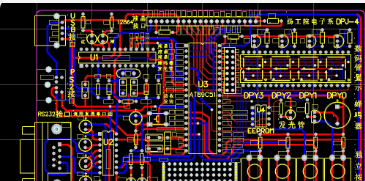

As for the use of wafer-level packaging, the purpose is to reduce the cost and overall size of the solution, but when the wafer-level packaging is introduced, the cost of the PCB is bound to be due to the use of wafer-level packaging, and corresponding wiring must be carried out. With the improvement of the punching process, the PCB characteristics can be fully matched with WLP and WLCSP components without connection problems. Especially after WLP and WLCSP are used in the design scheme, PCB will become more complicated and its role will become more important. Careful planning is required during the design to avoid the stability of the terminal product caused by the quality of the PCB.

Component packaging at the wafer stage greatly saves the footprint of the carrier board

Since WLP and WLCSP packaging are directly built on the "silicon" substrate packaging process, IC basically does not need to use bonding wires, for high-frequency components, it can directly obtain better high-frequency electrical properties, and achieve the benefit of shortening the cycle time. And because the packaging can be completed in the fab, and the packaging cost can be saved at the same time, but for the engineer, the design plan must also be considered in the direction of reducing costs. To match WLP and WLCSP components, the PCB cost must also be limited to a certain extent. Pay attention to the trade-off design, or adopt the corresponding circuit layout.

Generally speaking, to import WLP and WLCSP components, before executing PCB layout planning, engineers must first obtain the footprint of WLP and WLCSP (ie package size), and at the same time confirm the size/contact error and contact of WLP and WLCSP components For critical component information such as pitch, start circuit layout and process component placement, you can use the obtained component parameters to design and plan. As the size and contacts of WLP and WLCSP become smaller, you must also consider the soldering of the applicable IC pins. Mat design.

PCB needs to be fine-tuned for SMD and NSMD forms

It can be matched with WLP and WLCSP pad types, and Solder Mask Defined (SMD) and Nonsolder Mask Defined (NSMD) can be used. The solder mask definition type SMD solder pad is designed to use the solder mask to define the solder ball and the area of the solder pad to be soldered. This design solution can reduce the possibility that the solder pad may be pulled up during the soldering or desoldering process. But the disadvantage of the SMD form is that SMD reduces the surface area of the copper surface connected with the solder ball, and at the same time reduces the space between the adjacent pads, which will limit the width of the trace between the pads and may also cause the PCB to be turned on. The hole uses elasticity. In most design schemes, the more commonly used one is still the SMD design scheme, because the soldering pads of the SMD can have better solder connection characteristics, and the solder and the soldering pads can be integrated together during the manufacturing process.

As for the non-solder mask-defined solder pad (NSMD), the design method is to use copper for solder bump soldering to define the solder pad area. This design solution can provide a larger surface area to connect the PCB and the solder ball. At the same time, NSMD Compared with the SMD design form, it also provides a larger insulation distance between the soldering pads and the soldering pads, which allows a wider wiring spacing between the soldering pads, and has higher flexibility for the use of through holes of the PCB. However, if the NSMD is soldering, Desoldering and other operations can easily cause the solder pad to be pulled up.

Special consideration is required for spacing

The consideration of the pitch size is also very important, especially when the PCB is in the form of SMD or NSMD, the reserved pitch size of different solutions will also be slightly different, and the pitch size refers to the distance between the solder balls, which is two The distance between the center of the solder ball, and the larger the pitch size, the larger the wiring space between the solder pad and the solder pad that can be used for wiring.

In terms of PCB wiring, due to the characteristics of WLP and WLCSP components, the available solder ball pitch is quite small. Basically, it is impossible to use mechanical opening equipment to open PCB holes. Because the hole diameter of the mechanical opening is too large, the opening process may also make the PCB The upper thinner line is damaged due to errors in the opening process. However, in PCBs that use WLP and WLCSP components, because the circuits are much tighter, laser-drilled vias, which are more costly, will be used instead.

Concluding remarks

Wafer-level chip size packaging of WLP and WLCSP components has an excellent improvement benefit for reducing the size of the end product, but in exchange for the PCB design plan must also be upgraded simultaneously, with high-density multilayer boards and precision laser openings. During development, the carrier board space and component cost originally saved by IC components will be partly transferred to PCB design and subsequent mass production. Instead, smaller components are used to produce parts and components on the production line at the back of the product. Processing or maintenance will also cause some operational problems that are more difficult to implement, which must be considered one by one before relevant design.