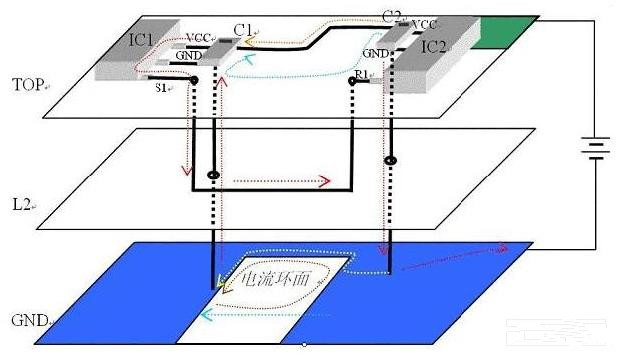

Regarding the signal return and cross-segmentation in high-speed PCB board, a "scenario" is simply constructed here, and the ground return, power return and some cross-segmentation issues are introduced in conjunction with the following figure. For the convenience of drawing, the layer spacing is enlarged.

IC1 is the signal output terminal, IC2 is the signal input terminal (to simplify the PCB board model, it is assumed that the receiving terminal contains a lower connection resistance). The third layer is the ground layer. Both IC1 and IC2 grounds come from the third ground plane. The upper right corner of the top layer is a power plane, which is connected to the positive pole of the power supply. C1 and C2 are the decoupling capacitors of IC1 and IC2, respectively. The power supply and ground pins of the chip shown in the figure are the power supply and ground of the transmitting and receiving signal terminals. At low frequency, if the S1 terminal outputs a high level, the entire current loop is that the power supply is connected to the VCC power plane through the wire, and then enters IC1 through the orange path, then exits from the S1 terminal, and enters IC2 through the R1 terminal along the second layer of wire. Then enter the GND layer and return to the negative pole of the power supply through the red path.

However, at high frequencies, the distribution characteristics presented by the PCB will have a great impact on the signal. The ground return we often say is a problem that is often encountered in high-frequency signals. When there is an increased current in the signal line from S1 to R1, the external magnetic field changes rapidly, which will induce a reverse current in the nearby conductor. If the ground plane of the third layer is a complete ground plane, there will be a current marked by a blue dotted line on the ground plane; if the TOP layer has a complete power plane, there will also be a current on the top layer along the blue Dotted reflow. At this time, the signal loop has a current loop, the energy radiated to the outside, and the ability to couple external signals. (The skin effect at high frequencies also radiates energy outward, and the principle is the same.)

Since the high-frequency signal level and current change rapidly, but the change period is short, the energy required is not very large, so the chip is powered by the decoupling capacitor close to the chip. When C1 is large enough and the response is fast enough (with very low ESR value, ceramic capacitors are usually used. The ESR of ceramic capacitors is much lower than that of tantalum capacitors.), the orange path on the top layer and the red path on the GND layer can be It is regarded as non-existent (there is a current corresponding to the power supply of the whole board, but not the current corresponding to the signal shown in the figure).

Therefore, according to the environment constructed in the figure, the entire path of the current is: from the positive pole of C1 -> VCC of IC1 -> S1 -> L2 signal line -> R1 -> GND of IC2 -> via hole -> $ of the GND layer Path -> Via -> Capacitor Negative. It can be seen that there is a brown equivalent current in the vertical direction of the current, and a magnetic field will be induced in the middle. At the same time, this torus can also be easily coupled to external interference. If the signal in the figure is a clock signal, there is a group of 8-bit data lines in parallel, powered by the same power supply of the same chip, and the current return path is the same. If the data lines are flipped in the same direction at the same time, a large reverse current will be induced on the clock. If the clock lines are not well matched, this crosstalk is enough to have a fatal impact on the clock signal. The strength of this crosstalk is not proportional to the level of the interference source, but is proportional to the current change rate of the interference source. For a purely resistive load, the crosstalk current is proportional to dI/dt=dV /( T10%-90%*R). In the formula, dI/dt (current rate of change), dV (swing of the interference source) and R (interference source load) all refer to the parameters of the interference source (if it is a capacitive load, dI/dt is related to T10%- The square of 90% is inversely proportional.). It can be seen from the formula that the crosstalk of low-speed signals is not necessarily smaller than that of high-speed signals. That is what we said: the 1kHZ signal is not necessarily a low-speed signal, and the edge situation should be comprehensively considered. For a signal with a very steep edge, it contains many harmonic components and has a large amplitude at each frequency multiplication point. Therefore, you should also pay attention when selecting devices. Do not blindly choose chips with fast switching speeds, which will not only cost high, but also increase crosstalk and EMC problems.

Any adjacent power plane or other plane with suitable capacitors across the signal to provide a low reactance path to GND can act as a return plane for that signal. In ordinary applications, the corresponding chip IO power supplies for transceivers are often the same, and there are generally 0.01-0.1uF decoupling capacitors between the respective power supplies and the ground, and these capacitors are also at both ends of the signal, so the The return flow effect of the power plane is second only to the ground plane. When using other power planes for return flow, there is often no low-reactance path to ground at both ends of the signal. In this way, the current induced in the adjacent plane will find the nearest capacitance back to ground. If the "near capacitor" is far away from the start or end, the return flow has to go through a "long journey" to form a complete return path, and this path is also the return path of the adjacent signal. This same return flow The effect of channel and common ground interference is the same, which is equivalent to crosstalk between signals.

For some unavoidable cross-power splitting situations, a high-pass filter (such as a 10-ohm resistor series 680p capacitor) can be connected across a capacitor or a RC series connection at the cross-segmented place. The specific value depends on your own signal type, that is To provide a high-frequency return path, but also to isolate low-frequency crosstalk between the mutual planes). This might involve adding capacitors between the power planes, which seems a bit comical, but certainly works. If it is not allowed by some specifications, the capacitors can be led to the ground on the two planes at the split. For the case of borrowing other planes for return, a few small capacitors can be appropriately added to the ground at both ends of the signal to provide a return path. But this approach is often difficult to achieve. Because most of the surface space near the terminal is occupied by the matching resistor and the decoupling capacitor of the chip on PCB board.