High-Speed PCB board Interconnect design technology includes testing, simulation, and various related standards, where testing is a method and means to verify the results of various simulation analyses. The most important test methods and means are the necessary conditions to ensure the analysis of interconnection design. For traditional signal waveform testing, the main concern is the length of the probe leads to avoid unnecessary noise introduced by Pigtail. This paper mainly discusses the new application and development of interconnect test technology. In recent years, with the continuous improvement of the signal rate, the test object has undergone significant changes. It is no longer limited to the traditional use of oscilloscopes to test signal waveforms. Power supply ground noise, synchronous switching noise (SSN), and jitter (Jitter) have gradually become The focus of interconnect design engineers, some instruments in the RF field have been applied to interconnect design. The test instruments commonly used in interconnect design include spectrum analyzers, network analyzers, oscilloscopes, and the various probes and fixtures used by these instruments, which have changed significantly to accommodate the ever-increasing signal rates. Using these test instruments as tools, this paper mainly introduces the development of interconnect design test technology in recent years from the following aspects:

1) The calibration method of the test

2) Modeling method of passive devices

3) Power Integrity Test

4) Test method of clock signal jitter

Among the three commonly used test instruments, the calibration method of the network analyzer is rigorous, followed by the spectrum analyzer, and the calibration method of the oscilloscope is simple. Therefore, we mainly discuss the calibration method of the network analyzer here. There are three commonly used calibration methods for network analyzers, Thru, TRL, and SOLT. The essence of Thru is normalization. During calibration, the network analyzer records the test result of the fixture (S21_C). In the actual test, directly divide the test result (S21_M) and S21_C to obtain the test result of the DUT (S21_A). . Thru calibration ignores reflections caused by mismatches in the test fixture as well as an electromagnetic coupling in space, therefore, its calibration accuracy. This calibration method can be used when only S21 is tested and the test accuracy is not required. In non-Coaxial structures such as PCB boards, it is sometimes necessary to test the characteristics of traces, vias, connectors, etc. In this case, the test instrument supplier does not provide standard calibration parts, and it is difficult for testers to make a good open circuit, short circuits, matching load, and other calibration parts at the test calibration port, so traditional SOLT calibration cannot be done. The advantage of calibrating with TRL is that standard calibration pieces are not required and the test calibration port can be extended to the desired location. At present, TRL calibration has been widely used in PCB board structure testing. SOLT is generally regarded as a standard calibration method. There are a total of 12 calibration error parameters in the calibration model, and various errors are calibrated and calculated by using a short circuit, open circuit, load, and through. Since test instrument suppliers usually only provide Coaxial calibration parts, the SOLT calibration method cannot be used in non-Coaxial structures. The above three calibration methods can all be analyzed in detail by means of the signal flow graph, in which each error parameter has corresponding parameters in the signal flow graph. Through the signal flow diagram, the error sensitivity of various calibration methods can be clearly understood, so as to understand the error range of the actual test. A point to make here is that even the standard SOLT calibration method ignores five error parameters in the calibration model. Typically, these five error parameters do not affect calibration accuracy. However, if you do not pay attention to the design of the calibration fixture during use, there will be a phenomenon that cannot be calibrated. The spectrum analyzer provides a standard source for calibration. During calibration, you only need to connect the internal standard source to the input port through a test fixture. The calibration takes about 10 minutes. The calibration of the oscilloscope is even simpler. Connect the probe to the internal standard source and confirm it. The calibration takes about 1 minute.

Testing and Modeling of Passive Devices

With the continuous increase of the signal rate, the role of passive devices in the signal chain is becoming more and more important. The accuracy of system performance simulation analysis often depends on the model accuracy of passive devices. As a result, the testing and modeling of passive components have gradually become an important part of the interconnect design of various equipment suppliers. Commonly used passive devices are as follows:

1) Connector

2) PCB board traces and vias

3) Capacitor

4) Inductance (magnetic beads)

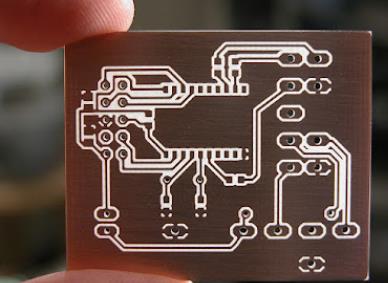

In high-speed signal integrity designs, the impact of connectors on the signal link. For frequently used high-speed connectors, the usual practice is to make a calibration fixture according to the TRL calibration method, and test and model the connector for simulation analysis. The test modeling method of PCB traces and vias is similar to that of connectors. TRL calibration is also used to move the test port to the desired position, and then the test modeling is performed.

Power supply impedance characteristic table of a single board

Capacitance models have applications in signal integrity analysis, and more importantly in power integrity analysis. The commonly used capacitance modeling instruments in the industry are impedance analyzers and network analyzers, which are suitable for different frequency bands respectively. Impedance analyzers are suitable for low-frequency bands, and network analyzers are suitable for high-frequency bands. If a network analyzer is used for power integrity testing in the actual test, it is recommended to use the network analyzer in the entire frequency band of capacitance modeling to ensure the consistency of modeling and application. Due to the low impedance of capacitors, paralleling is often used when modeling with a network analyzer. The problem that has not been solved in capacitance modeling in the industry at present is how to eliminate the mutual coupling between the fixture and the capacitance, so as to reduce the influence of the fixture on the modeling results. In traditional power supply design, inductors (magnetic beads) are often used to isolate the power supply to reduce noise interference. In the actual design, the isolation inductance (magnetic bead) is often removed, and the noise of the power supply is reduced instead. This is due to the resonance of the inductor (magnetic bead) with other filter components. To avoid this, it is necessary to model and simulate the inductance (magnetic bead) to avoid resonance. The commonly used inductance (magnetic bead) modeling method in the industry also uses a network analyzer. The specific method is similar to that of capacitance modeling. The difference is that the inductance (magnetic bead) modeling method is in series mode, and the capacitance modeling method is in parallel mode. The modeling of the above passive devices is mainly used in signal integrity and power integrity. In recent years, the simulation analysis of EMI is gradually developing, and the test modeling of EMI passive devices has gradually become the focus of interconnect design. . Figure 1 shows the impedance curve of the capacitor.

Power Integrity Testing

With the continuous increase of chip power and the continuous reduction of operating voltage, the noise of the power supply has gradually become the object of concern in interconnection design. From the perspective of the test object, the power integrity test can be divided into two steps, the power system characteristic test and the power ground noise test. The former is a test of the performance of the power supply part of the system (passive test), the latter is a direct test of the power supply ground noise (active test) when the system is working, and the synchronous switching noise can also be classified as power supply ground noise. When testing the performance of the power system, a network analyzer is usually used, and the test object is the Self-Impedance and Transfer-Impedance of the power system. Under normal circumstances, the impedance of the power system is much smaller than the impedance of the network analyzer system (50 ohms), so it is only necessary to do the pass-through calibration during the test, and the impedance of the power system can be obtained by using the formula S21=Z/25. A spectrum analyzer and an oscilloscope can be used to test the ground noise of the power supply. The input port of the spectrum analyzer cannot connect to the DC component. Therefore, when testing the ground noise of the power supply, DC-Blocking must be connected in series in the test fixture. The input impedance of the spectrum analyzer is 50 ohms, and the impedance of the power-ground network is generally at the milliohm level, so the test fixture will not affect the system under test. The methods described above are to test the power supply ground noise on the single board, and the power supply ground noise in the chip is what really affects the operation of the chip. At this time, it is necessary to use the synchronous switching noise test to determine the power supply ground noise in the chip. Suppose the chip has N IO ports, one of them is kept static, and the other N-1 is turned over at the same time, and the signal waveform on the static network is tested, that is, the synchronous switching noise. Synchronous switching noise includes both power supply ground noise and crosstalk between different signals in the package. There is currently no way to completely distinguish the two.

Oscilloscope input impedance changes with settings

In some high-end products, jitter has gradually become an important indicator that affects product performance. Here we only briefly introduce how to use a spectrum analyzer to test clock signal jitter and troubleshoot problems. The jitter test of data signals is not covered for the time being. In most systems, the clock is generated by a crystal oscillator or a phase-locked loop. The jitter test of the clock signal is relatively simple and does not require high-end test instruments. The problem can be located by using a common spectrum analyzer. The spectrum of an ideal clock signal is a clean discrete spectrum with components only at multiples of the clock frequency. If there is a jitter in the clock signal, side lobes will appear in the vicinity of these multipliers, and the jitter size is proportional to the power of these side lobes. The specific method of using a spectrum analyzer to test clock jitter is to find any testable point on the clock signal chain, connect the signal at this point to the spectrum analyzer through DC-Blocking, and observe the test results. Since the test fixture is a linear system, there is no need to worry about generating new spectral components. As mentioned above, the clocks are all generated by crystal oscillators or phase-locked loops. In this case, an important reason for introducing clock jitter is the power supply noise of crystal oscillators or phase-locked loops. Using the method described above to test the power supply noise of the crystal oscillator or phase-locked loop obtained, and compare it with the side lobes in the clock spectrum, the cause of the clock jitter can basically be determined. The solution to the problem is to redesign the filter circuit of the crystal oscillator of the phase-locked loop according to the side lobes of the clock spectrum. In general, these problems can be solved by selecting the filter capacitor reasonably.

This paper briefly introduces the current test objects and test methods in the field of interconnect design. As signal rates continue to increase, new test content is emerging, including power-to-ground noise, passive device modeling, jitter, and more. The author proposes a test method for these new test contents based on his own work experience. In the traditional signal waveform test, the main consideration should be to reduce the length of the ground wire to avoid pigtail coupling into noise and reduce the test accuracy. In the future interconnect design, due to the increase in signal operating frequency, the focus of work will shift to chip packaging, and related testing and modeling techniques will become the focus of work on PCB board.