Common sense of high frequency PCB wiring (4)

1. From which aspects should the circuit board DEBUG start?

As far as digital circuits are concerned, the first step is to determine three tasks in sequence: 1. Acknowledge that all power values have reached the planning requirements. Some systems with multiple power supplies may require certain standards for the order and speed of the power supplies. 2. Acknowledge that all clock signal frequencies are operating normally and there are no non-monotonic problems on the edges of the signal. 3. Acknowledge whether the reset signal meets the standard requirements. If these are normal, the chip should announce the first cycle (cycle) signal. Next, debug according to the operating principle of the system and the bus protocol.

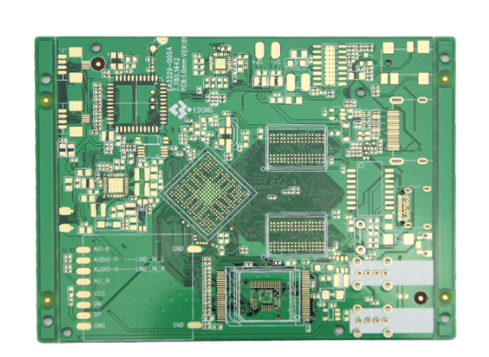

2. When the size of the circuit board is fixed, if the planning needs to accommodate more functions, it is often necessary to increase the PCB trace density, but this may cause the interference of the traces to increase, and the traces will also increase the impedance. Can't drop, please experts introduce the skills in high-speed (>100MHz) high-density PCB planning?

When planning high-speed and high-density PCBs, crosstalk (crosstalk interference) really needs special attention, because it has a great impact on timing and signal integrity. Here are a few places to pay attention to:

Control the connection and matching of the characteristic impedance of the trace.

The size of the trace interval. It is generally seen that the interval is twice the line width. It is possible to know the influence of trace spacing on timing and signal integrity through simulation, and find the minimum tolerable spacing. The result of different chip signals may be different.

Choose the appropriate termination method.

Prevent the wiring directions of two adjacent layers from being the same, even if there are wirings stacked up and down, because this kind of crosstalk is larger than that of adjacent wiring on the same layer.

Use blind/buried vias to increase the trace area. However, the production cost of the PCB board will increase. It is indeed difficult to achieve complete parallelism and equal length in practice, but it is still necessary to do as much as possible.

In addition, differential termination and common mode termination can be reserved to smooth the impact on timing and signal integrity.

3. An LC circuit is often used to imitate the filtering at the power supply. But why is the filtering effect of LC worse than RC sometimes?

To compare the filtering effects of LC and RC, it is necessary to consider whether the selection of the frequency band to be filtered and the inductance value is appropriate. Because the inductance (reactance) of the inductor is related to the inductance value and frequency. If the noise frequency of the power supply is low and the inductance value is not large enough, the filtering effect may not be as good as RC. However, the value to be paid for using RC filtering is that the resistor itself consumes energy and has poor efficiency, and pay attention to the power that the selected resistor can accept.

4. What is the method of selecting inductor and capacitance value for filtering?

In addition to the noise frequency that you want to filter out, the selection of the inductance value should also consider the ability of the instantaneous current to respond. If the output terminal of LC has the opportunity to output a large current instantaneously, a too large inductance value will prevent the large current from flowing through the inductor and add ripple noise. The capacitance value is related to the size of the standard value of ripple noise that can be tolerated. The smaller the ripple noise value requirement, the larger the capacitance value. The ESR/ESL of the capacitor will also have an impact. In addition, if the LC is placed at the output of a switching regulation power, pay attention to the stability of the pole/zero generated by the LC to the loop stability of the negative feedback control (negative feedback control). Influence.

5. How to reach EMC requirements as much as possible without causing too much capital pressure?

The cost added to the PCB due to EMC is generally due to the addition of the number of ground layers to enhance the shielding effect and the addition of ferrite bead, choke and other high-frequency harmonic devices to suppress high-frequency harmonics. In addition, it is generally necessary to deploy the shielding structure of other organizations to make the entire system pass the EMC requirements. The following only provides a few of the electromagnetic radiation effects generated by the circuit to reduce the PCB board planning skills.

Try to use devices with a slower signal slew rate to reduce the high frequency components generated by the signal. Pay attention to the location of the high-frequency equipment, and do not get too close to the external connector.

Pay attention to the impedance matching of high-speed signals, the wiring layer and its return current path to reduce high-frequency reflection and radiation.

Place adequate decoupling capacitors on the power pins of each device to smooth the noise on the power layer and ground layer. Pay special attention to whether the frequency response and temperature characteristics of the capacitor meet the planning requirements.

The ground adjacent to the external connector can be properly cut with the ground, and the ground of the connector should be connected to the chassis ground nearby.

You can properly use ground guard/shunt traces next to some particularly high-speed signals. But pay attention to the influence of guard/shunt traces on the characteristic impedance of the trace. The power layer shrinks 20H from the ground layer, and H is the distance between the power layer and the ground layer.

6. When there are multiple digital/analog function blocks in a PCB board, the usual practice is to separate the digital/analog grounds. What are the reasons?

The reason for separating the digital/analog ground is because the digital circuit generates noise on the power supply and ground when the bump potential is switched. The size of the noise is related to the speed of the signal and the size of the current. If the ground plane is not cut and the noise generated by the digital area circuit is large and the circuit in the imitated area is very close, even if the digital-to-analog signal is not interspersed, the imitated signal will still be disturbed by the ground noise. That is to say, the method of not cutting the digital-to-analog ground can only be used when the analog circuit area is far from the digital circuit area where large noise is generated.

7. Another approach is to ensure that the digital/analog separation layout and the digital/analog signal lines are not interspersed with each other, the entire PCB board ground is not cut, and the digital/analog ground is connected to this ground plane. The truth is there?

The requirement that the digital-analog signal traces cannot be interspersed is because the return current path of the faster digital signal will flow back to the source of the digital signal along the adjacent ground below the trace. If the digital-analog signal traces, Interspersed, the noise generated by the return current will appear in the area of the imitating circuit.

8. How to consider impedance matching when planning high-speed PCB schematic diagrams?

When planning high-speed PCB circuits, impedance matching is one of the elements of planning. The impedance value is definitely related to the routing method, such as walking on the surface layer (microstrip) or inner layer (stripline/double stripline), the distance between the reference layer (power layer or ground layer), the width of the trace, the PCB material, etc. Both will affect the characteristic impedance value of the trace. In other words, the impedance value must be determined after wiring. Generally, simulation software cannot take into account some wiring conditions where the impedance is not connected due to the accuracy of the circuit model or the mathematical algorithm used. At this time, only some terminators (termination), such as series resistance, can be reserved on the schematic diagram. To smooth out the effect of discontinuous trace impedance. The real way to deal with the problem is to try to prevent the occurrence of discontinuous impedance when wiring.

9. Where can I provide a more accurate IBIS model library?

The accuracy of the IBIS model directly affects the results of the simulation. Basically, IBIS can be regarded as the electrical characteristic data of the equivalent circuit of the actual chip I/O buffer, which can generally be obtained from the SPICE model conversion (measurement can also be selected, but most of them), and the SPICE data and chip production are positive Therefore, the SPICE data of the same equipment provided by different chip manufacturers is different, and the data in the transformed IBIS model will also vary accordingly. In other words, if the equipment of manufacturer A is used, as long as they have the ability to provide accurate model data for their equipment, because no one else knows better than them what kind of process their equipment is made. If the IBIS provided by the manufacturer is not accurate, the only way to deal with it is to continuously ask the manufacturer to improve.

10. When planning high-speed PCBs, which aspects should planners consider EMC and EMI regulations?

Generally, EMI/EMC planning needs to consider both radiated and conducted aspects. The former belongs to the higher frequency part (>30MHz) and the latter is the lower frequency part (<30MHz). So it cannot Only pay attention to the high frequency and ignore the low frequency. A good EMI/EMC plan must take into account the orientation of the equipment, the organization of the PCB stack, the way of important connections, the selection of equipment, etc., if these Without a better organization beforehand, the post-processing will outweigh the gains and increase the cost.

For example, the position of the clock generator should not be close to the external connector. High-speed signals should go to the inner layer as much as possible. Pay attention to the characteristic impedance matching and the connection of the reference layer to reduce reflections. The slew rate of the signal pushed by the equipment should be as small as possible to reduce the height. Frequency components, when choosing a decoupling/bypass capacitor, pay attention to whether its frequency response meets the requirements to reduce the noise of the power plane.

In addition, pay attention to the return path of the high-frequency signal current to make the loop area as small as possible (that is, the loop impedance as small as possible) to reduce radiation. You can also use the method of cutting the ground to control the scale of high-frequency noise. Finally, appropriate Select the chassis ground between the PCB board and the housing.