1. The basic concept of PCB reflow

In the schematic diagram of the PCB digital circuit, the propagation of digital signals is from one logic gate to another. The signal is sent from the output end to the receiving end through a wire. It seems to flow in one direction. Many digital engineers think that the circuit path It is irrelevant. After all, the driver and receiver are designated as voltage-mode devices, so why bother to consider current.

In fact, the basic circuit theory tells us that the signal is propagated by electric current. Specifically, it is the movement of electrons. One of the characteristics of electron flow is that electrons never stay anywhere. No matter where the current flows, they must come back. Therefore, Current always flows in the loop, and any signal in the circuit exists in the form of a closed loop. For high-frequency signal transmission, it is actually a process of charging the dielectric capacitor sandwiched between the transmission line and the DC layer.

2. The influence of PCB reflow

Digital circuits usually rely on ground and power planes to complete reflow. The return paths of high-frequency signals and low-frequency signals are different. For low-frequency signal return, select the path with the lowest impedance, and for high-frequency signal return the path with the lowest inductance.

When the current starts from the signal driver, flows through the signal line and injected into the signal receiving end, there is always a return current in the opposite direction: starting from the ground pin of the load, passing through the copper plane, flowing to the signal source, and flowing through The current on the signal line forms a closed loop. The noise frequency caused by the current flowing through the copper-clad plane is equivalent to the signal frequency. The higher the signal frequency, the higher the noise frequency. The logic gate does not respond to the absolute input signal, but responds to the difference between the input signal and the reference pin. The single-point termination circuit reacts to the difference between the incoming signal and its logical ground reference plane, so the disturbance on the ground reference plane and the interference on the signal path are equally important.

The logic gate responds to the input pin and the designated reference pin, and we don’t know which one is the designated reference pin (for TTL, it is usually a negative power supply, for ECL it is usually a positive power supply, but not all of them), In terms of this property, the anti-interference ability of the differential signal can have a good effect on ground bounce noise and power plane sliding.

When many digital signals on the PCB board are switched synchronously (such as CPU data bus, address bus, etc.), this causes transient load currents to flow from the power supply into the circuit or from the circuit to the ground wire, due to the existence of the power wire and the ground wire Impedance will produce synchronous switching noise (SSN), and ground plane bounce noise (referred to as ground bounce) will also appear on the ground line. And when the surrounding area of the power line and grounding line on the printed board is larger, their radiation energy is also greater. Therefore, we analyze the switching state of the digital chip and take measures to control the return mode to reduce the surrounding area. Area, the purpose of the least radiation.

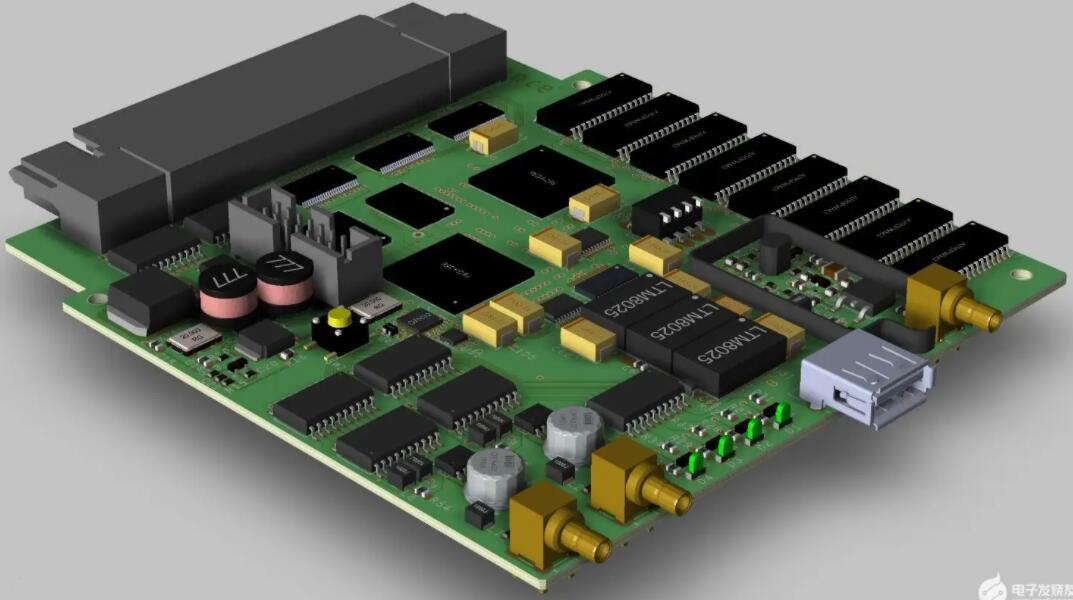

IC1 is the signal output terminal, IC2 is the signal input terminal (in order to simplify the PCB model, it is assumed that the receiving terminal contains a downstream resistor), and the third layer is the ground layer. The grounds of IC1 and IC2 are both from the third ground plane. The upper right corner of the TOP layer is a power plane, which is connected to the positive pole of the power supply. C1 and C2 are the decoupling capacitors of IC1 and IC2 respectively. The power supply and ground pin of the chip shown in the figure are the power supply and ground of the signal sending and receiving ends.

At low frequencies, if the S1 terminal outputs a high level, the entire current loop is that the power supply is connected to the VCC power plane through a wire, and then enters IC1 through the orange path, then comes out from the S1 terminal, and enters IC2 through the second layer of the wire through the R1 terminal. Then enter the GND layer and return to the negative pole of the power supply via the red path.

At high frequencies, the distribution characteristics of the PCB will have a great impact on the PCB signal. The ground return we often talk about is a problem often encountered in high-frequency signals. When there is an increased current in the signal line from S1 to R1, the external magnetic field changes rapidly, which will induce a reverse current in the nearby conductors. If the ground plane of the third layer is a complete ground plane, then A current indicated by the blue dashed line will be generated on the ground plane. If the TOP layer has a complete power plane, there will also be a return flow along the blue dashed line on the TOP layer. At this time, the signal loop has the smallest current loop, the energy radiated to the outside is the smallest, and the ability to couple external signals is also the smallest. (The skin effect at high frequency is also the smallest outward radiation energy, the principle is the same)

Since the PCB high-frequency signal level and current change rapidly, but the change period is short, the energy required is not very large, so the chip is powered by the decoupling capacitor closest to the chip. When C1 is large enough and the response is fast enough (it has a very low ESR value, ceramic capacitors are usually used. The ESR of ceramic capacitors is much lower than that of tantalum capacitors.), the orange path on the top layer and the red path on the GND layer can be Seen as non-existent.

Therefore, in the constructed environment, the entire path of the PCB current is: from the positive pole of C1 - the VCC of IC1 - the signal line of S1 - L2 - R1 - the GND of IC2 - the yellow path of the GND layer - the via - the ne gative electrode of the capacitor. It can be seen that there is a brown equivalent current in the vertical direction of the PCBcurrent, and a magnetic field is induced in the middle. At the same time, this torus can easily couple to external interference. If the signal is a clock signal as in the figure, there is a set of 8bit data lines in parallel, powered by the same power supply of the same PCB, and the current return path is the same. If the data line level flips in the same direction at the same time, a large reverse current will be induced on the clock. If the clock line is not well matched, this crosstalk is enough to have a fatal effect on the clock signal. The intensity of this kind of crosstalk is not proportional to the absolute value of the high and low levels of the interference source, but is proportional to the current change rate of the interference source.